- •Раздел 1. Микропроцессорные системы управления.

- •Раздел 2. Микроконтроллерные системы управления.

- •Раздел 3. Вопросы эксплуатации микропроцессорных устройств.

- •1. Микропроцессорные системы управления

- •1.1. Принципы построения и основы работы

- •Вопросы и задания

- •1.2. Элементная база мпсу

- •Вопросы и задания

- •1.3. Оперативные запоминающие устройства.

- •Вопросы и задания

- •1.4. Постоянные запоминающие устройства.

- •Вопросы и задания

- •1.5. Архитектура микропроцессора типа кр580вм80

- •Вопросы и задания

- •1.6. Типы машинных циклов и слово состояния

- •Вопросы и задания

- •1.7. Командные циклы чтения/записи

- •Вопросы и задания

- •1.8. Командный цикл подтверждения прерывания.

- •1.9. Принципиальные электрические схемы

- •Вопросы и задания

- •1.10. Интерфейс мпсу с изолированной системой шин

- •Вопросы и задания

- •1.11. Интерфейс мпсу с общей системой шин

- •1.12. Организация обслуживания запросов прерывания

- •Вопросы и задания

- •1.13. Программируемый контроллер

- •Вопросы и задания

- •1.14. Программируемый контроллер прерываний

- •Вопросы и задания

- •1.15. Программируемый интервальный таймер

- •Вопросы и задания

- •1.16. Мпсу с вводом-выводом аналоговой информации

- •Вопросы и задания

- •1.17. Выходные каскады мпсу

- •Вопросы и задания

- •2. Микроконтроллерные системы управления

- •2.1. Архитектура микроконтроллера к1816ве51

- •Вопросы и задания

- •2.2. Принципиальная электрическая схема порта

- •2.3. Схемы подключения внешней памяти к мк51

- •Вопросы и задания

- •2.4. Интерфейс мк51 с большим числом

- •Вопросы и задания

- •2.5. Таймер/счетчики мк51.

- •Вопросы и задания

- •2.6. Система прерываний мк51. Использование прерываний в программах

- •Вопросы и задания

- •2.7. Основы организации

- •Допустимые различия скорости приемо-передачи

- •2.8. Организация мультиконтроллерных систем

- •Программы инициализации станции и абонентов

- •Программы станции и абонента в сеансе "станция→абонент"

- •2.9. Микроконтроллерная система управления

- •3. Вопросы эксплуатации микропроцессорных устройств

- •3.1. Отладка аппаратных средств мпсу

- •Вопросы и задания

- •3.2. Отладка программного обеспечения мпсу

- •Вопросы и задания

- •3.3. Методы обеспечения помехоустойчивости мпсу

- •Вопросы и задания

- •1. Группа команд пересылок

- •2. Группа команд инкремента-декремента

- •3. Группа арифметических команд

- •4. Группа логических команд

- •5. Группа команд сдвига

- •6. Группа команд передачи управления

- •7. Группа команд работы со стеком

- •8. Группа команд ввода-вывода и управления микропроцессором

- •1. Группа команд пересылок

- •2. Группа команд арифметических операций

- •3. Группа команд логических операций

- •4. Группа команд операций с битами

- •5. Группа команд передачи управления

- •Дворак Николай Маркович микропроцессорные устройства

- •В высших учебных заведениях 3-4 уровней

- •98309, Г. Керчь, ул. Орджоникидзе, 82

- •98309, Г. Керчь, ул. Орджоникидзе, 82

Вопросы и задания

1. Поясните диаграммы сигналов и структурную схему при выполнении 1-го цикла М1.

2. Поясните диаграммы сигналов и структурную схему при выполнении команды чтения памяти.

3. Поясните диаграммы сигналов и структурную схему при выполнении команды записи в память.

4. Поясните диаграммы сигналов и структурную схему при выполнении команды чтения внешнего устройства.

5. Поясните диаграммы сигналов и структурную схему при выполнении команды записи во внешнее устройство.

6.

В каких случаях формируется управляющий

сигнал

![]() ?

?

7.

В каких случаях формируется управляющий

сигнал

![]() ?

?

8.

В каких случаях формируется управляющий

сигнал

![]() ?

?

9.

В каких случаях формируется управляющий

сигнал

![]() ?

?

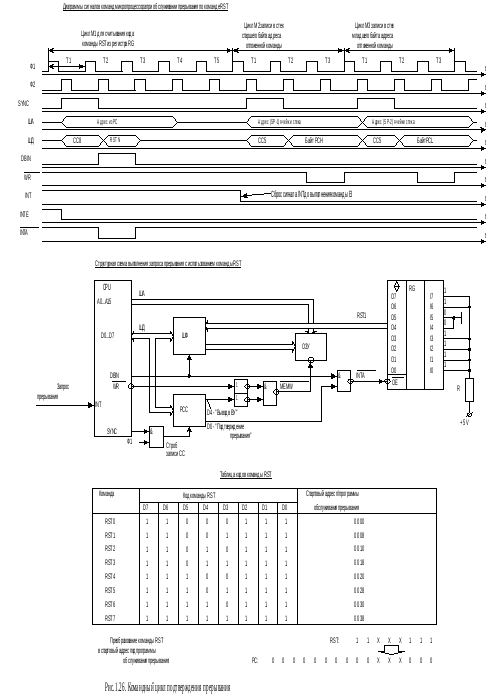

1.8. Командный цикл подтверждения прерывания.

Выполнение команды RST

В МП имеется возможность прервать выполнение текущей программы и перейти к выполнению более срочной, важной программы, которая называется подпрограммой обслуживания прерывания. При этом последняя команда текущей программы выполняется до конца, следующая за ней команда не выполняется, а переводится в ранг отложенной команды. Адрес отложенной команды сохраняется в стеке. После завершения выполнения подпрограммы, МП возвращается к выполнению отложенной команды.

Стеком называется область ОЗУ, информация в которую записывается и считывается упрощенным способом по правилу – "первый вошел, последним вышел". По этому правилу обмен информацией с ОЗУ ускоряется в несколько раз, но исключается произвольный доступ к ячейкам стека. На рис.1.25 показано заполнение стека и считывание из него информации на примере четырех байт данных:

|

Адреса ячеек ОЗУ |

Порядок записи данных в ячейки ОЗУ (стека) |

Порядок считывания данных из ячеек ОЗУ (стека) |

|

SP |

Начальный адрес – "вершина стека" |

|

|

SP-1 |

1-й сохраненный в стеке байт |

4-й считанный из стека байт |

|

SP-2 |

2-й сохраненный в стеке байт |

3-й считанный из стека байт |

|

SP-3 |

3-й сохраненный в стеке байт |

2-й считанный из стека байт |

|

SP-4 |

4-й сохраненный в стеке байт |

1-й считанный из стека байт |

|

Рис.1.25. Порядок записи в стек и считывания из стека |

||

В начале программы МПСУ в указатель стека SP с помощью команды LXI SP загружается адрес 1-й ячейки стека. Начальный адрес называется "вершиной стека".

Запись 1-го байта в стек сопровождается предварительным декрементом значения SP указателя стека и по адресу SP-1 сохраняется 1-й байт.

Запись 2-го и всех последующих байт сопровождается предварительным декрементом значения SP. Адреса стека уменьшаются относительно его вершины.

Чтение из стека производится в порядке, обратном заполнению стека, а именно, 1-м считывается байт записанный последним, 2-м считывается байт записанный предпоследним и т.д. После считывания каждого байта производится инкремент указателя стека. Адреса стека приближаются к его вершине.

Хотя есть команды PUSH и POP записи и чтения стека, заполнение стека происходит также автоматически при обработке запросов прерывания и вызове подпрограмм командой CALL, а считывание стека - при возврате из подпрограмм по команде RET.

На рис.1.26 приведена структурная схема и диаграммы сигналов командного цикла подтверждения прерывания с использованием команды прерывания RST. Диаграмма сигналов имеет существенные отличия от диаграмм простого выполнения команд, приведенных на рис.1.20.

Командный цикл подтверждения прерывания выполняется после обнаружения сигнала уровня 1 на ножке INT запроса прерывания. Текущая команда, при выполнении которой был обнаружен сигнал INT=1, доводится до конца и если программно разрешены прерывания (должна быть выполнена ранее команда EI), то запускается командный цикл подтверждения прерывания:

1). В такте Т1 цикла М1 по фронту синхросигнала Ф2:

- сбрасывается в 0 сигнал INTE (РАЗРЕШЕНИЕ ПРЕРЫВАНИЯ), который для внешних устройств является указанием того, что МП далее не реагирует на запросы прерываний;

- устанавливается сигнал SYNC=1;

- на ША выводится содержимое счетчика команд РС, которое далее в цикле М1 никак не используется;

- на ШД выводится слово состояния СС8 "Подтверждение прерывания" (табл.6.2), в котором установлены в 1 биты D5, D1 и D0.

2). В такте Т2 цикла М1 в течение времени действия синхроимпульса Ф1 происходит перепись СС8 в регистр РСС.

3).

В такте Т2 цикла М1 по фронту синхросигнала

Ф2 устанавливается DBIN=1 и через логический

элемент 2И-НЕ формируется сигнал

![]() =0.

=0.

Сигнал

![]() "Обслуживания прерывания" является

сигналом шины управления МПСУ (рис.1.4).

Сигналом

"Обслуживания прерывания" является

сигналом шины управления МПСУ (рис.1.4).

Сигналом

![]() =0

открывается для чтения внешний регистр

RG, на входе которого присутствует код

запроса прерывания, например по схеме,

код 1100.1111. Этот код через ШФ, включенный

на передачу информации от ВУ к МП,

поступает на ШД МП.

=0

открывается для чтения внешний регистр

RG, на входе которого присутствует код

запроса прерывания, например по схеме,

код 1100.1111. Этот код через ШФ, включенный

на передачу информации от ВУ к МП,

поступает на ШД МП.

4).

В такте Т3 цикла М1 в течение времени

действия синхроимпульса Ф1 происходит

перепись кода 1100.1111 в регистр команд РК

МП. Далее по фронту синхросигнала Ф2

снимается сигнал DBIN, и вслед за ним

сигнал

![]() устанав-

устанав-

ливается в состояние 1, переводя регистр RG в выключенное состояние.

5). В тактах Т3…Т5 цикла М1 происходит дешифрация кода, считанного из RG. Этот код является КОП команды RST N – "Повторный запуск от прерывания, поступившего под номером N" (приложение А).

В счетчике команд РС находится адрес команды, выполнение которой будет отложено до завершения программы обслуживания запроса прерывания.

6). В цикле М2:

- на ША выставляется адрес (SP-1) ячейки стека, где (SP) – содержимое указателя стека SP;

- на ШД в такте Т1 выводится СС5 "Запись в стек" и затем по синхросигналу Ф1 такта Т2 переписывается в РСС;

- на ШД в такте Т2 выводится старший байт РСН отложенной команды;

-

в такте Т3 активизируется сигнал

![]() (РАЗРЕШЕНИЕ ЗАПИСИ), устанавливается в

0 сигнал

(РАЗРЕШЕНИЕ ЗАПИСИ), устанавливается в

0 сигнал

![]() "Запись в память" и по синхросигналу

Ф1 байт РСН переписывается в ячейку

стека с адресом (SP-1).

"Запись в память" и по синхросигналу

Ф1 байт РСН переписывается в ячейку

стека с адресом (SP-1).

7). В цикле М3:

- на ША выставляется адрес (SP-2) ячейки стека;

- на ШД в такте Т1 выводится СС5 "Запись в стек" и затем по синхросигналу Ф1 такта Т2 переписывается в РСС;

- на ШД в такте Т2 выводится младший байт РСL отложенной команды;

-

в такте Т3 активизируется сигнал

![]() (РАЗРЕШЕНИЕ ЗАПИСИ), устанавливается в

0 сигнал

(РАЗРЕШЕНИЕ ЗАПИСИ), устанавливается в

0 сигнал

![]() "Запись в память" и по синхросигналу

Ф1 байт РСL переписывается в ячейку стека

с адресом (SP-2);

"Запись в память" и по синхросигналу

Ф1 байт РСL переписывается в ячейку стека

с адресом (SP-2);

- в указателе стека значение SP заменяется на значение (SP-2);

- из кода RST N, размещенного в регистре команд РК, формируется стартовый адрес подпрограммы обслуживания прерывания (рис.1.26), который заносится в счетчик команд РС. Так например, из кода 1100.1111 команды RST1 сформируется стартовый адрес 0000.0000.0000.1000В=0008Н подпрограммы обслуживания прерывания.

Командный цикл подтверждения прерывания завершен.

В следующем командном цикле выставляется на ША стартовый адрес 0008Н подпрограммы обслуживания прерывания, взятый из счетчика команд РС. Считанный из ПЗУ код воспринимается как КОП.

Таким образом, ВУ, выставляя запрос прерывания, должно не только послать сигнал INT=1, но и сообщить вариант команды RST. Также ВУ должно снять сигнал INT до завершения подпрограммы обслуживания прерывания.

Вопросы и задания

1. Что такое – стек? Как происходит заполнение и считывание стека?

2. Поясните диаграммы сигналов и структурную схему при выполнении цикла М1 подтверждения прерывания. В чем его принципиальное отличие от цикла М1 выполнения команд?

3. Как формируется стартовый адрес подпрограммы обработки прерывания при обслуживании запроса прерывания?

4. Поясните диаграммы сигналов и структурную схему при выполнении циклов М2 и М3 подтверждения прерывания. Откуда берутся адреса ячеек стека и адрес

отложенной команды?

5. Дайте характеристику управляющим сигналам командного цикла подтверждения прерывания.