- •Раздел 1. Микропроцессорные системы управления.

- •Раздел 2. Микроконтроллерные системы управления.

- •Раздел 3. Вопросы эксплуатации микропроцессорных устройств.

- •1. Микропроцессорные системы управления

- •1.1. Принципы построения и основы работы

- •Вопросы и задания

- •1.2. Элементная база мпсу

- •Вопросы и задания

- •1.3. Оперативные запоминающие устройства.

- •Вопросы и задания

- •1.4. Постоянные запоминающие устройства.

- •Вопросы и задания

- •1.5. Архитектура микропроцессора типа кр580вм80

- •Вопросы и задания

- •1.6. Типы машинных циклов и слово состояния

- •Вопросы и задания

- •1.7. Командные циклы чтения/записи

- •Вопросы и задания

- •1.8. Командный цикл подтверждения прерывания.

- •1.9. Принципиальные электрические схемы

- •Вопросы и задания

- •1.10. Интерфейс мпсу с изолированной системой шин

- •Вопросы и задания

- •1.11. Интерфейс мпсу с общей системой шин

- •1.12. Организация обслуживания запросов прерывания

- •Вопросы и задания

- •1.13. Программируемый контроллер

- •Вопросы и задания

- •1.14. Программируемый контроллер прерываний

- •Вопросы и задания

- •1.15. Программируемый интервальный таймер

- •Вопросы и задания

- •1.16. Мпсу с вводом-выводом аналоговой информации

- •Вопросы и задания

- •1.17. Выходные каскады мпсу

- •Вопросы и задания

- •2. Микроконтроллерные системы управления

- •2.1. Архитектура микроконтроллера к1816ве51

- •Вопросы и задания

- •2.2. Принципиальная электрическая схема порта

- •2.3. Схемы подключения внешней памяти к мк51

- •Вопросы и задания

- •2.4. Интерфейс мк51 с большим числом

- •Вопросы и задания

- •2.5. Таймер/счетчики мк51.

- •Вопросы и задания

- •2.6. Система прерываний мк51. Использование прерываний в программах

- •Вопросы и задания

- •2.7. Основы организации

- •Допустимые различия скорости приемо-передачи

- •2.8. Организация мультиконтроллерных систем

- •Программы инициализации станции и абонентов

- •Программы станции и абонента в сеансе "станция→абонент"

- •2.9. Микроконтроллерная система управления

- •3. Вопросы эксплуатации микропроцессорных устройств

- •3.1. Отладка аппаратных средств мпсу

- •Вопросы и задания

- •3.2. Отладка программного обеспечения мпсу

- •Вопросы и задания

- •3.3. Методы обеспечения помехоустойчивости мпсу

- •Вопросы и задания

- •1. Группа команд пересылок

- •2. Группа команд инкремента-декремента

- •3. Группа арифметических команд

- •4. Группа логических команд

- •5. Группа команд сдвига

- •6. Группа команд передачи управления

- •7. Группа команд работы со стеком

- •8. Группа команд ввода-вывода и управления микропроцессором

- •1. Группа команд пересылок

- •2. Группа команд арифметических операций

- •3. Группа команд логических операций

- •4. Группа команд операций с битами

- •5. Группа команд передачи управления

- •Дворак Николай Маркович микропроцессорные устройства

- •В высших учебных заведениях 3-4 уровней

- •98309, Г. Керчь, ул. Орджоникидзе, 82

- •98309, Г. Керчь, ул. Орджоникидзе, 82

Вопросы и задания

1. Поясните функциональную схему микроконтроллера.

2. Дайте характеристику памяти программ и сигнальная поддержка выбора ее вида.

3. Дайте характеристику памяти данных и сигнальная поддержка выбора ее вида.

4. Поясните структуру оперативной памяти данных. Поясните целесообразность выделения в ней побайтно и побитно адресуемых ячеек и банков оперативной памяти.

5. Поясните состав и назначение блока регистров специальных функций.

6. Поясните содержимое регистра слова состояния программы. Составьте программу активизации заданного банка оперативной памяти данных.

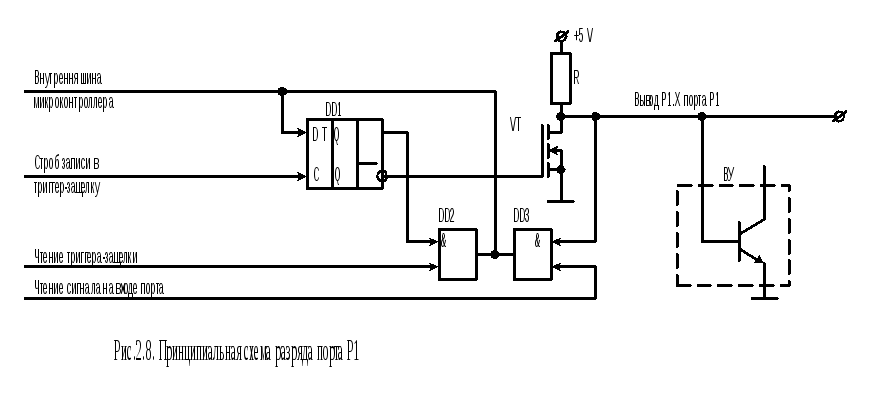

2.2. Принципиальная электрическая схема порта

ввода-вывода МК51. Организация вывода

и ввода информации битами и байтами

В программном отношении порты ввода/вывода представляют собой однобайтные ячейки оперативного запоминающего устройства, состоящие из прямо адресуемых бит, сигналы с которых выведены на корпус МК51. Независимая адресация бит портов позволяет настраивать их биты на ввод или вывод в произвольном сочетании. Все порты МК51 двунаправленные.

Порт Р0 трехстабильный, нагрузочная способность 1,6 мА.

Порты Р1…Р3 двухстабильные, нагрузочная способность 0,8 мА.

Порт Р1 используется только для простого ввода/вывода и, поэтому принципиальная схема его самая простая. Остальные порты кроме простого ввода/вывода могут использоваться для иных альтернативных операций ввода/вывода:

- через порт Р0 выводится младший байт адреса внешней памяти при обмене информацией с ВПП и ВПД;

- через порт Р2 выводится старший байт адреса внешней памяти при обмене информацией с ВПП и ВПД;

-

через порт Р3 выводятся управляющие

сигналы чтения

![]() и записи

и записи

![]() внешней памяти, биты TXD и RXD в операциях,

соответственно, вывода на внешние

устройства последовательного кода и

чтения внешних устройств в последовательном

коде, сигналы

внешней памяти, биты TXD и RXD в операциях,

соответственно, вывода на внешние

устройства последовательного кода и

чтения внешних устройств в последовательном

коде, сигналы

![]() и

и

![]() прерываний и входные импульсы Т0 и Т1

таймер/счетчиков (Т/С).

прерываний и входные импульсы Т0 и Т1

таймер/счетчиков (Т/С).

Принципы построения схем портов и принципы действия одинаковы для всех портов. Наиболее простая схема порта Р1 (рис.2.8). Рассмотрим работу порта Р1 при выводе и вводе информации.

Р ежим

вывода информации.

При выводе через порт сигнала 1 на

внутренней шине МК выставляется сигнал

1 и на входе синхронизации С D-триггера

DD1 проходит импульс единичного строба.

Сигнал 1 записывается в триггер-защелку

DD1. Сигналом

ежим

вывода информации.

При выводе через порт сигнала 1 на

внутренней шине МК выставляется сигнал

1 и на входе синхронизации С D-триггера

DD1 проходит импульс единичного строба.

Сигнал 1 записывается в триггер-защелку

DD1. Сигналом

![]() полевой транзистор VT с индуцированным

каналом удерживается закрытым и на его

стоке устанавливается высокое напряжение

логического уровня 1, подводимое от

источника питания +5 В через резистор

R. При выводе через порт сигнала 0 в

триггер-защелку записывается 0. Сигналом

полевой транзистор VT с индуцированным

каналом удерживается закрытым и на его

стоке устанавливается высокое напряжение

логического уровня 1, подводимое от

источника питания +5 В через резистор

R. При выводе через порт сигнала 0 в

триггер-защелку записывается 0. Сигналом

![]() полевой транзистор VT открывается и на

его стоке устанавливается низкое

напряжение логического уровня 0.

полевой транзистор VT открывается и на

его стоке устанавливается низкое

напряжение логического уровня 0.

В режиме вывода информации возможно выполнение арифметических и логических операций над содержимым порта непосредственно в порту по типу "чтение-модификация-запись". Для правильного восприятия состояния порта чтение производится не с физического вывода Р1.Х порта Р1, а с триггера-защелки DD1, сигнал Q которого совпадает с логическим состоянием порта, с использованием логического элемента DD2. Сделано это потому, что логическое состояние порта и выходной уровень напряжения порта могут не соответствовать друг другу, если к порту подключена мощная нагрузка. Если нагрузкой порта является эмиттерный переход транзистора ВУ, то напряжение на выходе порта не поднимется выше 0,5…0,7 В, что соответствует логическому уровню 0 независимо от фактического логического состояния выхода порта.

Режим ввода информации. Для настройки разряда порта на ввод в него предварительно нужно записать 1. По умолчанию (при включении питания или сбросе) во все разряды портов записываются сигналы 1 и все порты настроены на ввод. При записанной в порт единице транзистор VT закрыт и на вывод Р1.Х через резистор R (сопротивление 6,2 кОм) поступает напряжение +5 В. При малом выходном сопротивлении внешнего устройства (<<6,2 кОм) напряжение на выводе Р1.Х совпадает с уровнем сигнала, посылаемым внешним устройством. Чтение сигнала порта осуществляется через логический элемент DD3. Особенность начальной установки портов нужно учитывать при использовании его в режиме вывода: уровень 1 всех портов считается пассивным, а уровень 0 - активным.

Схемы остальных портов отличаются от рассмотренной схемы порта Р1 тем, что в них добавлены логические элементы, обеспечивающие альтернативные функции выводов портов.

Рассмотрим программное обеспечение простого ввода и вывода информации через порты МК51 на примере микроконтроллерной системы управления (МКСУ) контактором, принципиальная схема и алгоритм которой приведены на рис.2.9. На принципиальной электрической схеме показано также подключение кварцевого резонатора Q, кнопки сброса и цепь начальной установки, состоящая из конденсатора С3 и резистора R1.

С начала

проверяется кнопка С ("Стоп"). Если

С нажата, то переход на блок 4, где

отключается контактор К, гасится лампа

"Включено" ЛВ и зажигается лампа

"Отключено" ЛО. Если С не нажата,

то проверяется кнопка П ("Пуск").

Если П не нажата, то переход на блок 1,

иначе переход на блок 3, где включается

контактор К, зажигается лампа "Включено"

ЛВ и гасится лампа "Отключено" ЛО.

начала

проверяется кнопка С ("Стоп"). Если

С нажата, то переход на блок 4, где

отключается контактор К, гасится лампа

"Включено" ЛВ и зажигается лампа

"Отключено" ЛО. Если С не нажата,

то проверяется кнопка П ("Пуск").

Если П не нажата, то переход на блок 1,

иначе переход на блок 3, где включается

контактор К, зажигается лампа "Включено"

ЛВ и гасится лампа "Отключено" ЛО.

|

Код |

Мнемокод |

Комментарии |

|

|

|

Вариант 1: Вывод битами: |

|

|

|

а) с использованием мнемонических обозначений бит |

|

C2 A0 |

CLR P2.0 |

P2.0←0; используется команда CLR bit |

|

D2 A2 |

SETB P2.2 |

P2.2←1; используется команда SETB bit |

Рис.2.10. Вывод информации через порт МК51

|

Код |

Мнемокод |

Комментарии |

|

|

|

б) с использованием адресов бит |

|

C2 A0 |

CLR A0 |

(A0)←0; А0 – адрес бита 0 порта Р2; используется команда CLR bit |

|

D2 A2 |

SETB A2 |

(A2)←1; А2 – адрес бита 2 порта Р2; используется команда SETB bit |

|

|

|

Вариант 2: Вывод байтами: |

|

|

|

а) с использованием мнемонического обозначения порта |

|

75 A0 04 |

MOV P2, #04 |

P2←#04, где #04Н=#0000.0100В; используется команда MOV ad, #d |

|

|

|

б) с использованием адреса порта |

|

75 A0 04 |

MOV А0, #04 |

(A0)←#04; А0 – адрес порта Р2; используется команда MOV ad, #d |

|

|

|

Вариант 3: Вывод маскированием порта: |

|

|

|

а) с использованием мнемонического обозначения порта |

|

53 A0 FE |

ANL P2, #FE |

(P2)←(P2)Λ(#1111.1110В), причем #1111.1110В=#FEН; используется команда ANL ad, #d |

|

43 A0 04 |

ORL P2, #04 |

(P2)←(P2)V(#0000.0100В), причем #0000.0100В=#04Н; используется команда ORL ad, #d |

|

|

|

б) с использованием адреса порта |

|

53 A0 FE |

ANL A0, #FE |

(А0)←(А0)Λ(#1111.1110В) |

|

43 A0 04 |

ORL A0, #04 |

(А0)←(А0)V(#0000.0100В) |

|

Рис.2.10. Продолжение |

||

Вывод информации. Вывод информации на контактор К с лампой ЛВ и на лампу ЛО можно выполнить тремя вариантами. На рис.2.10 показан вывод для блока 3 алгоритма тремя вариантами.

Вариант 1 самый простой, так как вывод осуществляется на адреса контактов, расположенных на корпусе микроконтроллера.

Вариант 2 сложнее варианта 1 тем, что требуется составлять сначала двоичный, а затем 16-ричный код вывода в порт. Этот вид вывода неприменим, когда к остальным разрядам порта подключены другие потребители.

Вариант 3 сложнее варианта 1 тем, что нужно дважды составлять сначала двоичный, а затем 16-ричный код маски. Этот вид вывода можно применять даже тогда, когда к остальным разрядам порта подключены другие потребители.

Итак, самый простой вариант вывода – битами. Можно выводить с использованием маски. Непосредственный вывод байтами в условиях обслуживания нескольких внешних устройств неприменим: байт нужно предварительно сформировать с использованием аккумулятора, регистров и копии порта, и все это за счет дополнительных команд.

При составлении кодов команд используются приведенные на рис.2.11 шаблоны по типам (Т) команд. Типы команд Т указываются в таблице команд (приложение Б).

На рис.2.11 обозначены:

#d – числовая константа (числовое данное), к обозначению которой добавляется значок #;

ad – 8-разрядный адрес;

bit – адрес бита;

rel – величина относительного перехода;

ads и add – 8-разрядные адреса источника и приемника информации;

ad16h и ad16l – старший и младший байты 16-разрядного адреса ad16;

#d16h и #d16l – старший и младший байты 16-разрядного данного d16.

-

Тип

1-й байт команды

2-й байт команды

3-й байт команды

(Т)

D7D6D5D4D3D2D1D0

D7D6D5D4D3D2D1D0

D7D6D5D4D3D2D1D0

1

КОП

2

КОП

#d

3

КОП

ad

4

КОП

bit

5

КОП

rel

6

А10А9А8|КОП

A7A6A5A4A3A2A1A0

7

КОП

ad

#d

8

КОП

ad

rel

9

КОП

ads

add

10

КОП

#d

rel

11

КОП

bit

rel

12

КОП

ad16h

ad16l

13

КОП

#d16h

#d16l

Рис.2.11. Шаблоны по типам команд МК51

Ввод информации. Ввод информации осуществляется двумя способами:

1) ввод байтами без непосредственного анализа содержимого его бит;

2) ввод битами с непосредственным анализом их значений.

Ввод байтами без непосредственного анализа содержимого его бит осуществляется из порта в ячейку резидентной памяти данных, состоящую из ячеек ОПД и РСФ. В зависимости от вида ячейки приемника информации возможны варианты такого ввода, представленные на рис.2.12 (адрес 04Н и регистр R4 приняты произвольно). Переписанная из порта информация анализируется в ячейке-приемнике.

|

Код |

Мнемокод |

Комментарии |

|

|

|

Вариант 1: Ввод из порта на адрес ячейки РПД: |

|

85 04 90 |

MOV 04, P1 |

(04)←P1; 04Н – адрес ячейки РПД |

|

85 04 90 |

MOV 04, 90 |

(04)←(90); 90Н – адрес порта Р1 |

|

|

|

Вариант 2: Ввод из порта в регистр: |

|

АС 90 |

MOV R4, P1 |

(R4)←P1; R4 – обозначение регистра |

|

АС 90 |

MOV R4, 90 |

(R4)←(90) |

|

|

|

Вариант 3: Ввод из порта в аккумулятор: |

|

Е5 90 |

MOV А, P1 |

(А)←P1 |

|

Е5 90 |

MOV А, 90 |

(А)←(90) |

|

Рис.2.12. Ввод информации байтами через порт МК51 |

||

Ввод битами с непосредственным анализом их значений является основным, так как сразу запускается программа-реакция на введенную информацию. Для такого ввода используются две команды: JB bit, rel и JNB bit, rel и если проверяемый бит bit равен, соответственно, 1 или 0, то следующей выполняется команда, адрес которой формируется с учетом значения rel относительного перехода. Величина rel является числом со знаком, десятичные значения которой заключены в пределах от –12810 до +12710. Если проверка бита bit на значение 1 или 0 ложна, то далее выполняется команда по следующему за командой JB bit, rel или JNB bit, rel адресу. Если проверка бита bit на 1 или 0 истинна, то далее выполняется команда по адресу, равному сумме числа rel и адреса команды, которая следует за командой JB bit, rel или JNB bit, rel. Этим осуществляется переход к выполнению команды по адресам максимум на 128 ячеек ПП назад по программе и максимум на 127 ячеек вперед относительно выполненной команды JB bit, rel или JNB bit, rel.

В кодовом представлении двоичных чисел не используются символы + и – знака числа, как это принято для десятичных чисел. Коды отрицательных двоичных 8-разрядных чисел N2 выводятся из следующего выражения суммы

Р2+N2=1.0000.0000, (2.1)

в котором Р2 является двоичным кодом положительного числа, а N2 - кодом отрицательного числа, равным по абсолютной величине положительному числу Р2.

В коде 1.0000.0000 суммы восемь младших разрядов (байт) являются кодом нуля, старший восьмой разряд выходит за пределы байта и, поэтому, на значение указанного байта не влияет. Следовательно, если складываемые коды чисел Р2 и N2 имеют 8 разрядов, код 100Н является машинным нулем, и поэтому числа ad и ad+10016 являются одинаковыми числами. Из равенства (2.1) следует определение кодов отрицательных, соответственно, двоичных и шестнадцатеричных чисел

N2=1.0000.0000-Р2 и N16=100-Р16=FF-Р16+1 (2.2)

Для разграничения кодов положительных Р и отрицательных N восьмиразрядных чисел используют значение старшего 7-го бита кода: если D7=0, то число считается положительным, а при D7=1 – отрицательным (рис.2.13).

-

Положительные числа Р

Отрицательные числа N

десятичные

двоичные

16-ричные

десятичные

двоичные

16-ричные

0

0

0

0

0.

0

0

0

0

00

-128

1

0

0

0.

0

0

0

0

80

1

0

0

0

0.

0

0

0

1

01

-127

1

0

0

0.

0

0

0

1

81

:

:

126

0

1

1

1.

1

1

1

0

7Е

-2

1

1

1

1.

1

1

1

0

FE

127

0

1

1

1.

1

1

1

1

7F

-1

1

1

1

1.

1

1

1

1

FF

Рис.2.13. Коды положительных и отрицательных чисел

Если adНАЧ – начальный адрес, равный адресу команды непосредственно следующей за командой JB bit, rel или JNB bit, rel, а adКОН – конечный адрес, определяемый как adНАЧ+rel, то величина rel относительного перехода по программе определяется 16-ричными выражениями

(2..3)

(2..3)

где bit7rel – 7-й бит (знаковый) в коде числа rel.

В блоках 1 и 2 алгоритма МКСУ контактором (рис.2.9) содержится проверка бит вводимой информации. При проверке бит командами JB bit, rel и JNB bit, rel программа МКСУ контактором примет вид, приведенный на рис.2.14.

|

Адрес |

Код команды |

Метка |

Мнемокод |

Комментарии |

|||

|

000 |

30 |

91 |

08 |

|

M1 |

JNB P1.1, M4 |

adНАЧ=003, adКОН=00B, rel=08; bit7rel=0 |

|

003 |

20 |

90 |

FA |

|

M2 |

JB P1.0, M1 |

adНАЧ=006, adКОН=000, rel=FA; bit7rel=1 |

|

006 |

75 |

A0 |

04 |

|

M3 |

MOV P2, #04 |

|

|

009 |

80 |

F5 |

|

|

|

SJMP M1 |

adНАЧ=00B, adКОН=000, rel=F5; bit7rel=1 |

|

00B |

75 |

A0 |

01 |

|

M4 |

MOV P2, #01 |

|

|

00E |

80 |

F0 |

|

|

|

SJMP M1 |

adНАЧ=010, adКОН=000, rel=F0; bit7rel=1 |

|

Рис.2.14. Программа МКСУ контактором |

|||||||

Особенностью программ, в которых используются команды с переменной rel, является их модульность. Например, начальный адрес программы МКСУ контактором (рис.2.14) может быть любым, а не только 000Н, и программа будет работать в соответствии с алгоритмом. Такая особенность дает возможность составлять программы управления отдельными объектами в виде законченных и отлаженных модулей, а затем объединять их в одну МКСУ. Это проще, чем составлять одну большую программу управления сразу всем множеством объектов.

Вопросы и задания

1. Приведите общие характеристики и варианты использования портов ввода-вывода микроконтроллера.

2. Что такое – альтернативное использование портов ввода-вывода.

3. Объясните работу принципиальной схемы разряда порта Р1. Поясните целесообразность введения в схему порта регистра-защелки.

4. Поясните принципиальную схему и алгоритм микроконтроллерной системы управления контактором.

5. Какие существуют способы вывода информации через порты микроконтроллера? Составьте программы вывода информации.

6. Составьте программы ввода информации без непосредственного анализа ее бит.

7. Поясните сущность и назовите достоинства способа ввода информации с одновременным анализом ее бит.

8. Дайте определения кодам отрицательных чисел. Поясните процедуру вычисления кода заданного отрицательного числа.

9. Поясните структуру команд перехода, использующих относительную адресацию, и поясните процедуру вычисления адреса относительного перехода.

10. В чем основные преимущества относительной адресации?

11. Поясните программу управления контактором, обратив особое внимание на вычисления величин значений относительных переходов.