- •Раздел 1. Микропроцессорные системы управления.

- •Раздел 2. Микроконтроллерные системы управления.

- •Раздел 3. Вопросы эксплуатации микропроцессорных устройств.

- •1. Микропроцессорные системы управления

- •1.1. Принципы построения и основы работы

- •Вопросы и задания

- •1.2. Элементная база мпсу

- •Вопросы и задания

- •1.3. Оперативные запоминающие устройства.

- •Вопросы и задания

- •1.4. Постоянные запоминающие устройства.

- •Вопросы и задания

- •1.5. Архитектура микропроцессора типа кр580вм80

- •Вопросы и задания

- •1.6. Типы машинных циклов и слово состояния

- •Вопросы и задания

- •1.7. Командные циклы чтения/записи

- •Вопросы и задания

- •1.8. Командный цикл подтверждения прерывания.

- •1.9. Принципиальные электрические схемы

- •Вопросы и задания

- •1.10. Интерфейс мпсу с изолированной системой шин

- •Вопросы и задания

- •1.11. Интерфейс мпсу с общей системой шин

- •1.12. Организация обслуживания запросов прерывания

- •Вопросы и задания

- •1.13. Программируемый контроллер

- •Вопросы и задания

- •1.14. Программируемый контроллер прерываний

- •Вопросы и задания

- •1.15. Программируемый интервальный таймер

- •Вопросы и задания

- •1.16. Мпсу с вводом-выводом аналоговой информации

- •Вопросы и задания

- •1.17. Выходные каскады мпсу

- •Вопросы и задания

- •2. Микроконтроллерные системы управления

- •2.1. Архитектура микроконтроллера к1816ве51

- •Вопросы и задания

- •2.2. Принципиальная электрическая схема порта

- •2.3. Схемы подключения внешней памяти к мк51

- •Вопросы и задания

- •2.4. Интерфейс мк51 с большим числом

- •Вопросы и задания

- •2.5. Таймер/счетчики мк51.

- •Вопросы и задания

- •2.6. Система прерываний мк51. Использование прерываний в программах

- •Вопросы и задания

- •2.7. Основы организации

- •Допустимые различия скорости приемо-передачи

- •2.8. Организация мультиконтроллерных систем

- •Программы инициализации станции и абонентов

- •Программы станции и абонента в сеансе "станция→абонент"

- •2.9. Микроконтроллерная система управления

- •3. Вопросы эксплуатации микропроцессорных устройств

- •3.1. Отладка аппаратных средств мпсу

- •Вопросы и задания

- •3.2. Отладка программного обеспечения мпсу

- •Вопросы и задания

- •3.3. Методы обеспечения помехоустойчивости мпсу

- •Вопросы и задания

- •1. Группа команд пересылок

- •2. Группа команд инкремента-декремента

- •3. Группа арифметических команд

- •4. Группа логических команд

- •5. Группа команд сдвига

- •6. Группа команд передачи управления

- •7. Группа команд работы со стеком

- •8. Группа команд ввода-вывода и управления микропроцессором

- •1. Группа команд пересылок

- •2. Группа команд арифметических операций

- •3. Группа команд логических операций

- •4. Группа команд операций с битами

- •5. Группа команд передачи управления

- •Дворак Николай Маркович микропроцессорные устройства

- •В высших учебных заведениях 3-4 уровней

- •98309, Г. Керчь, ул. Орджоникидзе, 82

- •98309, Г. Керчь, ул. Орджоникидзе, 82

Вопросы и задания

-

Почему к шинам данных недопустимо подключение элементов с двухстабильным выводом сигналов?

2.

Поясните работу схемы трехстабильного

элемента с сигналом 0 на его входе при

наличии разрешающего сигнала вывода

![]() =0.

=0.

3.

Поясните работу схемы трехстабильного

элемента с сигналом 1 на его входе при

наличии разрешающего сигнала вывода

![]() =0.

=0.

4.

Поясните работу схемы трехстабильного

элемента с любым сигналом на его входе

при запрещающем сигнале вывода

![]() =1.

=1.

5. Определите назначение и приведите характеристики шинных формирователей и микросхем регистров.

6. Приведите протокол обмена информацией в МПСУ с раздельными шинами адреса и данных.

7. Приведите протокол обмена информацией в МПСУ с совмещенными шинами адреса и данных.

1.3. Оперативные запоминающие устройства.

Блоки оперативной памяти

Оперативное запоминающее устройство (ОЗУ; RAM - Random Access Memory) служит для записи в него, хранения и чтения из него информации. ОЗУ является энергозависимой памятью, так что при выключении питания микросхемы память очищается. Данные сохраняются в ОЗУ, пока есть его питание. ОЗУ является относительно медленной памятью. Шины данных всех ОЗУ трехстабильные.

Основные характеристики ОЗУ: способ хранения информации, емкость, организация памяти, быстродействие и энергопотребление в режимах записи/чтения и хранения.

По способу хранения ОЗУ подразделяются на статические, динамические и регистровые. В статических ОЗУ единица информации – бит – хранится в RS-триггерах. В динамических ОЗУ единица информации – бит – хранится в конденсаторах емкостью несколько пикофарад, причем для восстановления напряжения конденсатора, который довольно быстро разряжается, вводится операция регенерации памяти. Примером регистрового ОЗУ является регистр КР580ИР82.

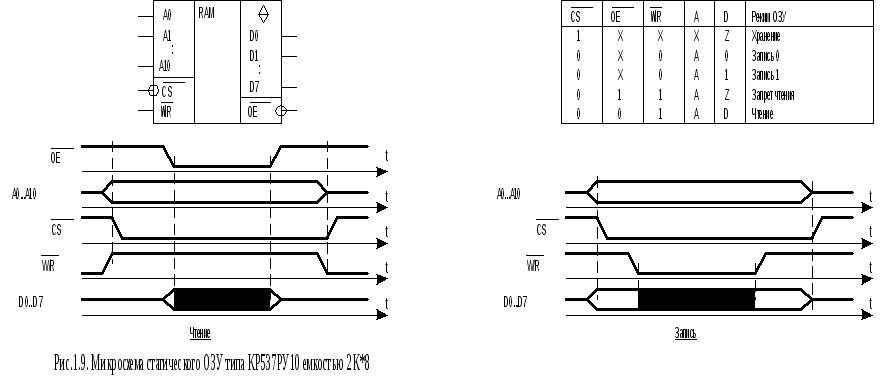

Емкость микросхем ОЗУ измеряется в битах, которая указывается в обозначении ИМС. Память ОЗУ организуется битами, тетрадами, байтами и словами, соответственно, по 1, 4, 8 и 16 бит информации на один адрес ячейки памяти. Об организации памяти можно узнать из справочных данных, а также из размерности шины данных ОЗУ. Емкость ОЗУ можно найти как произведение размера ШД (1, 4, 8 или 16) на емкость адресного пространства ОЗУ, равной 2AN, где AN – размер шины адреса ОЗУ. Так, приведенная на рис.1.6 ИМС статического ОЗУ типа КР537РУ10, имеет размер шины данных равный 8 (память организована байтами, т.е. информация записывается, хранится и считывается байтами), размер шины адреса AN=11 (от А0 до А10), емкость адресного пространства 211=2048=2К, емкость ИМС составляет 2К·8 или 2 Кбайта. Емкость ОЗУ в битах составляет 16 Кбит, которая в обозначении ИМС указана как 16К.

Статические ОЗУ имеют организацию по 1, 4, 8 и 16 бит на адрес и относительно небольшую емкость – до 1 Мбит (1024 Кбит) на одну ИМС. Динамические ОЗУ организуются только битами и имеют большую емкость – 16 Мбит и выше.

Быстродействие оценивается величиной времени цикла записи/считывания tЦ.ЗП(СЧ) и имеет порядок десятки-сотни наносекунд.

Энергопотребление в режимах записи/считывания составляет десятки-сотни милливатт на одну ИМС ОЗУ, в режиме хранения снижается на 2-3 порядка, а при уменьшении напряжении питания микросхем, когда еще обеспечивается сохранность информации, мощность снижается еще на 2-3 порядка.

Рассмотрим микросхему статического ОЗУ типа КР537РУ10 (рис.1.6 и рис.1.9) с характеристиками: емкость 16К, организация 2К·8, tЦ.ЗП(СЧ)=110…500 нс, РЗП(СЧ)=350 мВт при UСС=5 В, РХРАН=0,6…1,0 мкВт при UХРАН=2 В.

Э то

ОЗУ имеет: ША размером 11 бит; двунаправленную

ШД размером 8 бит=1 байт (от D0 до D7); ножку

то

ОЗУ имеет: ША размером 11 бит; двунаправленную

ШД размером 8 бит=1 байт (от D0 до D7); ножку

![]() выбора кристалла; ножку

выбора кристалла; ножку

![]() разрешения вывода информации из ОЗУ и

ножку

разрешения вывода информации из ОЗУ и

ножку

![]() управления записью/считыванием памяти,

причем при

управления записью/считыванием памяти,

причем при

![]() производится запись в ОЗУ, а при

производится запись в ОЗУ, а при

![]() - чтение.

- чтение.

Т аблица

режимов работы ИМС и диаграммы сигналов

при чтении и записи ОЗУ приведены на

рис.1.9. Требуемая последовательность и

длительность сигналов на диаграммах

определяется содержанием машинных

циклов МП и схемой МЭВМ. Подробно этот

вопрос рассматривается на рис.1.20 и

рис.1.26.

аблица

режимов работы ИМС и диаграммы сигналов

при чтении и записи ОЗУ приведены на

рис.1.9. Требуемая последовательность и

длительность сигналов на диаграммах

определяется содержанием машинных

циклов МП и схемой МЭВМ. Подробно этот

вопрос рассматривается на рис.1.20 и

рис.1.26.

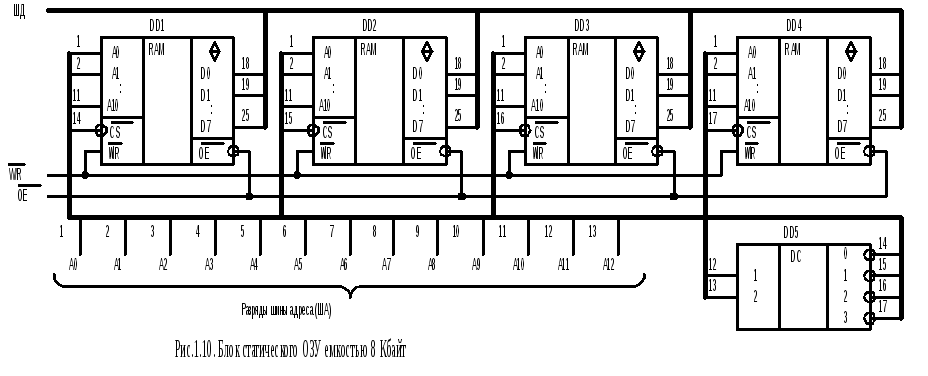

Из нескольких корпусов ИМС создаются блоки оперативной памяти большой информационной емкости. Так, на рис.1.10 приведена схема ОЗУ емкостью 8 Кбайт, составленного из четырех ИМС DD1…DD4 типа КР537РУ10 и дешифратора DD5. Ориентируясь на использование в МЭВМ МП типа КР580ВМ80, приведем команды чтения и записи ячеек этого блока памяти и разберем их выполнение на сигнальном уровне, которое отражено на вышеприведенных диаграммах.

Распределение адресов ячеек памяти по ИМС блока имеет вид:

|

ИМС |

Диапазон адресов |

|||

|

Двоичные адреса |

16-ричные адреса |

|||

|

Минимальный адрес |

Максимальный адрес |

Мин. адрес |

Макс. адрес |

|

|

DD1 |

0000.0000.0000.0000 |

0000.0111.1111.1111 |

0000 |

07FF |

|

DD2 |

0000.1000.0000.0000 |

0000.1111.1111.1111 |

0800 |

0FFF |

|

DD3 |

0001.0000.0000.0000 |

0001.0111.1111.1111 |

1000 |

17FF |

|

DD4 |

0001.1000.0000.0000 |

0001.1111.1111.1111 |

1800 |

1FFF |

Двоичные адреса для удобства их восприятия разбиты на тетрады, которые друг от друга отделяются точками. Шестнадцатеричные адреса получаются заменой указанных тетрад на символы 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F шестнадцатеричной системы счисления.

Команда чтения содержимого ячейки памяти с адресом 1С5В и пересылки результата в аккумулятор МП имеет вид:

LDA 1C5B (в ассемблере)

и 3А 5В 1С (в машинных кодах).

В этой записи 3А – код операции (КОП) команды LDA (прямая загрузка в аккумулятор содержимого ячейки, адрес которой указан во 2-м и 3-м байтах команды), а 5В1С – операнд, который является записью адреса ячейки 1С5В памяти, содержимое которой нужно переслать в аккумулятор МП. По правилам синтаксиса команд МП КР580ВМ80 в операнде записывается сначала младший байт адреса ячейки памяти, а затем старший. В естественной записи адреса старший байт располагается впереди младшего.

Ячейка с адресом 1С5В находится в ИМС DD4.

Этапы выполнения команды LDA 5B1C:

1). МП выставляет на ША адрес 1С5ВН=0001.1100.0101.1011. Биты этого адреса используются в схеме блока памяти (рис.1.10) следующим образом:

|

Биты адреса |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Адрес |

0 |

0 |

0 |

1. |

1 |

1 |

0 |

0. |

0 |

1 |

0 |

1. |

1 |

0 |

1 |

1 |

|

Использование бит адреса |

Не используются |

На вход DD5 |

На адресные входы всех ИМС блока памяти |

|||||||||||||

Одновременно

устанавливается сигнал чтения

![]() .

.

2).

На код 11, поступивший на вход дешифратора

DD5, на его выходе 3 устанавливается

активный сигнал 0. По проводу 17 сигнал

0 поступает на ножку

![]() ИМС DD4, которая переходит в активный

режим, а остальные ИМС памяти остаются

неактивными. В активной ИМС DD4 выбирается

ячейка с адресом 45ВН = 100.0101.1011В.

ИМС DD4, которая переходит в активный

режим, а остальные ИМС памяти остаются

неактивными. В активной ИМС DD4 выбирается

ячейка с адресом 45ВН = 100.0101.1011В.

3). Через некоторое время на внутренней шине данных ИМС DD4 устанавливаются действительные данные ячейки памяти, которые можно считывать.

4).

МП формирует импульс

![]() ,

и информация с внутренней ШД поступает

на выход ИМС, который соединен с ШД МП.

Содержимое из ячейки памяти ИМС DD4 с

адресом 45ВН передается в аккумулятор

микропроцессора.

,

и информация с внутренней ШД поступает

на выход ИМС, который соединен с ШД МП.

Содержимое из ячейки памяти ИМС DD4 с

адресом 45ВН передается в аккумулятор

микропроцессора.

5).

МП снимает с ША адрес 1С5В и одновременно

снимается сигнал чтения

![]() .

.

Команда записи содержимого аккумулятора МП в ячейку памяти с адресом 0F3D имеет вид:

STA 0F3D (в ассемблере)

и 32 3D 0F (в машинных кодах).

В этой записи 32 – код операции (КОП) команды STA, а 3D0F – операнд, который является записью адреса ячейки 0F3D памяти, в которую нужно переслать содержимое аккумулятора МП. В записи операнда применено упомянутое выше правило синтаксиса.

Ячейка с адресом 0F3D находится в ИМС DD2.

Этапы выполнения команды STA 0F3D:

1). МП выставляет на ША адрес 0F3DН=0000.1111.0011.1101В. Биты этого адреса используются в соответствии с принципиальной схемой блока следующим образом:

|

Биты адреса |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Адрес |

0 |

0 |

0 |

0. |

1 |

1 |

1 |

1. |

0 |

0 |

1 |

1. |

1 |

1 |

0 |

1 |

|

Использование бит адреса |

Не используются |

На вход DD5 |

На адресные входы всех ИМС блока памяти |

|||||||||||||

Одновременно на ШД МП выводятся данные из аккумулятора.

2).

На код 01, поступивший на вход дешифратора

DD5, на его выходе 1 устанавливается

активный сигнал 0. По проводу 15 сигнал

0 поступает на ножку

![]() ИМС DD2, которая переходит в активный

режим, а остальные ИМС памяти остаются

неактивными. В активной ИМС DD2 выбирается

ячейка с адресом 73DН = 111.0011.1101В.

ИМС DD2, которая переходит в активный

режим, а остальные ИМС памяти остаются

неактивными. В активной ИМС DD2 выбирается

ячейка с адресом 73DН = 111.0011.1101В.

3).

Через некоторое время проходит импульс

записи

![]() .

Данные с ШД МП переписываются в ячейку

памяти ИМС DD2 с адресом 73D.

.

Данные с ШД МП переписываются в ячейку

памяти ИМС DD2 с адресом 73D.

4).

МП снимает с ША адрес 0F3D, вслед за которым

снимается сигнал

![]() .

.

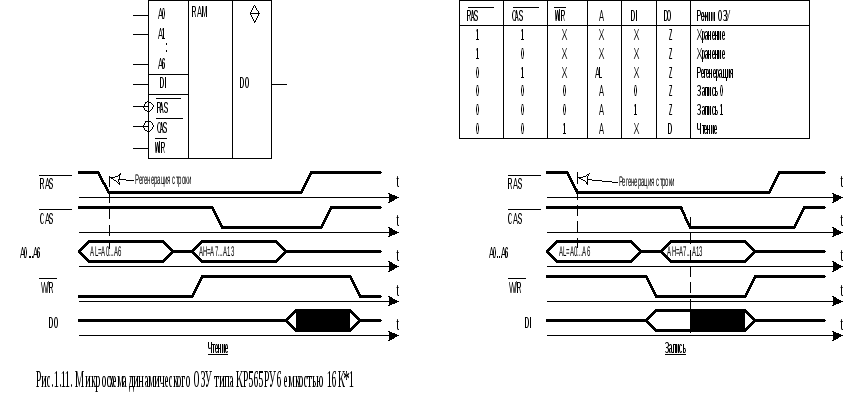

Рассмотрим микросхему динамического ОЗУ типа КР565РУ6 (рис.1.11) с характеристиками: емкость 16К, организация 16К·1, tЦ.ЗП(СЧ)=150…250 нс, РЗП(СЧ)=160 мВт при UСС=5 В, РХРАН=21 мВт при UХРАН=5 В.

Это

ОЗУ имеет мультиплексируемую ША размером

7 бит (от А0 до А6), раздельные ШД (на ввод

DI и вывод DO) размером 1 бит каждая, вход

![]() управления записью/считыванием памяти,

причем при

управления записью/считыванием памяти,

причем при

![]() производится запись в ОЗУ, а при

производится запись в ОЗУ, а при

![]() - чтение ОЗУ. Массив ячеек памяти внутри

ИМС организован в виде квадрата со

сторонами, равными 27=128. Общая

емкость равна 128·128=214=16384 однобитных

ячеек, т.е. 16 Кбит.

- чтение ОЗУ. Массив ячеек памяти внутри

ИМС организован в виде квадрата со

сторонами, равными 27=128. Общая

емкость равна 128·128=214=16384 однобитных

ячеек, т.е. 16 Кбит.

Адресация ячеек памяти через 7 расположенных на корпусе ИМС ножек ША проводится в два такта:

-

сначала вводятся младшие 7 разрядов

AL=A0…A7 адреса, которые стробируются

срезом сигнала

![]() (строки квадратного массива памяти) и

запоминаются в семи младших битах

внутреннего 14-разрядного регистра

адреса;

(строки квадратного массива памяти) и

запоминаются в семи младших битах

внутреннего 14-разрядного регистра

адреса;

- затем вводятся старшие 7 разрядов

AН=A8…A13 адреса, которые стробируются

срезом сигнала

затем вводятся старшие 7 разрядов

AН=A8…A13 адреса, которые стробируются

срезом сигнала

![]() (столбца квадратного массива памяти),

но запоминается уже в семи старших битах

внутреннего 14-разрядного регистра

адреса.

(столбца квадратного массива памяти),

но запоминается уже в семи старших битах

внутреннего 14-разрядного регистра

адреса.

Далее

режим чтения или записи зависит от

значения сигнала на входе

![]() ,

как показано на диаграммах сигналов на

рис.1.11.

,

как показано на диаграммах сигналов на

рис.1.11.

В

момент прохождения среза сигнала

![]() происходит регенерация ячеек строки

массива памяти, организованного

квадратом. При регенерации напряжение

на запоминающих конденсаторах ячеек

памяти ИМС восстанавливается до

номинального уровня. Следовательно,

при всяком обращении к ОЗУ происходит

автоматически регенерация всей строки,

в которой расположена адресуемая ячейка.

Для данной ИМС регенерация должна

проходить через каждые 2 мс. Для

гарантированной регенерации всех ячеек

динамического ОЗУ производится

принудительная регенерация, путем

обращения к строкам (активизацией

сигнала

происходит регенерация ячеек строки

массива памяти, организованного

квадратом. При регенерации напряжение

на запоминающих конденсаторах ячеек

памяти ИМС восстанавливается до

номинального уровня. Следовательно,

при всяком обращении к ОЗУ происходит

автоматически регенерация всей строки,

в которой расположена адресуемая ячейка.

Для данной ИМС регенерация должна

проходить через каждые 2 мс. Для

гарантированной регенерации всех ячеек

динамического ОЗУ производится

принудительная регенерация, путем

обращения к строкам (активизацией

сигнала

![]() )

через интервалы времени, не превышающие

2 мс.

)

через интервалы времени, не превышающие

2 мс.

Динамические ОЗУ обладают большой емкостью, но требуют специального контроллера, управляющего регенерацией и считыванием/записью при использовании тех же сигналов, которые обеспечивают взаимодействие микропроцессора и ИМС статических ОЗУ, ИМС ПЗУ, внешних устройств.