- •Індивідуальне завдання

- •Анотація

- •Розробка криптопротоколу

- •Узагальнений опис криптопротоколу

- •Алгоритм блокового шифрування rc6

- •Алгоритм формування підключів

- •Алгоритм зашифрування даних

- •Розробка детального алгоритму реалізації криптопротоколу

- •Аналіз криптопротоколу

- •Постулати і правила ban-логіки

- •Аналіз криптопротоколу з використанням ban-логіки

- •РoЗробка структури спеціалізованого процесора

- •Визначення набору функцій, що реалізує спеціалізований процесор

- •Розробка структурної схеми спеціалізованого процесора

- •Визначення технічних характеристик спеціалізованого процесора

- •Розробка програми

- •Розробка структури програми

- •Результати тестування програми

- •Висновки

- •Список використаних джерел

- •Функція зашифрування

- •Функція розшифрування

- •Функція зняття мітки часу

-

Розробка структурної схеми спеціалізованого процесора

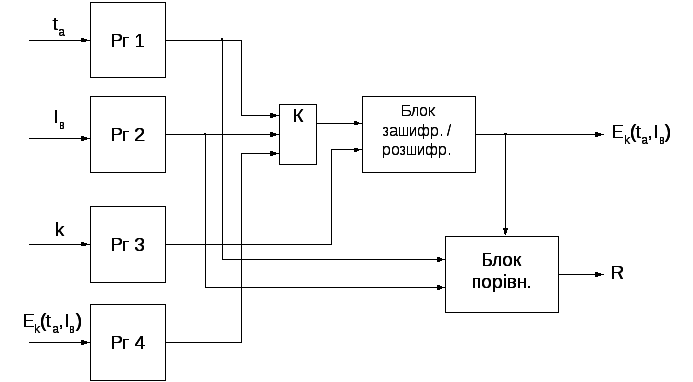

Для побудови структурної схеми спеціалізованого процесора скористаємось канонічним методом синтезу. Згідно з цим методом кожному математичному елементу наведених множин поставлено у відповідність структурний елемент. Схема спеціалізованого процесора має такий вигляд (рис. 2).

Рисунок 2 – Схема

спеціалізованого процесора для реалізації

протоколу

Рисунок 2 – Схема

спеціалізованого процесора для реалізації

протоколу

На вході

у нас знаходяться три регістри Рг1, Рг2,

Рг3, що складають згенеровану мітку часу

![]() ,

ідентифікатор сторони В

,

ідентифікатор сторони В

![]() та відкритий ключ k.

Блок К на даній схемі представляє собою

мультиплексор(комутатор).

Сторона А зашифровує

та відкритий ключ k.

Блок К на даній схемі представляє собою

мультиплексор(комутатор).

Сторона А зашифровує

![]() і

і

![]() і отримує зашифрване повідомлення

і отримує зашифрване повідомлення

![]() ,

що записується в регістр Рг4, потім

відправляє сформоване повідомлення

стороні В. Сторона В розшифровує

повідомлення і отримує ідентифікатор

,

що записується в регістр Рг4, потім

відправляє сформоване повідомлення

стороні В. Сторона В розшифровує

повідомлення і отримує ідентифікатор

![]() ,

мітку часу сторони А

,

мітку часу сторони А

![]() і генерує свою мітку чаусу

і генерує свою мітку чаусу

![]() .

Після розшифрування порівнюються мітки

часу кожної сторони та ідентифікатори

і отримується відповідний результат

автентифікації.

.

Після розшифрування порівнюються мітки

часу кожної сторони та ідентифікатори

і отримується відповідний результат

автентифікації.

Розглянемо блоки, використанні в схемі: блок зашифрування/розшифрування, блок порівняння.

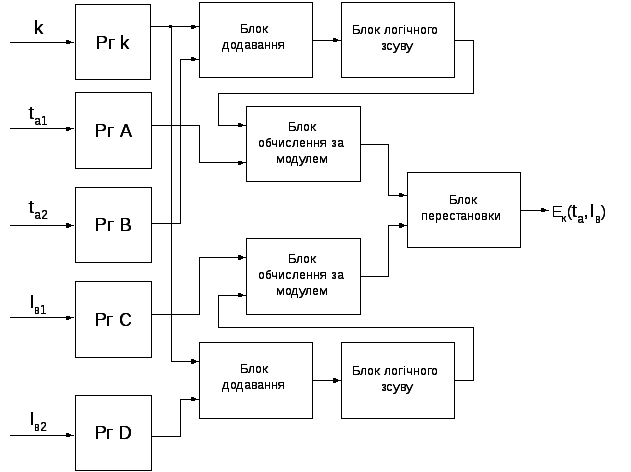

Оскільки в RC6 для зашифрування і розшифрування використовується подібна процедура, тому блоки зашифрування і розшифрування будуть мати наступний вигляд (рис. 3):

Рисунок 3 – Блок зашифрування і розшифрування для алгоритму RC6

Мітка часу

![]() ,

ідентифікатор сторони В

,

ідентифікатор сторони В

![]() .

.

Для зашифрування

та розшифрування отриману мітку часу

![]() та ідентифікатор сторони В

та ідентифікатор сторони В

![]() ,

що становлять наше повідомлення,

розміщуємо в 4 32-розрядні регістри.

,

що становлять наше повідомлення,

розміщуємо в 4 32-розрядні регістри.

Тепер розглянемо окремо кожен блок наведеного алгоритму шифрування.

В блоці додавання

дані з регістра додаються до ключа. Блок

логічного зсуву виконує зсув повідомлення

на

![]() ,

де

,

де

![]() - розрядність регістра рівна 32. Блок

обчислення за модулем обчислює остачу

від ділення вмісту одного регістру на

вміст регістру, отриманого при операції

зсуву. Блок перестановки відповідає за

перестановку регістрів. Детальніше усі

ці дії описані в п.1.2.2.

- розрядність регістра рівна 32. Блок

обчислення за модулем обчислює остачу

від ділення вмісту одного регістру на

вміст регістру, отриманого при операції

зсуву. Блок перестановки відповідає за

перестановку регістрів. Детальніше усі

ці дії описані в п.1.2.2.

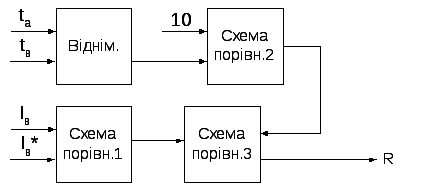

В схемі спеціалізованого процесора використовується блок порівняння. Його структура представлена на рис. 4.

Рисунок 4 – Структура блоку порівняння

Отже сторона А

сформувала мітку часу

![]() ,

згенерувала повідомлення, зашифрувала

його на відкритому ключі

,

згенерувала повідомлення, зашифрувала

його на відкритому ключі

![]() і відправила стороні В. Сторона В отримала

зашифроване повідомлення, потім

розшифрувала його на відкритому ключі

і відправила стороні В. Сторона В отримала

зашифроване повідомлення, потім

розшифрувала його на відкритому ключі

![]() ,

отримала мітку часу сторони А

,

отримала мітку часу сторони А

![]() ,

ідентифікатор

,

ідентифікатор

![]() і згенерувала свою мітку часу

і згенерувала свою мітку часу

![]() .

Стороні В на отримання і розшифрування

повідомлення виділялось 10 с, якщо вона

вклалась в заданий час і ідентифікатори

.

Стороні В на отримання і розшифрування

повідомлення виділялось 10 с, якщо вона

вклалась в заданий час і ідентифікатори

![]() та

та

![]() однакові, то автентифікація пройдена

успішно.

однакові, то автентифікація пройдена

успішно.

-

Визначення технічних характеристик спеціалізованого процесора

Для розробленого процесора визначимо такі технічні характеристики:

-

час реалізації криптопротоколу;

-

складність апаратури для обчислень;

-

ємність пам’яті.

Час реалізації криптопротоколу будемо визначати в таких умовних одиницях:

-

час додавання за модулем 232 – tдод;

-

час зсуву на один двійковий розряд – tзс;

-

час виконання однієї логічної операції – tлог.

Час реалізації криптопротоколу (t) – це час, який потрібен для виконання зашифрування та розшифрування даних. Оскільки алгоритм розшифрування для шифру RC6 передбачає виконання тих самих дій, що й при зашифруванні але у зворотному порядку то фактично час реалізації криптопротоколу – час, який потрібен для дворазового виконання операції зашифрування даних.

Процес зашифрування можна розділити на дві частини: перетворення ключової інформації (час – tk) та безпосередньо зашифрування даних(час – tc).

Розрядність всіх чисел будемо вважати рівною 128, тобто 4 машинних слова.

Отже, маємо:

tk =9∙ tдод+10∙5 tдод+10∙2 tзс=59 tдод+20 tзс

tc=4 tдод+9∙(4 tзс+2 tлог+2 tдод)=22 tдод+18 tлог+36 tзс

Враховуючи отримані дані розрахуємо час реалізації всього криптопротоклу:

t= tk+ tc=59 tдод +20 tзс +22 tдод +18 tлог +36 tзс=81 tдод +56 tзс +18 tлог

Розрахуємо

складність апаратури для обчислень.

Отже, для процесора

потрібно чотири 128-розрядних

регістрів та два комутуємих

зв’язка мультиплексора

. Тому складність апаратури

![]() розрядів регістра.

розрядів регістра.