- •Математичні основи цифрової техніки

- •Відображення інформації у цифровій техніці

- •Перетворення числової інформації

- •Двійкова арифметика

- •Основні поняття та закони бульової алгебри

- •Властивості логічних функцій

- •Форми зображення логічних функцій

- •Мінімізація логічних функцій

- •Структурна реалізація логічних функцій

- •Загальні відомості про цифрові автомати

- •Різновиди цифрових автоматів та особливості їх функціонування

- •Загальні питання синтезу цифрових автоматів

- •Схемотехніка цифрових елементів

- •Види цифрових сигналів, та способи їх передачі

- •Класифікація цифрових елементів

- •Основні характеристики та параметри цифрових мікросхем

- •Порівняльні характеристики цифрових мікросхем

- •Схеми логічних елементів

- •Елементи з розширеними функціональними можливостями

- •Cинтезовані логічні елементи

- •Логічні елементи з відкритим колектором

- •Тристановий драйвер

- •Інтерфейсні мікросхеми

- •Узгоджувачі рівнів

- •Завадостійкість цифрових пристроїв

- •Імпульсні схеми на цифрових елементах

- •Формувачі

- •Генератори

- •Пристрої для перетворення цифрової інформації

- •Шифратори та дешифратори

- •Мультиплексори та демультиплексори

- •Синтез комбінаційних пристроїв на дешифраторах

- •Синтез комбінаційних пристроїв на мультиплексорах

- •Перетворювачі кодів

- •Арифметичні пристрої

- •Арифметичні суматори

- •Цифрові компаратори

- •Арифметико-логічні пристрої

- •Програмовані логічні матриці

- •Контрольні запитання по розділу

- •Послідовнісні пристрої

- •Особливості функціонування послідовнісних пристроїв

- •Особливості синтезу послідовнісних пристроїв

- •Тригер – найпростіший зaпам’ятовувальний пристрій

- •Загальна структура та класифікація тригерів

- •Рiзновиди тригерів

- •Регістри

- •Регістри пам’яті

- •Регістри зсуву

- •Лічильники

- •Класифікація лічильників

- •Лічильники з послідовним переносом

- •Реверсивні лічильники

- •Лічильники з довільним модулем лічби

- •Кільцеві лічильники та лічильники Джонсона

- •Контрольні запитання по розділу

- •Інтегральні запам'ятовувальні пристрої

- •Загальні відомості

- •Оперативні запам'ятовуючі пристрої

- •Статичні запам'ятовувачі віс озп

- •Динамічні запам'ятовувачі віс озп

- •Принцип побудови і структура віс озп

- •Принцип побудови і структура пзп

- •Електрично перепрограмовувані пзп

-

Регістри

Регістром називається послідовнісний пристрій, що призначений для приймання, запам’ятовування, перетворення і передачі двійкової iнформації. Регістри можуть використовуватися також для виконання деяких логічних перетворень. У загальному випадку регістр - це блок тригерів i ЛЕ одного типу, що певним чином з’єднані між собою. Введення /запис/ інформації у регістр i зняття /зчитування/ інформації з нього залежать від способу і характеру цих з’єднань. Тому можливих способів приймання і передачі слів може бути чотири:

-

з послідовними входом і виходом - регістр типу SISO (S - від англ. Serial);

-

з послідовним входом і паралельним виходом - регістр типу SIРО (Р - від англ. Раrаllel);

-

з паралельним входом i послідовним виходом - регістр типу РІSО ;

-

з паралельними входом i виходом - регістр типу РІРО;

Регістр типу SISO призначений для послідовного біт за бітом виконання операцій запису і зчитування n-розрядного слова. Такий регістр ще називають регістром зсуву. Регістр типу SІРО завантажується послідовно біт за бітом, а видає записану інформацію одночасно з усіх своїх розрядів за один такт синхросигналу. Приймання інформації у регістрі типу РІSО здійснюється одночасно по всіх розрядах слова за один такт керування, а зчитування - послідовно. Найбільш швидкодіючим очевидно, є регістр РІРО бо і запис, і зчитування слова у нього відбуваються одночасно і незалежно. Такий регістр називають регістром пам’яті.

Розрядність будь-якого регістра визначається числом тригерів, кожний з яких як двостановий запам’ятовувач одного розряду слова відповідає за введення, збереження і виведення-1 біт iнформації. Регістри можуть відрізнятись між собою за кількістю тактів керування, що необхідні для виконання конкретних операцій. Тому за способом тактування розрізняють одно-, дво- або багатотaктні регістри. Для керування однотактним регістром досить однієї послідовності синхросигнaлів, багатотактним - кількох. Операції встановлення регістра у початковий стан, приймання інформації з одного пристрою i передача її в інший пристрій, зсув слова вліво або вправо, реалізуються за допомогою комбінаційної схеми регістра.

Регістри належать до найбільш поширених функціональних вузлів. Крім зберігання інформації, її зсуву тa зчитування, які необхідні для виконання різних арифметичних та логічних операцій над двійковими числами, за допомогою регістрів можна також перетворювати інформацію з одного виду в інший, наприклад, послідовного коду у паралельний або навпаки тощо.

-

Регістри пам’яті

Цe накопичувальні регістри - пристрої в паралельним записом та зчитуванням слова, типу РІРО. Їх основне призначення – зберігання двійкової інформації невеликого об’єму (не більше 2 байт), що подана у паралельному коді. Регістри пам’яті можуть бути синхронізовані рівнем (дозволом С=1) або фронтом, чи зрізом синхросигналу залежно від типу застосованих тригерiв.

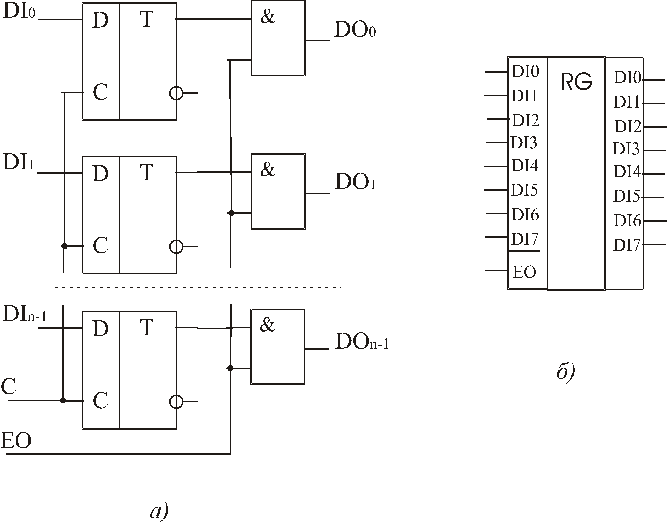

На рис.4.10.а показана схема n-розрядного регістра пам’яті, що побудований на синхронних D-тригерах, та кон’юнкторах на ЛЕ, що виконують функцію збігу. Інформація у вигляді паралельного коду двійкових чисел {DIn-1…DI1,DI0} заноситься по вхідній шині і записується у регістрі тільки при наявності дозволяючого рівня С=1. Зчитування інформації з регістра можливе тільки при наявності на входах схем збігу дозволяючих рівнів, тобто при ЕО=1.

Рис. 4.53 Структура (а) та позначення (б) регістра пам’яті

На рис.4.10.б показане схематичне позначення 8-ми розрядного регістра пам’яті.

У випадку

побудови регістра пам’яті на RS -тригерах

у схемі потрібно передбачити попереднє

"очищення" регістра тобто встановлення

всіх тригерів у стан нуль, що здійснюється

за допомогою входу скидання R. Попереднє

встановлення тригерів в нуль вимагає

додаткового часу, то зменшує швидкодію

регістра. Для збільшення швидкодії

таких регістрів пам'яті застосовують

парафазну передачу для перезапису

iнформації з регістрa в регістр. Для

цього використовують обидва входи RS

-тригерів, по яких одночасно подають

сигнали

![]() ,

та

,

та

![]() . Розрядність регістрів пвм’ятi

нарощується збільшенням потрібного

числа тригерів, тактові входи яких

приєднують до шини синхронізації С.

. Розрядність регістрів пвм’ятi

нарощується збільшенням потрібного

числа тригерів, тактові входи яких

приєднують до шини синхронізації С.