- •Математичні основи цифрової техніки

- •Відображення інформації у цифровій техніці

- •Перетворення числової інформації

- •Двійкова арифметика

- •Основні поняття та закони бульової алгебри

- •Властивості логічних функцій

- •Форми зображення логічних функцій

- •Мінімізація логічних функцій

- •Структурна реалізація логічних функцій

- •Загальні відомості про цифрові автомати

- •Різновиди цифрових автоматів та особливості їх функціонування

- •Загальні питання синтезу цифрових автоматів

- •Схемотехніка цифрових елементів

- •Види цифрових сигналів, та способи їх передачі

- •Класифікація цифрових елементів

- •Основні характеристики та параметри цифрових мікросхем

- •Порівняльні характеристики цифрових мікросхем

- •Схеми логічних елементів

- •Елементи з розширеними функціональними можливостями

- •Cинтезовані логічні елементи

- •Логічні елементи з відкритим колектором

- •Тристановий драйвер

- •Інтерфейсні мікросхеми

- •Узгоджувачі рівнів

- •Завадостійкість цифрових пристроїв

- •Імпульсні схеми на цифрових елементах

- •Формувачі

- •Генератори

- •Пристрої для перетворення цифрової інформації

- •Шифратори та дешифратори

- •Мультиплексори та демультиплексори

- •Синтез комбінаційних пристроїв на дешифраторах

- •Синтез комбінаційних пристроїв на мультиплексорах

- •Перетворювачі кодів

- •Арифметичні пристрої

- •Арифметичні суматори

- •Цифрові компаратори

- •Арифметико-логічні пристрої

- •Програмовані логічні матриці

- •Контрольні запитання по розділу

- •Послідовнісні пристрої

- •Особливості функціонування послідовнісних пристроїв

- •Особливості синтезу послідовнісних пристроїв

- •Тригер – найпростіший зaпам’ятовувальний пристрій

- •Загальна структура та класифікація тригерів

- •Рiзновиди тригерів

- •Регістри

- •Регістри пам’яті

- •Регістри зсуву

- •Лічильники

- •Класифікація лічильників

- •Лічильники з послідовним переносом

- •Реверсивні лічильники

- •Лічильники з довільним модулем лічби

- •Кільцеві лічильники та лічильники Джонсона

- •Контрольні запитання по розділу

- •Інтегральні запам'ятовувальні пристрої

- •Загальні відомості

- •Оперативні запам'ятовуючі пристрої

- •Статичні запам'ятовувачі віс озп

- •Динамічні запам'ятовувачі віс озп

- •Принцип побудови і структура віс озп

- •Принцип побудови і структура пзп

- •Електрично перепрограмовувані пзп

-

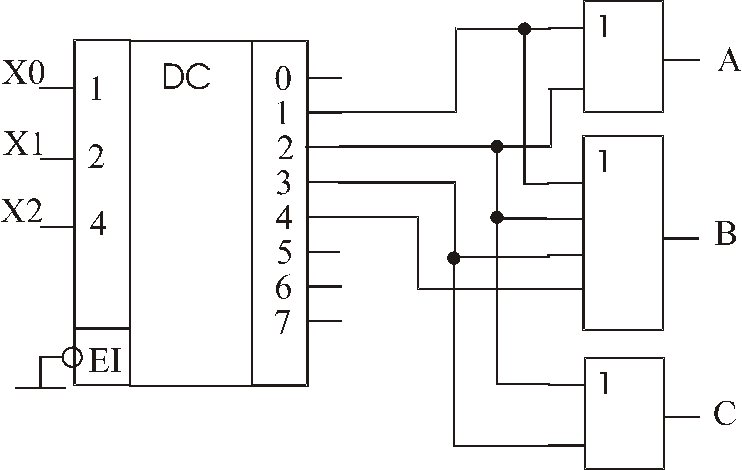

Синтез комбінаційних пристроїв на дешифраторах

Дешифратори зручно використовувати в тих випадках, коли потрібно сформувати деяку кількість взаємно синхронізованих сигналів, або в загальному реалізувати деяку систему логічних функцій. При цьому дешифратор використовується у вигляді постійного запам’ятовувального пристрою (ПЗП), в якому містяться задані логічні функції. Для того, щоб детальніше зрозуміти вищесказане, розглянемо приклад. Нехай слід розробити цифрових пристрій, на вхід якого надходить циклічна двійкова послідовність Х: (0,1,2,3,4,5,0,1,2,3,4,5... і т.д.). У відповідь на це, розроблюваний пристрій повинен генерувати три синхронні послідовності, які в часовій формі виглядатимуть так (див. рис.3.7):

Рис. 3.33 Генеровані цифровим пристроєм сигнали

Система логічних функцій роботи даного пристрою матиме вигляд:

(

3.0 )

(

3.0 )

Якщо подивитись на систему логічних функцій дешифратора (3.2), то стає зрозумілим, що там зустрічаються всі можливі терми системи (3.6). Залишається тільки об’єднати необхідні з них за допомогою зовнішніх диз’юнкторів. Схематично це буде мати наступний вигляд (див.рис.3.8):

Рис. 3.34 Схема генератора сигналів представлених на рис.3.7

В іншій інтерпретації, робота пристрою може бути представлена так: сигнали Х надходять на вхід дешифратора послідовно, тому моменти часу 0,1,2,3,4,5 мають свої відповідні кодові послідовності, які на виході дешифратора перетворюються на сигнал "біжучої" в часі одиниці. Цей сигнал надходить на входи ЛЕ "АБО", які і формують відповідні вихідні сигнали.

-

Синтез комбінаційних пристроїв на мультиплексорах

Комбінаційні

пристрої на мультиплексорах дозволяють

реалізувати довільні логічні функції,

і подібно до КП на дешифраторах,

забезпечують зменшення кількості

корпусів ІС на платі цифрового притсрою.

Синтез КП на мультиплексорах полягає

в тому, що задавши інформаційним входом

лог.0 або лог.1 можна виключити або

включити в логічну функцію той чи інший

мінтерм, який визначається адресним

кодом. Тому мультиплексор зручно

застосовувати для реалізації довільної

функції

![]() змінних, що подана в УДНФ. Оскільки вихід

в мультиплексора один, то й логічну

функцію можна реалізувати на ньому

одну. Для реалізації системи логічних

функцій слід використати каскадування

декількох мультиплексорів. Методику

синтезу розглянемо на прикладі.

змінних, що подана в УДНФ. Оскільки вихід

в мультиплексора один, то й логічну

функцію можна реалізувати на ньому

одну. Для реалізації системи логічних

функцій слід використати каскадування

декількох мультиплексорів. Методику

синтезу розглянемо на прикладі.

-

Нехай слід розробити пристрій, на вхід якого надходить циклічна двійкова послідовність Х: (0,1,2,3,4,5,6,7... і т.д.). У відповідь на це, пристрій повинен генерувати кодову послідовність (01110010). Для цього зручно застосувати мультиплексор 8-1, інформаційні входи якого потрібно з’єднати з однойменними розрядами даного коду, як це показано на рис.3.9

Рис. 3.35 Генератор кодової послідовності на мультиплексорі 8-1

Робота даного пристрою відбувається наступним чином: на адресні входи надходить двійкова послідовність Х: (0,1,2,3,4,5,6,7... ), що спричиняє послідовне під’єднання до виходу Y входів D0,D1,D2..., і як наслідок, на виході з’являється кодова послідовність "запрограмована" за допомогою подачі на ці входи лог.0 та лог.1.