- •Математичні основи цифрової техніки

- •Відображення інформації у цифровій техніці

- •Перетворення числової інформації

- •Двійкова арифметика

- •Основні поняття та закони бульової алгебри

- •Властивості логічних функцій

- •Форми зображення логічних функцій

- •Мінімізація логічних функцій

- •Структурна реалізація логічних функцій

- •Загальні відомості про цифрові автомати

- •Різновиди цифрових автоматів та особливості їх функціонування

- •Загальні питання синтезу цифрових автоматів

- •Схемотехніка цифрових елементів

- •Види цифрових сигналів, та способи їх передачі

- •Класифікація цифрових елементів

- •Основні характеристики та параметри цифрових мікросхем

- •Порівняльні характеристики цифрових мікросхем

- •Схеми логічних елементів

- •Елементи з розширеними функціональними можливостями

- •Cинтезовані логічні елементи

- •Логічні елементи з відкритим колектором

- •Тристановий драйвер

- •Інтерфейсні мікросхеми

- •Узгоджувачі рівнів

- •Завадостійкість цифрових пристроїв

- •Імпульсні схеми на цифрових елементах

- •Формувачі

- •Генератори

- •Пристрої для перетворення цифрової інформації

- •Шифратори та дешифратори

- •Мультиплексори та демультиплексори

- •Синтез комбінаційних пристроїв на дешифраторах

- •Синтез комбінаційних пристроїв на мультиплексорах

- •Перетворювачі кодів

- •Арифметичні пристрої

- •Арифметичні суматори

- •Цифрові компаратори

- •Арифметико-логічні пристрої

- •Програмовані логічні матриці

- •Контрольні запитання по розділу

- •Послідовнісні пристрої

- •Особливості функціонування послідовнісних пристроїв

- •Особливості синтезу послідовнісних пристроїв

- •Тригер – найпростіший зaпам’ятовувальний пристрій

- •Загальна структура та класифікація тригерів

- •Рiзновиди тригерів

- •Регістри

- •Регістри пам’яті

- •Регістри зсуву

- •Лічильники

- •Класифікація лічильників

- •Лічильники з послідовним переносом

- •Реверсивні лічильники

- •Лічильники з довільним модулем лічби

- •Кільцеві лічильники та лічильники Джонсона

- •Контрольні запитання по розділу

- •Інтегральні запам'ятовувальні пристрої

- •Загальні відомості

- •Оперативні запам'ятовуючі пристрої

- •Статичні запам'ятовувачі віс озп

- •Динамічні запам'ятовувачі віс озп

- •Принцип побудови і структура віс озп

- •Принцип побудови і структура пзп

- •Електрично перепрограмовувані пзп

-

Схеми логічних елементів

Т

Рис. 2.6 Логічний елемент

"НЕ" ТТЛ

Широкого

розповсюдження набули типи ЛЕ виконані

на польових структурах

(метал-діелектрик-напівпровідник, МДН).

Основна особливість мікросхем цих

елементів є незначне споживання вхідного

струму в статичному режимі (![]() мкА).

Основним недоліком до останнього часу

була низька швидкодія (<3МГц), однак на

сучасному рівні розвитку наявні КМОН

серії ІС з швидкістю перемикання сигналу

до 80МГц.

мкА).

Основним недоліком до останнього часу

була низька швидкодія (<3МГц), однак на

сучасному рівні розвитку наявні КМОН

серії ІС з швидкістю перемикання сигналу

до 80МГц.

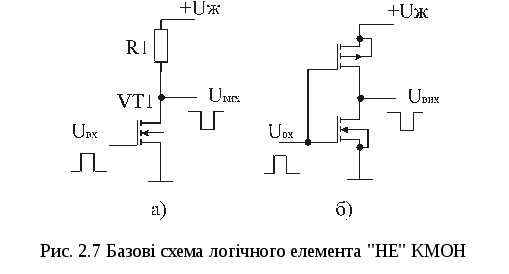

На рис.2.5 а) показана базова схема МОН інвертора з резистором навантаження, а на рис.2.5 б) інвертор на парі МОН транзисторів різних каналів, тобто комплементарних МОН транзисторах (КМОН). Особливість роботи таких транзисторів дозволяє обійтися у схемі без фазорозщеплюючого транзистора, і тим самим спрощує схему. Основним недоліком таких схем є їхня чутливість до статичної електрики, що спричиняє їх вихід з ладу. Тому при роботі з КМОН ІС слід користуватись антистатичним браслетом, та заземлити жало паяльника. Самі ж мікросхеми (як, до речі і польові транзистори) слід транспортувати загорнутими у фольгу або в спеціальних антистатичних футлярах.

До елементної бази надвисокої швидкодії належать ЛЕ емітерно-зв’язаної логіки (ЕЗЛ). Базовою схемою ЕЗЛ є струмовий ключ, побудований за схемою диференційного підсилювача, наведений на рис. 2.6. Така схема може виконувати роль інвертора та буферного повторювача вхідного логічного сигналу.

Рис. 2.8 Струмовий ключ ЕЗЛ

Поріг

перемикання струмового ключа задається

зовнішньою опорною напругою

![]() ,

яка формується спеціальною схемою

R3,R5,R6,VT3.

Вихідні емітерні повторювачі забезпечують

високу навантажувальну здатність по

струму (до Кроз=15). В серійних ЛЕ

ЕЗЛ колекторні кола заземляють, а

емітерні під’єднують до від’ємної

напруги живлення, що підвищує

завадостійкість схеми. Залежно від

способу кодування вхідного сигналу,

тобто від того, який рівень напруги

вважати лог.0 або лог.1 ЕЗЛ схема може

виконувати різні операції. Для

збільшення кількості входів струмового

ключа до VT1 паралельно (колектор до

колектора, емітер до емітера) під’єднують

додаткові біполярні транзистори, при

чому кількість базових входів схеми

збільшується. Належність до тої чи

іншої логіки визначається взятим рівнем

,

яка формується спеціальною схемою

R3,R5,R6,VT3.

Вихідні емітерні повторювачі забезпечують

високу навантажувальну здатність по

струму (до Кроз=15). В серійних ЛЕ

ЕЗЛ колекторні кола заземляють, а

емітерні під’єднують до від’ємної

напруги живлення, що підвищує

завадостійкість схеми. Залежно від

способу кодування вхідного сигналу,

тобто від того, який рівень напруги

вважати лог.0 або лог.1 ЕЗЛ схема може

виконувати різні операції. Для

збільшення кількості входів струмового

ключа до VT1 паралельно (колектор до

колектора, емітер до емітера) під’єднують

додаткові біполярні транзистори, при

чому кількість базових входів схеми

збільшується. Належність до тої чи

іншої логіки визначається взятим рівнем

![]() відносно рівня

відносно рівня

![]() .

Якщо за лог.0 взяти рівень

.

Якщо за лог.0 взяти рівень

![]() ,

що лежить нижче від рівня

,

що лежить нижче від рівня

![]() ,

а за лог.1 рівень

,

а за лог.1 рівень

![]() ,

що лежить вище

,

що лежить вище

![]() -

одержимо функціонування схеми в

позитивній логіці. Двовходовий

варіант такої схеми реалізує функції

АБО та АБО-НЕ в залежності від вибору

виходу, з якого знімається сигнал. Інший

вибір напруг, призводить до функціонування

схеми в негативній логіці, тоді

схема реалізує функції І та І‑НЕ. Для

того, щоб глибше розібратись з особливістю

функціонування такої схеми, слід

дослідити роботу двовходового варіанту

такої схеми в MicroCAP.

-

одержимо функціонування схеми в

позитивній логіці. Двовходовий

варіант такої схеми реалізує функції

АБО та АБО-НЕ в залежності від вибору

виходу, з якого знімається сигнал. Інший

вибір напруг, призводить до функціонування

схеми в негативній логіці, тоді

схема реалізує функції І та І‑НЕ. Для

того, щоб глибше розібратись з особливістю

функціонування такої схеми, слід

дослідити роботу двовходового варіанту

такої схеми в MicroCAP.