- •Учебно-методический комплекс по дисциплине «Вычислительные машины, системы и сети»

- •Содержание

- •Введение

- •Министерство образования росийской федерации

- •-Государственный образовательный стандарт высшего профессионального

- •Информатика , Физика , Высшая математика , Математическое моделирование в

- •Основываясь на этих знаниях , дисциплина «Вычислительные машины , системы и сети

- •В результате изучения дисциплины студент должен знать

- •2.4Наименование и краткое содержание тем практических занятий

- •2.5 Наименование и краткое содержание тем лабораторных занятий

- •Учебно-методические материалы по дисциплине

- •Методические рекомендации по изучению дисциплины

- •Советы по планированию и организации времени, необходимого на изучение дисциплины:

- •Описание последовательности действий студента, или "сценарий изучения дисциплины"

- •Рекомендации по использованию материалов учебно-методического комплекса

- •Рекомендации по работе с литературой

- •Советы по подготовке к экзамену, критерии экзаменационных (зачетных) оценок

- •Разъяснения по поводу работы с тестовой системой курса

- •6.1.Типы процессоров, классификация.

- •Стандартные значения адресов и irq для com – портов приведены в таблице 2.2.

- •8.3.Работа с параллельным портом (lpt)

- •Лекция 10. Структура элементов памяти

- •10.1. Иерархия устройств памяти Принято все элементы памяти используемые в

- •1Какую роль играют буферные схемы в организации обмена данными и командами в современной эвм?

- •Лекция 11 принципы записи информации на магнитные носители

- •11.1.Взу. Спектр решений.

- •Вопросы для самопроверки

- •14.1. Архитектурные принципы Фон Неймана

- •14.2. Альтернативные структуры

- •Коды с повторением. Один символ передается несколькими (нечетным числом). Декодер по принятой комбинации определяет 0 или 1.

- •Вопросы для самопроверки

- •Лекция 21.Сети передачи данных

- •21.3.Одноранговые сети

- •Список использованной литературы

- •Цели и задачи курсового проекта

- •Содержание курсовой работы

- •Разработка технического задания.

- •Разработка схемы устройства

- •Структурная схема устройства.

- •Функциональная схема устройства.

- •Проверочные расчеты.

- •2.4.1. Расчет на потребляемую мощность.

- •Расчет на нагрузочную способность элементов.

- •Расчет на задержку формирования сигнала.

- •Программная часть

- •Разработка программы.

- •Текст программы

- •Литература по курсовому проекту

- •Список тем

- •Билеты по курсу эвм и вс для специальности уитс

- •Глоссарий

6.1.Типы процессоров, классификация.

Со времени появления микропроцессоров их структура и возможности значительно изменились. Первые микропроцессоры были разработаны для устройств автоматического управления, но не для вычислителей. Отсюда появление множества новых фирм, которые занимались разработкой вычислителей на первых микропроцессорах. Но с увеличением интеграции появилась возможность разработки кристаллов, структура которых была близка к процессорам универсальных ЭВМ. Дальнейшее увеличение интеграции привело к появлению целых групп различных процессоров:

1) арифметические процессоры, ориентированные на выполнение команд длинной арифметики.

2) многокристальные процессоры, когда в один корпус вставляли 2-3 кристалла, выполняющих функции основного процессора, памяти, сопроцессора.

3) микроконтроллеры – схемы с архитектурой процессора, но интегрированные в один кристалл – однокристальные микроЭВМ. 4) транспьютеры – кристаллы, работающие в структурах

однородных вычислительных сред.

5) секционированные микропроцессоры и специализированные схемы.

Каждое из этих направлений имеет свою область применения, решает свои задачи. Более того, внутри каждого направления существует деление: а) по разрядности схем (2,4,8,16,32) б) по потребляемой мощности в) по системе команд микропроцессора и т.д. Любая классификация преследует цель – полнее показать варианты изделия, опираясь на признак.

6.2 Микропроцессоры, микроконтроллеры

Составляют большую группу ЦФУ, использующих последовательный принцип обработки. В основе микроконтроллера – большая ИМС микроконтроллера. На сегодня выделяется три вида таких схем: 1) однокристальные микропроцессоры с разрядностью 8-16 (ОМП) 2) однокристальные микроЭВМ 8 разрядов 3) PIC контроллеры.

Первоначально контроллеры строились на основе ОМП. Это традиционный подход. Первые МП предназначались для контроллеров. С увеличением интеграции во многих применяемых ОМП начали заменятся на однокристальные микроЭВМ. И на сегодняшний день микроЭВМ – основной тип интегральных схем в контроллерах.

PIC контроллеры используют несколько иную структуру. Они ориентированы по алгоритмам на преобразование протоколов следования входных сигналов.

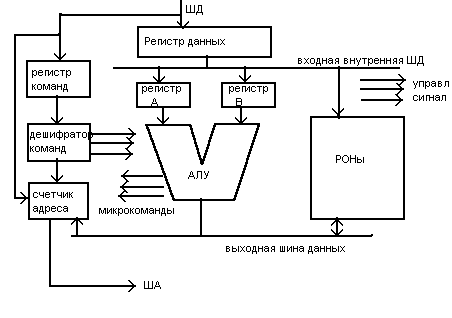

П рограммная

структура однокристального микропроцессора

(8 разрядов)

рограммная

структура однокристального микропроцессора

(8 разрядов)

Основа схемы - двухвходовое АЛУ. Операнды фиксируются перед АЛУ в промежуточных регистрах А и В. необходимость в них выравнивание во времени появления операндов. Сигнал с выхода АЛУ через внутренний выход ШД поступает в РОН. Количество и разрядность РОНов изменяется 8-16. Их количество определяется числом разрядов в коде команды прямой регистровой адресации (3-4). Разрядность одинарной длины 8 или двойной – 16. РОНы связаны внутри входной ШД, через которую сигнал поступает в регистр промежуточного хранения или регистр данных. Входные сигналы через ШД фиксируется регистр. Далее поступая в промежуточный регистр. Код команды КОП запоминается регистром команд, после чего устройство управления с помощью тактовых сигналов преобразует код команды в микрокоманду, управляющей внутренним коммутатором схемы. Счетчик адреса формирует адрес на ША по сигналам микрокоманды, при имеется возможность занесение входного сигнала непосредственно в счетчик. Для косвенной адресации необходимо занесение в счетчик адреса содержимого РОНа. При выполнении любой операции, АЛУ формирует признаки (флаги), которые фиксируются регистре признаков. Схема не только обрабатывает операнды, но и формирует управляющие сигналы для работы внешних блоков.

Главной особенностью микропроцессора является наличие внутренней входной и выходной ШД. Эти шины отделяют микропроцессоры от других БИС.

Примеры ОМП, используемых в микроконтроллерах микроЭВМ.

семейство микропроцессоров К580ВМ80, кроме 8 разрядного. Аналог Intel 8080. Рекомендуют в качестве памяти использовать типовые схемы ОЗУ (серии К565 РУХХ, К541РУХХ), ПЗУ – К556РТХХ

этой схемы Intel 8085 соответствует К1821ВМ85, Z-80 во многом схема похожа на К 580ВМ, но в ней предусмотрена регенерация памяти (восстановление) и добавлены еще две команды.

Третью группу схем контроллеров – программируемые интегральные контроллеры. Используют не вычислительную структуру для получения сигналов управления. Это позволяет им иметь большую производительность, но требует несколько иного подхода при разработке программного обеспечения- использует не очень простые эмуляторы

6.3. Секционированные микропроцессоры.

Они ориентированы на использование в специализированных вычислителях и контроллерах. Требуемая разрядность устройства получается за счет наращивания разрядности нескольких секций. Например: 16 разрядный вычислитель строится на 4 разрядных секциях. На сегодняшний день наиболее замечательными сериями являются К588ВС1;2 К1804ВС1;2;3

К588ВС – 16 разрядная секция, выполнена КМОП технологии, но ориентирована на применение в вычислителях с системой DEC. Она может использоваться как самостоятельная схема с микропрограммным управлением. КМОП позволяет использовать автономное питание. Схема не требует тактового генератора. В качестве тактового генератора используется 13 разряд микрокоманды. Схема была ориентирована на автономные системы обработки и управления. Совместно с основной схемой разработаны дополнительные ИМС регистры контроллера. Поскольку КМОП не может работать в жестких условиях, разработали ТТЛШ секции. К1802, К1804. Основное назначение – бортовая аппаратура высокой производительности. Секции включают набор дополнительных схем. По распространенности 1804 лучше – в его состав входит комплекты более 10 схем, но в них нет ОЗУ и ПЗУ. Ориентация как и в 580. Помимо серии 1802 и 1804 существуют сверхбыстродействующие К1800ВС1 ЭСЛ 4-разрядная. В состав кроме секций и буферных регистров входит ОЗУ и ПЗУ. Структура секций во многом повторяет ОМП, где отсутствует адресный счетчик и регистр команд. Отсутствует регистр флагов, а дешифратор преобразует микрокоманду в унитарный код. Причина – биполярный, рассеивается больше мощности и что бы кристалл не перегрелся , степень его интеграции не высока.

6.4 Многокристальные микропроцессоры

Первые однокристальные микропроцессоры (микроконтроллеры) мало подходили для организации удобных вычислительных процедур, а именно:

1) Разрядность адреса не высока, разрядность данных (8,16).

2) При необходимости можно было увеличить в 2-4 раза, но это увеличение приводило к большим временным затратам.

3) Сложные арифметические операции выполнялись программно, т.е. нужно время.

4) Неудобная система прерываний. С учетом сказанного микропроцессоры от микроконтроллеров значительно продвинулись в своем развитии, прежде всего, по возможности увеличения адресуемого пространства.

1 )

Первый шаг был сделан за счет введения

адресного сумматора, позволяющего

формировать адрес на ША очень гибким

способом. Адрес формировался как сумма

содержимого нескольких внутренних

регистров процессора: непосредственно

адресного, смещения и сегментного и

базового регистров. Причем последние

складываются в сумматоре после сдвига

в сторону старших на 4. За счет чего

старшие разряды адреса идут, минуя

сумматор. Адрес в ОЗУ может быть изменен

содержанием любого из указанных

регистров, т.е косвенная адресация

позволяла легко перемещаться в адресном

поле за счет только одной команды.

)

Первый шаг был сделан за счет введения

адресного сумматора, позволяющего

формировать адрес на ША очень гибким

способом. Адрес формировался как сумма

содержимого нескольких внутренних

регистров процессора: непосредственно

адресного, смещения и сегментного и

базового регистров. Причем последние

складываются в сумматоре после сдвига

в сторону старших на 4. За счет чего

старшие разряды адреса идут, минуя

сумматор. Адрес в ОЗУ может быть изменен

содержанием любого из указанных

регистров, т.е косвенная адресация

позволяла легко перемещаться в адресном

поле за счет только одной команды.

2) Сложные команды начали выполняться с использованием аппаратных средств. Первые опыты применения арифметических микропроцессоров.

П римеры:

К1810ВМ87 процессор заменяет основной при

выполнении команд деления , умножения,

требующих большого времени. Такие схемы

назывались сопроцессорными. Локальная

шина объединяет ША и ШД двух схем и о

римеры:

К1810ВМ87 процессор заменяет основной при

выполнении команд деления , умножения,

требующих большого времени. Такие схемы

назывались сопроцессорными. Локальная

шина объединяет ША и ШД двух схем и о бщие

сигналы управления при получении кода

длинной команды. Основной процессор

блокируется, операция выполняется

сопроцессором. Это направление получило

распространение в системах требующих

реализации длинных операций.

Специализированные схемы, как правило,

сочетали программную и аппаратную

реализацию, что позволяло выполнять

также операции за несколько тактов

(5-6). Но это направление было оправдано,

если в задачах постоянно встречались

эти операции. В универсальных ВМ они

встречались не столь часто, поэтому в

них арифметический сопроцессор.

Увеличение интеграции позволило

разместить на кристалле большее число

элементов и интегрировать сопроцессор

в основной кристалл, либо сделать

кристалл сопроцессора рядом с основным

кристаллом. Это направление привело

также к введению буферной памяти команд

и данных в структурах микропроцессора.

бщие

сигналы управления при получении кода

длинной команды. Основной процессор

блокируется, операция выполняется

сопроцессором. Это направление получило

распространение в системах требующих

реализации длинных операций.

Специализированные схемы, как правило,

сочетали программную и аппаратную

реализацию, что позволяло выполнять

также операции за несколько тактов

(5-6). Но это направление было оправдано,

если в задачах постоянно встречались

эти операции. В универсальных ВМ они

встречались не столь часто, поэтому в

них арифметический сопроцессор.

Увеличение интеграции позволило

разместить на кристалле большее число

элементов и интегрировать сопроцессор

в основной кристалл, либо сделать

кристалл сопроцессора рядом с основным

кристаллом. Это направление привело

также к введению буферной памяти команд

и данных в структурах микропроцессора.

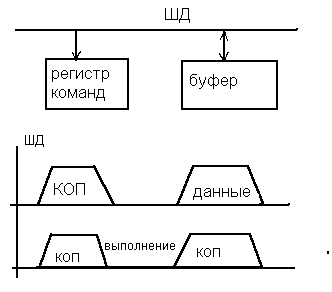

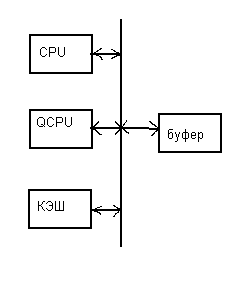

При передаче по ШД КОП и данных немало ситуаций, когда по шине ничего не передается, т.к. процессор выполняет текущую команду. Чтобы повысить производительность, предложено в «свободные окна» на ШД передавать коды следующих команд, расположенных по нарастанию адресов. Но для их хранения на кристалле нужна память, поэтому начали выполнять отдельный третий кристалл «кэш» память. Таким образом, микропроцессор стал состоять минимум из 3 частей. Такая конструкция размещается на посадочном месте в корпусе ИМС и коммутируется между собой локальной шиной в корпусе. Это же идея развита на кристалле основного, где дополнительно РОН выполняется буферная память данных с тем, чтобы снизить число обращений процессора во внешнюю память данных. Т.о. введение в буферной памяти команд и данных позволило заметно повысить производительность схемы. Команды загрузки выполняются традиционно, а процедуры преобразования – данные не выходят на ШД. Буферная память приводит к тому, что программа располагается сегментами. Переход внутри сегментов не проводит к смене содержимого буферной памяти. Выход за пределы сегмента – перезапись нового сегмента в буферную память команд. Разработаны схемы с коротким набором команд RISC микропроцессор. В них введет конвейерный подход к преобразованию. Одновременно несколько команд выполняются в различных фазах. Самая первая команда заканчивается –последняя, начинается. Те же команды разбиты на простые фрагменты.

Первые применения RISC архитектуры совмещались с традиционной. Структура RISC микропроцессоров более регулярна, но устройствам управления – сложнее.

6.5.

Вычислитель на ОМП

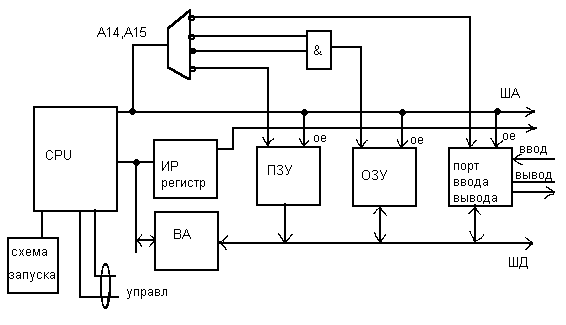

Вариации в структуре вычислителя возможны в организации ША и ШД. Так, например, ША формируется из старших разрядов по ША и младших по ШД. Чтобы адрес сохранялся, дополнительно введен регистр адреса, содержимое которого фиксируется по сигналу синхронизации. ШД сформирована через буфер данных (ВА) и двунаправлена. Управление буфером данных – сигналом запись/чтение процессора. Схемы ОЗУ, ПЗУ, порт In /Out выбираются адресными дешифраторами, поэтому при проектировании структуры все адресное пространство делят на области. Как правило самая большая – ОЗУ. Например: она занимает32К. Это половина из имеющегося адресного пространства. Рекомендуют размещать ее в верхней части карты памяти. При использовании микросхемы ОЗУ с информационной емкостью 16К, чтобы разделить дешифратором, необходимо определить число частей. В простейшем варианте всю область памяти делим на 4 равных части: 16К-ПЗУ, 16К- ПОРТ, 32К – ОЗУ. С этой целью используем дешифратор 2 в 4. На вход дешифратора подаем адресные сигналы А15,А14 – два старших разряда.

-

А14

А15

0

0

ПЗУ

0

1

Порт в/выв

1

0

ОЗУ

1

1

ОЗУ

С соответствующих выходов дешифратора согласно таблице подаем сигналы на входы разрешение выборки кристалла. Для ОЗУ необходима схема И объединяющая два выхода дешифратора. Управляющие сигналы r/w берутся с выхода процессора либо с системного контроллера и подаются на соответствующие входы блоков. Возможна ситуация, когда объем ОЗУ ПЗУ превышает 64К. в этом случае рассматривается два адресных пространства: первое для ОЗУи ПЗУ, второе порты ввода/вывода. Переключение адресных пространств – сигналами контроллера – фаза выборки, чтение/запись и т.д.

В реальных схемах число порто I/Out может быть значительно, поэтому число областей в адресном пространстве 6-10.поэтому можно применить двойной дешифратор. Первый «грубый», у которого один выход обращения к ВУ, второй включается этим выходом и обеспечивает разделение с помощью младших разрядов адреса.

Для ОМП с общей шиной (К1801) необходимо сформировать адресные дешифраторы и адресные регистры на каждом функциональном блоке. Каждый блок имеет на входе адресный регистр с дешифрацией. Если адресное пространство его в регистр записывается – адрес и блок становится активными. Все остальные блоки не выбраны. Однокристальные микроЭВМ имеют в своем составе порты и некоторую память, поэтому структура контроллера отличается лишь блоком процессора. Способы подключения ВУ аналогичны. Контроллер на основе ОМП используют в промышленных системах управления, отображения информации ввода вывода. Их относительная черта – невысокая производительность, при несложных аппаратных затратах.

6.6. Структура на СМП

Основное отличие

этой структуры в том, что процессор

имеет более сложное построение чем в

первом варианте. Это связано с тем, что

необходимо обеспечить работоспособность

секций и связь их между собой. Кроме

этого блок микропрограммного управления

также имеет н емалые

аппаратные затраты. Четыре секции

включены параллельно: младшая, старшая

– по краям, на входе каждой секции

поступает часть разрядов, например по

четыре. Выходные разряды секций также

комплексируются, обеспечивая выходную

разрядность равную входной. ШД формируется

двумя регистрами, входным и выходым.

Причем, выходной регистр должен иметь

третье состояние по выходу. ША формируется

отдельным регистром, причем разрядность

ее зависит от задания и может отличаться

от разрядности шины данных.. Если

разрядность ША<ШД используются младшие

выходные разряды секции, если разрядность

ША>ШД – он выводится из внутренних

регистров секций за два такта, младшие

и старшие части. В секциях нет отдельно

выделенных регистров адреса, поэтому

в качестве адресного применяют один из

РОН-ов каждой секции. Между собою секции

объединяются через выходы сдвиговых

разрядов. Крайние выводы этих разрядов

коммутируются через мультиплексор. С

помощью отдельных разрядов микрокоманды

мультиплексор настаивается на

соответствующий тип сдвига: сдвиг влево

или сдвиг вправо, логический, циклический

или арифметический сдвиги, сдвиги

операндов двойной длины.

емалые

аппаратные затраты. Четыре секции

включены параллельно: младшая, старшая

– по краям, на входе каждой секции

поступает часть разрядов, например по

четыре. Выходные разряды секций также

комплексируются, обеспечивая выходную

разрядность равную входной. ШД формируется

двумя регистрами, входным и выходым.

Причем, выходной регистр должен иметь

третье состояние по выходу. ША формируется

отдельным регистром, причем разрядность

ее зависит от задания и может отличаться

от разрядности шины данных.. Если

разрядность ША<ШД используются младшие

выходные разряды секции, если разрядность

ША>ШД – он выводится из внутренних

регистров секций за два такта, младшие

и старшие части. В секциях нет отдельно

выделенных регистров адреса, поэтому

в качестве адресного применяют один из

РОН-ов каждой секции. Между собою секции

объединяются через выходы сдвиговых

разрядов. Крайние выводы этих разрядов

коммутируются через мультиплексор. С

помощью отдельных разрядов микрокоманды

мультиплексор настаивается на

соответствующий тип сдвига: сдвиг влево

или сдвиг вправо, логический, циклический

или арифметический сдвиги, сдвиги

операндов двойной длины.

Для организации ускоренного переноса используют блок ускоренного переноса (СУП). На ее выходы подключают сигналы распространения и генерации переноса. Выходы СУП – на входной перенос следующей секции. Одна такая схема работает с 4 секциями. Со старшей секцией снимают признаки, причем, признак Z объединяется со всеми секциями. Признаки хранятся в регистре.

Б лок

микропрограммного управления имеет

типовую структуру. Управляющая часть

– форматы микрокоманд распределяется

между регистрами, мультиплексорными

ключами, обеспечивая синхронизацию во

времени. Непосредственно микрокоманды

поступают на каждую секции параллельно.

Одни и те же разряды на каждую секцию.

Это схема позволяет выполнять операции

как над одинарной длины так и над

операндами.

лок

микропрограммного управления имеет

типовую структуру. Управляющая часть

– форматы микрокоманд распределяется

между регистрами, мультиплексорными

ключами, обеспечивая синхронизацию во

времени. Непосредственно микрокоманды

поступают на каждую секции параллельно.

Одни и те же разряды на каждую секцию.

Это схема позволяет выполнять операции

как над одинарной длины так и над

операндами.

Процессорный блок на СМП отличается большей аппаратной сложностью, но позволяет гибко изменять разрядность адреса и данных процессора.

6.7. Организация шин в вычислителях на МП.

Контроллеры имеют простейшую архитектуру т.к. ориентированы на режим программного обмена, невысокую скорость. В вычислителях стремятся разделить информационные потоки между процессором - памятью, и памятью – ВУ. При передаче информации из памяти в ВУ процессор может выполнять внутренние пересылки, арифметику. В связи с чем применяют разделение ША и ШД на : локальную, системную, шину памяти , расширения.

Примером структурной организации является построение IBM PC

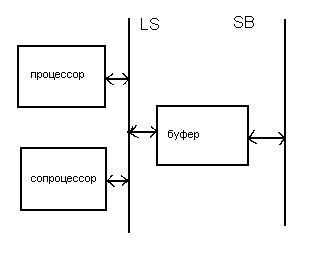

Как и в типовой структуре контроллера здесь используется системный (шинный ) контроллер, формирующий сигналы управления, включения и выключения блоков. Локальная шина L объединяет процессор, сопроцессор, кэш и в старших моделях МП находится внутри корпуса. Буферы между шинами разрывают связи, чтобы обеспечить требуемое направление передачи. Причем буфер связывающий L и S шины включается в режиме ПДП.

6.8..Арифметические и логические операции процессора.

Обычно перечень арифметических и логических операций у процессора не велик. В их основе операции сложения, быстрого сложения на матрицах сумматоров, умножение и деление. Из логических операций — конъюнкция, дизъюнкция, сумма по модулю 2, инверсия. Арифметические операции предназначены для преобразования одного или пары операндов. Результат — третий операнд. Обычно операнды имеют разрядность n (2, 4, 8, 16, 32, 64), но любой вычислитель позволяет последовательно обрабатывать операнды с разрядностью кратной n. Время операции возрастает, но вычислитель тот же самый. Поскольку двоичные числа могут быть представлены в различном формате (целые коды, со знаком, без знака, фиксированная или плавающая запятая), то вычислитель не изменяется, изменяются правила учета разрядов результата. По результату любой арифметической операции формируются признаки: признак выходного переноса С, признак нулевого результата Z, признак старшего разряда S, признак переполнения OVR. Арифметическая операция это операция над всем n разрядным кодом, всеми его разрядами от нулевого до старшего. При выполнении операций над числами с кратной разрядностью следует учитывать формат представления операндов и соответственно каждый признак рассматривать с учетом значения операнда. Например, при двойной длине младшая часть может дать признаки нуля и переноса. В старшей части возможен анализ всех четырех признаков, но если формат без знака анализировать S и OVR нет смысла. Связь результата и признаков операции всегда по здравой логике. Логические операции выполняются поразрядно, т.е. каждый разряд одного операнда комбинирует с соответствующим разрядом второго операнда согласно выбранной функции. Эти операции позволяют установить нулевые уровни в конкретных разрядах, выделить, определить значения того или иного разряда при приеме параллельного кода, т.е. логические операции применяют для формирования управляющих сигналов. Признаки, формируемые при логических операциях, также следует рассматривать применительно к задачам. Операнды двойной длины при логических операциях не имеют смысла.

Вопросы для самопроверки

-

Перечислите основные виды микропроцессоров.

-

Чем микропроцессор отличается от однокристальной ЭВМ?

-

Поясните историю трансформации структуры многокристальных ( арифметических) микропроцессоров.

-

Укажите технологии производства интегральных схем, часто применяемые для их получения.

-

Поясните способ разделения адресного пространства, применяемый в микропроцессорных вычислителях.

-

Для какой цели применяют буферные усилители в шинах адреса и данных?

-

На примере покажите, как выбирается требуемое число секций для схемы.

-

По структурной схеме устройства с микропрограммным управлением покажите управляющие сигналы для синхронизации работы внешних к микропроцессору блоков.

-

Поясните, какими преимуществами обладает структура вычислителя с раздельными системной шиной и шинами расширения.

-

Для какой цели используют признаки, формируемые в результате арифметических и логических операций?

Лекция 7.ПРОЦЕДУРА ВВОДА-ВЫВОДА

7.1.Способы обмена данными

Функционирование любого вычислителя складывается из процедур передачи информации между его отдельными функциональными блоками. При этом передача информации между внутренними РОН называется пересылка, между процессором и памятью чтение/запись, а между памятью и внешними устройствами ввод/вывод информации. Наиболее длинными во времени процедурами считают операции ввода/вывода, поскольку внешние устройства в большинстве случаев имеют меньшее быстродействие, чем процессор или память, поэтому большое внимание на возможные варианты пересылки информации, рассматривая их с точки зрения снижения времени всей процедуры.

Доступ к внешним устройствам в большинстве случаев адресный, т. е. по структуре ввод/вывод не должен отличаться от чтения/записи. Но объем памяти значителен, значительна и шина адреса (минимум 16 разрядов). В тоже время число внешних устройств не может быть физически большим. В вычислителях системы DEC, i360 было принято ограничение на число внешних устройств 255. Это связано с байтом, хотя реально их значительно меньше. Поэтому, сохраняя адресную выборку ВУ ввод/вывод выполнялся с некоторым отличием от чтения/записи:

сигналы разрешения ввода/вывода формировались шинным контролером, в то время ОЗУ/ПЗУ блокируется;

адрес выставлялся на младшем байте и дублировался на старшем. Старший байт практически не использовался.

ШД соединяла выход процессора и вход внешнего устройства (при выводе) и наоборот.

Обмен информацией между внешними устройствами и памятью реализуется в одном из трех подходов:

Программный режим.

Процессор читает содержимое нужной ячейки памяти ОЗУ и выводит это содержимое (РОН) во внешнее устройство. Не преобразуя информацию процессор выступает лишь как временное хранилище (буферная память). Способ позволяет синхронизировать быстродействие ВУ и памяти. Процедура выполняется за две команды. Адреса на внешнее устройство байтовые. Способ возможен, если в наборе команд имеется команды ввода и вывода.

Ввод/вывод с отображением в память.

Наиболее универсальный способ, применяется, когда нет команд ввода/вывода. Последовательность выполнения та же самая: ОЗУCPU, CPUВУ. Отличие: процессор на внешнее устройство выставляет полный адрес, поэтому из адресного пространства исключаются адреса внешних устройств. Вывод с отображением используется часто, поскольку чтение/запись во многом похожи на ввод/вывод. Основной недостаток второго способа — занимается часть адресного пространства. Поэтому способ рекомендуется, если имеются свободные области в адресном пространстве.

Прямой доступ к памяти (ПДП).

7.2. Прямой доступ к памяти

Суть способа в том, что процессор как бы отключается от ШД и содержимое ОЗУ напрямую копируется во внешнее устройство. Главная цель применения ПДП — сократить время ввода/вывода с одновременным использованием процессора для выполнения следующей операции. Существует три способа обеспечения режима ПДП:

с блокировкой процессора.

С приходом запроса на ПДП, процессор отключается, его выходные шины адреса, данных и управления переводятся в третье состояние. Микрокоманды не расшифровываются устройством управления. Процессор не может выполнять операции, хотя тактовый сигнал и питание поступают. Чтобы перевести процессор в такой режим требуется небольшое время. Для обеспечения управления (сигналы выборки, сопровождения, формирование сигналов адреса) необходимо новое устройство, называемое контролер ПДП. Контролер должен заменить процессор при формировании указанных сигналов. Обратный переход также требует некоторого времени. Способ характерен для несложных микропроцессоров имеющих один или несколько регистров команд и не имеющих внутреннего ОЗУ данных.

с квантованием цикла.

В каждом цикле обращения к памяти (ОЗУ, ПЗУ) процессор должен успеть выполнить это обращение за время t/2. Во второй половине цикла процессор отключает свои выходы, позволяя контролеру ПДП выставить свой адрес на шину. За второй интервал выполняется процедура ввода/вывода. Такое условие требует быстродействующей памяти, следовательно, смены элементной базы (переход к ЭСЛ). Последнее затрудняет использование такого подхода, поэтому он практически не применяется.

с отъемом цикла.

При работе процессора имеющего внутреннюю буферную память команд и данных реализуется ПДП с отъемом цикла. Процессор начинает команду с выборки — обращение к ПЗУ, далее ОЗУ или ввод/вывод. Третий способ заключается в том, что вместо положенного обращения процессора в память (стандартный цикл) выполняется процедура ввода/вывода режима ПДП. При этом процессор выполняет текущую команду, поскольку в его буфере команд стоит очередь следующих друг за другом команд. Выходные разряды процессора переводятся в третье состояние и не оказывают влияния на состояние шин адреса и данных. Главное отличие от первого способа — процессор выполняет текущую, следующую команды не останавливаясь. Поскольку процессор не занимает шины в этом режиме процедура ввода/вывода выполняется как бы одновременно с основной операцией.

7.3. Каналы ввода-вывода

В любом режиме ПДП

необходим контроллер специализированная

схема, работающая синхронно с процессором.

Контролеры входят в МП комплекты

соответствующих серий. Основу их

составляют счетчики адреса с произвольной

загрузкой и небольшая схема управления. Для обмена информацией между процессором,

ОЗУ и внешними устройствами существует

буферный блок — каналы ввода/вывода.

Канал — это интегрированное понятие,

объединяющее как аппаратные, так и

программные средства вычислителя для

подключения периферии. Число внешних

устройств может быть значительным,

поэтому для удобства работы с большим

числом внешних устройств, применяют

специальное оборудование — каналы

ввода/вывода. Структурно каналы включаются

между шиной процессора и внешними

устройствами. Функционально канал —

это промежуточный буферный блок,

предназначенный для согласования во

времени работы быстрого процессора и

разнотипных внешних устройств. Основу

канала составляют устройства управления

и буферная память, накапливающая данные

для ввода или вывода из процессора.

Любая процедура ввода/вывода переносит

данные из ОЗУ в буферную память канала

в режиме ПДП или программно, т.е. процессор

не видит внешнего устройства. Процессор

работает с каналом, произвольное ВУ

также не имеет прямого доступа к ОЗУ

или процессору. Внешнее устройство

переносит информацию в канал. Каналы

конструктивно и функционально были

развиты в машинах ЕС ЭВМ. Там использовались

каналы двух типов: селекторные и

мультиплексные. Первые обеспечивали

связь процессора с одним быстрым ВУ,

т.е. селекторный канал имел буферную

память маятникового типа (память делится

пополам, в одну часть запись из другой

части чтение, если память переполнена,

составляющие меняются местами). Это

позволяет «одновременно» читать/записывать

память.

Для обмена информацией между процессором,

ОЗУ и внешними устройствами существует

буферный блок — каналы ввода/вывода.

Канал — это интегрированное понятие,

объединяющее как аппаратные, так и

программные средства вычислителя для

подключения периферии. Число внешних

устройств может быть значительным,

поэтому для удобства работы с большим

числом внешних устройств, применяют

специальное оборудование — каналы

ввода/вывода. Структурно каналы включаются

между шиной процессора и внешними

устройствами. Функционально канал —

это промежуточный буферный блок,

предназначенный для согласования во

времени работы быстрого процессора и

разнотипных внешних устройств. Основу

канала составляют устройства управления

и буферная память, накапливающая данные

для ввода или вывода из процессора.

Любая процедура ввода/вывода переносит

данные из ОЗУ в буферную память канала

в режиме ПДП или программно, т.е. процессор

не видит внешнего устройства. Процессор

работает с каналом, произвольное ВУ

также не имеет прямого доступа к ОЗУ

или процессору. Внешнее устройство

переносит информацию в канал. Каналы

конструктивно и функционально были

развиты в машинах ЕС ЭВМ. Там использовались

каналы двух типов: селекторные и

мультиплексные. Первые обеспечивали

связь процессора с одним быстрым ВУ,

т.е. селекторный канал имел буферную

память маятникового типа (память делится

пополам, в одну часть запись из другой

части чтение, если память переполнена,

составляющие меняются местами). Это

позволяет «одновременно» читать/записывать

память.

Селекторные каналы

объединялись в группы, что позволяло

подключать несколько внешних устройств

к процессору, но в любой момент работало

только одно ВУ. Мультиплексные каналы

рассчитаны на работу с медленными ВУ

(печать, клавиатура, НМЛ). Мультиплексный

канал работает в байт-последовательном

режиме с несколькими внешними устройствами

«одновременно». Фактически канал

опрашивает последовательно каждое

внешнее устройство, пересылает байт и

обращается к следующему. Буферная память

таких каналов разделена на подканалы.

Каждый подканал работает с одним ВУ. В

конечном счете буферная память заполняется

информацией с нескольких ВУ и процессор

быстро прочитает данные. Управляющие

сигналы формируются на основании

командного слова канала — процессор

пересылает команду в канал, она

расшифровывается и внешнее устройство

получает управляющий не от процессора,

а от устройства управления каналом.

Кроме командного слова процессор

посылает в канал адресное слово —

начальный или конечный адрес источника

информации. Слова данных также иногда

выделяют при обмене информации. Многие

внешние устройства имеют собственную

буферную память, поэтому необходимости

в самостоятельном канале у них нет.

Функции канала, его принципы организации

уже внесены в структуру внешнего

устройства. Отсюда актуальность каналов

как самостоятельных функциональных

узлов в тех случаях, когда очень быстрый

процессор обменивается с довольно

медленными внешними устройствами, число

которых значительно.

Селекторные каналы

объединялись в группы, что позволяло

подключать несколько внешних устройств

к процессору, но в любой момент работало

только одно ВУ. Мультиплексные каналы

рассчитаны на работу с медленными ВУ

(печать, клавиатура, НМЛ). Мультиплексный

канал работает в байт-последовательном

режиме с несколькими внешними устройствами

«одновременно». Фактически канал

опрашивает последовательно каждое

внешнее устройство, пересылает байт и

обращается к следующему. Буферная память

таких каналов разделена на подканалы.

Каждый подканал работает с одним ВУ. В

конечном счете буферная память заполняется

информацией с нескольких ВУ и процессор

быстро прочитает данные. Управляющие

сигналы формируются на основании

командного слова канала — процессор

пересылает команду в канал, она

расшифровывается и внешнее устройство

получает управляющий не от процессора,

а от устройства управления каналом.

Кроме командного слова процессор

посылает в канал адресное слово —

начальный или конечный адрес источника

информации. Слова данных также иногда

выделяют при обмене информации. Многие

внешние устройства имеют собственную

буферную память, поэтому необходимости

в самостоятельном канале у них нет.

Функции канала, его принципы организации

уже внесены в структуру внешнего

устройства. Отсюда актуальность каналов

как самостоятельных функциональных

узлов в тех случаях, когда очень быстрый

процессор обменивается с довольно

медленными внешними устройствами, число

которых значительно.

Вопросы для самопроверки

-

Кокой тип организации ввод-вывода возможен в вычислителя , имеющих систему команд Intel?

-

Способ ввода-вывода « с отображением в памяти» имеет достоинства…

-

Поясните цели, решенные при вводе информации в ЭВМ в режиме ПДП.

-

Какой из трех распространенных способов ПДП сегодня наиболее востребован?

-

Что позволяет совместить работу процессора и процедуру ввода-вывода при использовании режима ПДП?

-

Назовите современные блоки, выполняющие роль каналов ввода-вывода.

-

К какому типу каналов можно отнести шину расширения типа PCI?

Лекция 8. ИНТЕРФЕЙСЫ ЭВМ.

8.1 .Типы интерфейсов вычислительных устройств.

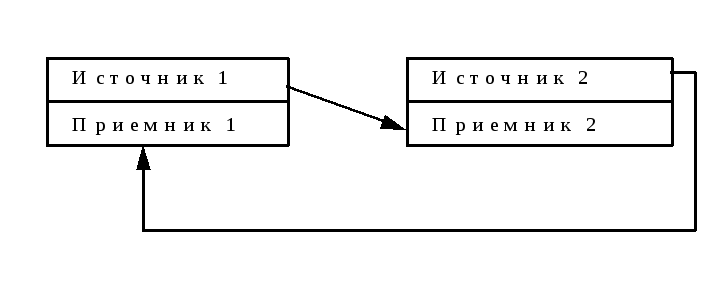

Непосредственно с идеологией канала связан термин интерфейс. Он объединяет в себе аппаратные и логические построения, обеспечивающие правильную передачу информации от источника к приемнику. Как правило, на верхнем понятии каналы и интерфейсы часто совмещают. Общее у них — передача информации, но интерфейс, более конкретный термин, имеющий фиксированные характеристики и часто канал вбирает в себя характеристики интерфейса. Любой канал имеет интерфейс, но любой интерфейс входит в канал. Различают интерфейсы по многим критериям .

Например, по способу передачи данных.

Последовательный способ. Сигналы данных передаются в виде низкого и высокого уровней последовательно от источника к приемнику, причем способ передачи может быть как синхронным так и асинхронным.

Параллельный способ. Байт данных (два байта) одновременно передается от источника к приемнику. Этот способ также может быть синхронным или асинхронным.

По направлению передачи интерфейсы делят на следующие.

1) Цепочечные

2) Радиальные (типа звезда).

3) Магистральные. Источник выставляет информацию на шине (магистрали) и все внешние устройства подключенные к ней могут считать информацию. Для определенности ВУ выбирают, обеспечивая один приемник. По отношению к радиальному способу аппаратные затраты ниже, но надежность и скорость хуже. Магистральный интерфейс позволяет изменять число внешних устройств, при этом их можно менять местами.

Радиальный

интерфейс более быстр, надежен, но

требует отдельных разъемов для

подключения. Радиальные интерфейсы

используются в ПЭВМ для подключения

периферии. Магистральный интерфейс

используют для объединения функциональных

модулей в вычислитель. На основе

магистрального интерфейса разработан

функционально-модульный метод объединения

блоков.

Радиальный

интерфейс более быстр, надежен, но

требует отдельных разъемов для

подключения. Радиальные интерфейсы

используются в ПЭВМ для подключения

периферии. Магистральный интерфейс

используют для объединения функциональных

модулей в вычислитель. На основе

магистрального интерфейса разработан

функционально-модульный метод объединения

блоков.

по назначению:

1) системный интерфейс

2) интерфейсы внешних устройств.

3) межпроцессорные интерфейсы

4) межсистемные интерфейсы

Интерфейсы предназначены для организации связи с различными блоками вычислительной системы CPU, RAM, I/O. Системные интерфейсы это некая основа, на которой построен вычислитель. Изменение конфигурации вычислителя в пределах интерфейса приводит лишь к программным изменениям. Стоит поменять интерфейс, сразу же возникают аппаратные дополнения. Тип системного интерфейса формировался из конфигураций вычислителя: 8-, 16-, 32-разрядные с раздельной или совмещенной шиной адрес/данные. Т.е. первоначально разрабатывался вычислитель, принимались связи между блоками и затем эти связи определялись как тот или иной тип интерфейса. Последующие разработки принимали уже имеющиеся типы связей. При разработке нового вычислителя принят модульный подход: выбирается стандартный системный интерфейс (если он не задан), функциональные блоки определенные заданием подключаются по правилам этого интерфейса, уточняются их характеристики, определяются параметры — вычислитель «спроектирован». Примерами системных интерфейсов являются: multybus, Q-bus, microbus, ISA, EISA, PCI.

Периферийные интерфейсы связывают устройства ввода/вывода с внешними периферийными устройствами. Периферийные интерфейсы имеют большую стабильность, поскольку номенклатура периферии широкая и изменение в способах ее подключения снижает потребительские качества внешних устройств. Самыми распространенными считаются:

параллельный интерфейс ИРПМ-М (CENTRONIX) — байтовый параллельный интерфейс для обмена байтами (принтер, индикация). Интерфейс асинхронный.

ИРПС (интерфейс радиальный последовательный) — информация передается последовательно, каждый байт стробируется (синхронизируется с приемником), информация передается уровнем тока, поэтому помехоустойчивость наибольшая.

RS-232C (стык С2) — информация передается последовательно со стробированием байтов. Интерфейс потенциальный «1»=+12В, «0»=-12В. Расстояние 0.7-1.5 метра. Применяют в ПЭВМ для связи со стандартной периферией.

Межсистемные интерфейсы предназначены для связи, объединения различных систем в единую конфигурацию. Как правило, это информационно-вычислительные системы, поэтому для них используют концепцию открытых систем, позволяющую наращивать вычислители. Примером такой конфигурации является интерфейс VME — трехшинная архитектура включающая параллельную системную магистраль, последовательную магистраль и параллельную магистраль расширения памяти.

Межпроцессорные интерфейсы ориентируются на системную магистраль (работая порознь). Это направление на сегодня практически не разрабатывается.

8.2 Последовательный интерфейс RS-232

Для последовательных интерфейсов выбор подключаемых устройств значительно шире, поэтому большинство РС одновременно оборудованы двумя интерфейсными разъёмами для последовательной передачи данных ( Рис.2.1)Обычно они различаются по внешнему виду. Разъёмы последовательного интерфейса на РС представляют собой 9 – контактный (вилка) Sub – D и 25 – контактный (вилка) Sub – D, назначение контактов которых приведено в таблице 2.1

Рис.8

Таблица 1

|

Контакт разъёма DB9 |

Контакт разъёма DB25 |

Обозначение сигнала |

I/O |

Описание |

|

1 |

8 |

DCD (Data Carrier Detect) |

I |

Обнаружение несущей |

|

2 |

3 |

RXD (Recive Data) |

I |

Принимаемые данные |

|

3 |

2 |

TXD (Transmit Data) |

O |

Передаваемые данные |

|

4 |

20 |

DTR (Data Terminal Ready) |

O |

Готовность оконечного устройства |

|

5 |

7 |

GND (Ground) |

-- |

Сигнальная земля |

|

6 |

6 |

DSR (Data Set Ready) |

I |

Готовность модема |

|

7 |

4 |

RTS (Request To Send) |

O |

Запрос передачи |

|

8 |

5 |

RI (Ring Indicator) |

I |

Сброс для передачи |

|

9 |

22 |

I |

Индикатор звонка |

В качестве стандартного обозначения для последовательного интерфейса чаще всего используют RS -232С.

Главный элемент последовательного интерфейса – микросхема UART (Universal Asynchron Receiver Transmitter) 16550AF, 16650 или 16750. В старых контроллерах применялись микросхемы: 8250 (А,В), 16450, 16550 (А). Контроллер на базе чипа 8250 обеспечивает максимальную скорость передачи данных 9600 бод, чип 16450 – 115200 бод, а чип 16550AF, и ему подобные – 921600 бод.

В отличии от параллельной передачи данных, последовательная передача осуществляется побитно. Отдельные биты пересылаются (или принимаются) последовательно друг за другом, при этом возможен обмен данными в двух направлениях. Уровень напряжения последовательного интерфейса изменяется в пределах от -12 до +12 В. Благодаря этому относительно высокому значению напряжения повышается помехоустойчивость, и данные могут передаваться без потерь по кабелю длинной 50 метров и более.

Контроллер стыка RS-232 является полностью программируемым устройством; вы можете задать следующие параметры обмена: количество битов данных и стоп-битов, вид четности и скорость обмена в бодах (бит/с).

В асинхронном режиме, который используют РС (передаваемая команда состоит из стартового бита, 8 бит данных и одного стоп – бита), прием, и передача данных осуществляются с одинаковой тактовой частотой.

Для связи через последовательный интерфейс в принципе было бы достаточно трёх проводов: приёма, передачи и корпус. Однако на практике это часто не так, что показывает таблица 2.1.

Последовательный интерфейс связывает два устройства. Для того чтобы “собеседники” при обмене данными не перебивали друг друга, они должны иметь единый протокол приёма/передачи которым определяется последовательность обмена данными.

Данные при последовательной передачи разделяются служебными посылками, такими как стартовый бит (Start bit) и стоп – бит (Stop bit). Эти биты указывают на начало и конец последовательности бит данных (Data bits). Данный метод передачи осуществить синхронизацию между приёмной и передающими сторонами, а также выровнять скорость обмена данными.

Для идентификации и распознавания ошибок при последовательной передаче в состав посылки дополнительно включают бит контроля чётности (Parity bit). Существует несколько различных вариантов использования бита контроля чётности:

- бит контроля чётности не посылается (No Parity)

- бит контроля чётности чётный (Even Parity)

- бит контроля чётности нечётный (Odd Parity)

Значение бита контроля чётности определяется бинарной суммой всех передаваемых битов данных.

Рассмотрим подробнее назначение сигналов последовательного интерфейса. Приведённый здесь технический материал поможет разобраться с назначением индикаторов состояния на модеме и правильно настроить коммуникационные программы:

Сигнал DCD используется в модемах для сообщения компьютеру и коммуникационной программе об установлении связи модем – модем. Когда локальный модем связывается с удалённым модемом и получает в ответ хороший сигнал несущей, он формирует положительный сигнал DCD.

Сигнал RXD представляет собой данные, переданные удалённым РС и полученные компьютером- модемом.

Сигнал TXD представляет собой данные, передаваемые компьютером/модемом. Отметим наличие двух линий данных, одна из которых предназначена для передачи, а другая для приёма. Следовательно, при наличии соответствующей коммуникационной программы два последовательных устройства могут передавать данные одновременно.

Сигнал DTR (положительный) сообщает удалённому компьютеру о готовности приёма данных. Дополнительным для этого сигнала является сигнал DSR. Чтобы два устройства могли взаимодействовать, оба эти сигнала должны быть высокого уровня, сообщая о наличие устройств и их готовности к обмену данными.

Сигнал GND является сигнальной землёй, т. е. второй линией, необходимой для передачи и приёма сигналов.

Сигнал DSR наряду с сигналом DTR сообщает РС о включении (режим On-line) и готовности к обмену данными с удалённым компьютером/модемом (сигнал положительный).

Сигнал RTS является одним из двух сигналов (второй - CTS), благодаря которым осуществляется обмен данными между двумя соединёнными компьютерами/модемами. Это сигналы готовности к приёму данных. Сигнал RTS формирует локальный, а сигнал CTS – удалённый модем.

Сигнал CTS дополняет пару RTS/CTS. В случае отсутствия на соответствующих линиях сигналов RTS и CTS положительной полярности практически во всех системах связи передача данных по последовательному каналу невозможна. Однако имеются исключения. Чаще всего встречается подключение последовательного оконечного устройства к удалённому компьютеру. При таком способе подключения линии RTS/CTS можно как использовать так и не использовать. Обычно для того, чтобы сэкономить количество проводников в соединительном кабеле, эти линии коммутируют соответствующим образом непосредственно на локальном разъёме интерфейса.

Сигналом RI локальный модем сообщает компьютеру (коммуникационной программе), к которому он подключен, о поступлении телефонного вызова, т. е. о предстоящем сеансе связи.

COM – порты могут быть сконфигурированы различным образом. BIOS PC поддерживает до 4 последовательных интерфейсов. С конфигурацией двух как правило, проблем не возникает, тем более что стандартные установки на плате интерфейса обычно соответствуют оптимальным. Проблемы могут возникнуть при конфигурировании портов COM3 и COM4, поскольку для необходимо указать непересекающиеся с другими устройствами адреса и номера линий прерывания.