Для магистратуры / CMOS_IC

.pdf

280

j-го разряда. В результате после N тактов разница между ViB B и VOB B не пре-

высит VRB /2B NP ,P рис.8.6,б.

Достоинство АЦП последовательного приближения – простота, недостаток высокие требования к ЦАП. Плата за простоту – ограниченное быстродействие.

Алгоритмический АЦП. Алгоритмический АЦП, как и АЦП последовательного приближения, может формировать выходной код поразрядно, что займет N таков.

Но он может формировать и сразу несколько разрядов выходного кода, сократив время преобразования до N/n тактов. В этом случае в его составе используют n-разрядные ЦАП и АЦП, рис.8.7.

Рис.8.7. Алгоритмический АЦП

В отличие от АЦП последовательного приближения алгоритмический АЦП преобразует не сам входной сигнал, а его остаток (разность между сигналом и накопленным значением кода). Выходной код получается последовательным заполнением регистра сдвига.

Достоинство алгоритмическогоАЦП – низкоразрядный ЦАП, недостаток наличие вычитателя, который должен быть полноразрядной точности.

8.3.Последовательные АЦП.

АЦП последовательного счета. Содержит ЦАП, компаратор и управляемый синхронный счетчик, рис.8.8.

281

Рис.8.8. Последовательный АЦП

Перед началом очередного сеанса работы (АЦП преобразования) счетчик обнуляется сигналом управления, а затем переходит в режим счета тактовых импульсов, частота которых намного выше частоты сигнала fcB .B Выходной код счетчика преобразуются в аналоговую форму VOB B параллельным ЦАП и поступают на вход компаратора. Входной сигнал ViB B подается на другой вход компаратора. Счетчик остается в таком режиме, пока ViB >VB OB .B При нарушении неравенства счетчик останавливается. Накопленный счетчиком код соответствует входному сигналу и может быть считан.

Достоинства АЦП последовательного счета – предельная простота. Недостаток – низкое быстродействие. В худшем случае задержка преобразования составит 2NP P тактов.

Интегрирующий АЦП. Состоит из интегратора, компаратора с нулевым порогом и управляемого синхронного счетчика, рис.8.9.

Рис.8.9. Интегрирующий АЦП

В отличии от ранее рассмотренных АЦП в цифровую форму преобразуется не сама входная величина, а ее среднее за некоторый интервал времени, что повышает помехоустойчивость преобразования. Для усред-

282

нения используется накопление входного сигнала на линейном интеграторе. Как правило, для повышения точности используют интегратор с двойным интегрированием, изображенный на рис.8.9.

Перед началом сеанса счетчик обнуляется, а затем АЦП переходит в режим интегрирования (1), при котором на положительный вход интегратора подан преобразуемый сигнал, а счетчик сохраняет нулевое состояние. Длительность режима (1) такова, чтобы при максимальном входном сигнале интегратор оставался в линейной области. В счетном режиме (2) на отрицательный вход интегратора подается опорное напряжение VRB >VB iB ,B и пока выход интегратора положителен, на выходе компаратора единица, которая разрешает счет. Время разряда и величина накопленная счетчиком за это время пропорциональны величине входного сигнала.

Интегрирующий АЦП сочетает высокую точность и простоту реализации. За нее приходится расплачиваться низким быстродействием. Принципиальным недостатком интегрирующего АЦП является наличие интервала времени, когда входной сигнал отсоединен от интегратора, т.е. усреднение работает с перерывами.

Этого недостатка лишен другой класс интегрирующих АЦП, называемых дельта-сигма (равнозначно сигма-дельта) АЦП.

Дельта-сигма АЦП (∆Σ-АЦП). Состоит из двух основных блоков: дельта-сигма модулятора (ДСМ) и цифрового фильтра (ЦФ), рис.8.10.

Рис.8.10. Дельта-сигма АЦП

ДСМ преобразует аналоговый входной сигнал в последовательность n-разрядных чисел. За счет тактовой частоты модулятора fsB B во много раз превышающую частоту Найквиста fNB B удается передать входной сигнал ViB B с высокой точностью в виде потока чисел ВnB .B ЦФ выполняет линейное преобразование потока BnB B в N-разрядное число B.

ДСМ содержит n-разрядные АЦП и ЦАП замкнутые в контур обратной связи через линейный фильтр (в качестве фильтра на рис.8.10 –

283

просто интегратор). Фактически ДСМ осуществляет оцифровку остатка (разности входного сигнала с переведенным в аналог выходом), пропущенного через линейный фильтр. Точностные характеристики ДСМ зависят от порядка фильтра и улучшаются с повышением порядка, но при этом возникает проблема устойчивости контура.

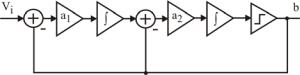

Дельта-сигма модулятор второго порядка. Содержит два инте-

гратора, компаратор, и два дифференциальных сумматора рис.8.11.

Рис.8.11. Дельта-сигма модулятор второго порядка

В варианте на рис. 8.11 использован одноразрядный АЦП – компаратор. Тем не менее, за счет высокой передискретизации (оверсэмплин-

га) M = fs  fN можно получить очень высокую разрядность ∆-Σ-АЦП.

fN можно получить очень высокую разрядность ∆-Σ-АЦП.

При выделении сигнала из цифрового (двоичного) потока очень высокую нагрузку несет ЦФ. Однако он реализуется на цифровых схемах и не вносит дополнительных искажений, связанных с неидеальностью МОП приборов.

Главное достоинство ∆-Σ-АЦП – возможность получения высокой точности при минимальных требованиях к аналоговым элементам. Недостаток – ограниченное быстродействие из-за необходимости высокого оверсэмплинга.

Дельта-сигма преобразователи находят очень широкое применение в различных приложениях.

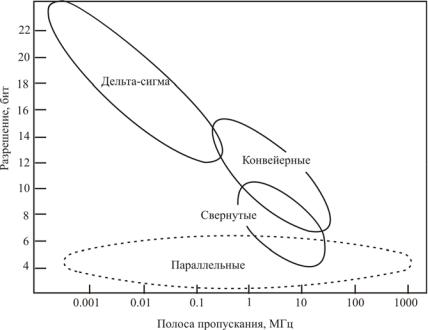

8.4. Сравнение АЦП

Сравнительные характеристики основных типов АЦП приведены на рис.8.12.

284

Рис.8.12. Сравнительные характеристики АЦП

Из него следует, что для получения максимального разрешения целесообразно использовать ∆Σ-АЦП, а для получения максимального быстродействия – конвейерные и параллельные (флэш) АЦП.

285

Глава 9. Конвейерные АЦП.

Конвейерные АЦП позволяют получить высокое быстродействие и достаточно высокое разрешение.

Их появление обусловлено трудностью использования параллельных АЦП (флэш-АЦП) при высокой разрядности. У флэш-АЦП количество компараторов, экспоненциально зависит от числа разрядов. При этом:

каждый компаратор имеет индивидуальный порог, отличающийся на 1 LSB;

все компараторы включены параллельно, загружая входной каскад АЦП;

на выходах компаратора термометрический код, который нужно преобразовать в двоичный, да еще с учетом возможных ошибок компараторов;

По этим причинам при высокой разрядности используют упрощенные последовательно-параллельные АЦП и наиболее часто – конвейерные. Они могут быть построены простейших на одноразрядных АЦП с сохранением остатка (АЦПº, см. рис.8.5). Последовательное соединение таких АЦП позволяет организовать конвейерный режим, при котором внутри АЦП обрабатывается одновременно несколько сигналов, а выходная частота равна тактовой частоте. Правда конвейер вводит задержку пропорциональную количеству разрядов, но во многих случаях это допустимо. Достоинством конвейерных АЦП являются:

идентичность и независимость одинаковых каскадов; возможность исправления ошибок непосредственно в конвейере; возможность снижения требований к элементам (повышения точ-

ности АЦП) и помехоустойчивость за счет избыточности.

Большой популярностью пользуются 1.5 разрядные конвейерные АЦП, в которых каждые два каскада АЦПº формируют 3 разряда выходного кода, рис.9.1.

286

Рис.9.1. Конвейерный 1.5 разрядный АЦП

Каскад АЦПº преобразует входной сигнал VjB B в два выходных двоичных сигнала М и L и аналоговый сигнал остатка Vj+1B ,B в соответствие с табл.9.1.

Алгоритм работы 1.5 разрядного АЦПº |

Таблица 9.1. |

|||||

VjB B |

|

|

М |

L |

Vj+1B |

B |

VjB B < –VRB /4B |

|

0 |

0 |

2VjB B + VRB B |

||

–VRB /4B |

< VjB B |

< |

0 |

1 |

2VjB B |

|

VRB /4B |

|

|

|

|

2VjB B |

– VRB B |

VjB B > VRB |

/4B |

|

1 |

0 |

||

Фактически АЦПº формирует тернарный код, что поясняется на

рис.9.2.

287

Рис.9.2. Характеристики элементов 1.5 разрядного АЦПº:

а – тернарного АЦП; б – тернарного ЦАП; в –усилителя остатка

Последний каскад работает как обычный двухразрядный АЦП. Тернарные коды задерживаются треугольной матрицей D-

триггеров и синхронно подаются на корректирующий регистр, осуществляющий их сложение. Задержка и сложение могут быть выполнены и на треугольной матрице трехвходовых сумматоров.

Корректирующий выходной регистр работает по правилу

N−2 |

1 Lj ) + 2−N+1 |

|

1 LN−1) . |

B(b1,b2 ,...,bN ) = ∑2−j (Mj + |

(MN−1 + |

||

j=1 |

2 |

|

2 |

Избыточность конвейерного АЦП (двухразрядные АЦПº выдают тернарные коды) позволяет исправлять ошибки, обусловленные неточностью порогов и шумами, пока те не очень велики. Так если на некотором шаге преобразования вместо кода 01 появится код 00, то на следующем шаге код 10 способен во многих случаях скомпенсировать эту ошибку.

Реализация АЦПº достаточно просто выполняется схемой на ПК,

рис.9.3.

288

Рис.9.3. 1.5 разрядный АЦП с сохранением остатка

Вее составе тернарный АЦП на основе двух компараторов и вентиля, тернарный ЦАП, управляемый тернарным АЦП, и сумматор на операционном усилителе с удвоением напряжения за счет коммутации кон-

денсаторов С1B B и С2B .B

Рассмотрим работу АЦПº для случая, когда входной сигнал раз-

нополярный (VRB /2B > VjB >B –VRB /2)B .

Вподготовительной фазе приема φ1B (B ключи с индексом 1 замкнуты) входной сигнал VjB заряжаетB парллельно соединенные конденсаторы С1 и С2 и формирует на выходе тернарного АЦП сигналы M и L, которые

сохраняются и в следующей фазе передачи φ2B .B При замыкании ключей 2 конденсаторы соединяются последовательно и к ЦАП, управляемому тернарным АЦП. В результате выходное напряжение становится равным следующему значению

|

|

+C2 |

|

|

|

|

Vj+1 |

C1 |

|

C2 |

|

||

= |

C |

Vj − |

C |

VD + Ej , |

||

|

|

1 |

|

|

1 |

|

где: VDB B – напряжение на выходе ЦАП; E – ошибка передачи сигнала. Последняя зависит от коэффициента усиления ОУ

|

−1 |

|

|

C2 |

|

Ej = |

|

+ |

|

||

A |

1 |

C |

Vj . |

||

|

|

|

|

1 |

|

Равенство емкостей С1B =B С2B обеспечиваетB удвоение входного сигнала и вычитание из него напряжения VDB .B Высокий коэффициент усиления – малую ошибку преобразования при перераспределении зарядов.

289

Глава 10. Дельта-сигма преобразователи

10.1 Принцип работы ∆Σ-модулятора

Однобитные дельта-сигма модуляторы. Однобитные дельта-

сигма модуляторы (∆Σ-модуляторы) осуществляют оцифровку сигналов с помощью единственного компаратора. Двоичный выходной сигнал преобразуется в аналоговый уровень и вычитается из входного без внесения дополнительной нелинейности. Интегрирование (и, возможно, многократное) разности входного и выходного сигнала осуществляется с высокой точностью, обеспечиваемой операционным усилителем (усилителями) с высоким коэффициентом усиления. Этот накопленный разностный сигнал и поступает на компаратор. Таким образом, точность модулятора определяется точностью основных операций аналоговой техники: сложением с учетом знака и накоплением, и ограничивается в основном нелинейностью таких операций и шумами при их выполнении. В других преобразователях ( в том числе, в многобитных ∆Σ-модуляторах) либо используется несколько компараторов, либо требуется точное усиление сигнала.

На рис.10.1 показана блок-схема дельта-сигма модулятора первого порядка.

Рис.10.1. Модулятор первого порядка:

а – блок схема; б –линеаризованная схема

Он состоит из аналогового сумматора, фильтра нижних частот (интегратора) и компаратора, охваченных петлей отрицательной обратной связи, рис.10.1,а. На вход дельта-сигма модулятора поступает аналоговый сигнал x(t), а на выходе – двоичный сигнал y(n). В силу отрицательной обратной связи выходной шум при высоком прямом коэффициенте уси-