Для магистратуры / CMOS_IC

.pdf

200

10.4. Повторители

Задержка сигнала по длинной линии (рис.10.3,а) пропорциональна квадрату ее длины l. При передаче сигнала на большие расстояния, особенно в быстродействующих устройствах, задержка может стать недопустимо большой. Для ее снижения естественно разбивать линию на сегменты меньшей длины (рис.10.3,б) и в каждом сегменте ставить драйвер (инвертор или буфер из двух инверторов), ускоряющий передачу сигнала. Оптимальное по суммарной задержке разбиение длинной линии зависит как от параметров проводников, так и от параметров МОП-транзисторов.

Рис.10.3. Длинная линия: а – одиночная линия; б – секционированная линия

Пусть линия длиной l разбита на N сегментов, в каждом из которых стоит драйвер с шириной затвора W. В таком случае сопротивление проводника сегмента равно Rw l /N, емкость проводника сегмента Cw l / N, выходное сопротивление драйвера Rg/W, а его входная и выходные емкости Сg W. Общая задержка сегментированной линии (по аналогии с формулой (10.4а)) равна

τΣ = [2RWg (Cg W + C2Nw l) + (2RWg + RNw l)(C2Nw l + Cg W)]N .(10.6)

Из равенства нулю производной τΣ по N можно определить оптимальное количество каскадов. Минимум задержки имеет место в случае

N = l |

R w Cw |

. |

(10.7) |

|

2Rg Cg |

|

|

Из равенства нулю производной τΣ |

по W можно определить оп- |

||

тимальные размеры драйвера: |

|

|

|

W = |

R g Cw . |

|

(10.8) |

|

R w Cg |

|

|

201

Подставляя (10.7) и (10.8) в (10.6) имеем значение минимальной задержки

τΣ min = l (2 +  2)

2)  RgCgRwCw . (10.9)

RgCgRwCw . (10.9)

Величина задержки порядка 50 пс/мм, т.е. примерно совпадает с полученной в предыдущих оценках. Но эта задержка с возрастанием длины проводника растет линейно, а не квадратично.

Эффекты распространения (задержки) сигнала по линии существенны только для импульсов с фронтом (спадом) короче времени его распространения

tr << 2,5 l / c,

где с – скорость распространения сигнала по линии.

202

Глава 11. Методология проектирования

Современная кремниевая технология позволяет на одном кристалле разместить сложную микроэлектронную систему. Ее проектирование предполагает решение ряда задач с широким спектром целей, достижение которых требует определенных компромиссов. Наряду с выполнением заданных функций система должна удовлетворять ряду технических требований при используемых технологических возможностях. Общими требованиями к интегральным схемам (и системам) являются:

уменьшение площади; повышение быстродействия (эффективности); снижение потребляемой мощности; упрощение тестирования; повышение надежности;

снижение стоимости, состоящей из затрат на проектирование, освоение изготовления и непосредственно на производство.

С точки зрения проектировщика, существует два принципиально различных класса микроэлектронных изделий: серийные микросхемы широкого применения (например, микропроцессоры, ЗУ) и специализированные микросхемы самого разного назначения, включая системы на кристалле.

Серийные изделия, выпускаемые в массовых объемах, обладают высокой производительностью, имеют низкую стоимость, фактически являются отраслевыми стандартами. На их оптимальное проектирование тратятся значительное время и большие средства, которые окупаются за счет высокой прибыли при массовом спросе.

Специализированные микросхемы позволяют добиваться уникальных характеристик систем, которые недостижимы на стандартных микросхемах. Однако они должны разрабатываться за короткое время, при меньших затратах и с учетом объемов производства. Вследствие этого при их разработке используются различные методы ускорения (и удешевления) проектирования.

Специализированные микросхемы разрабатываются, как полузаказные, а в их составе могут быть различные блоки, в том числе:

заказные схемы; на стандартных ячейках (элементах);

на вентильных матрицах; с программируемыми соединениями.

Одно из основных различий при проектировании этих блоков состоит в степени свободы выбора при разработке топологии.

Для заказных схем свобода ограничивается только правилами проектирования топологии.

203

Вблоках на стандартных ячейках ограничена их высота и месторасположение соединений.

Вблоках на вентильных матрицах топология элементов строго задана и проектируются межсоединения (иногда только контакты между проводниками).

Всхемах с программируемыми соединениями топология задана полностью, а в процессе настройки пользователь создает требуемые соединения (или устраняет ненужные).

Стандартные ячейки могут представлять собой специально или ранее разработанные типовые блоки (макроячейки), а также схемы произвольной логики.

11.1.Символьная топология

Процесс разработки топологии заказных схем с произвольной логикой является “узким местом” в проектировании СБИС.

Рис.11.1 . Инвертор: а – электрическая схема; б – символьная топология; в – полная топология

Для его ускорения применяют ряд методов, получивших общее название метода символьной топологии. При этом подходе разработчик проектирует не непосредственно топологию, а ее эскиз, качественно отражающий взаимное размещение топологических элементов (рис.11.1). Полная топо-

204

логия реализуется при обработке символьной топологии специальной программой.

Символьная топология весьма уместна при выборе конфигурации сложных схем, поскольку позволяет достаточно просто анализировать возможные их варианты, что показано на примере инвертора на рис.11.2.

Рис.11.2. Варианты топологии инвертора

Очевидно,что n-МОП и p-МОП могут быть размещены вертикально (рис.11.2,а) и горизонтально (рис.11.2,б). Размещение других проводников над инвертором может выполняться либо между n-МОП и p- МОП (рис.11.2,в), либо между n-МОП и общей шиной GND, либо между p-МОП и шиной питания VDD (рис.11.2,г). Увеличение ширины канала достигается добавлением параллельных транзисторов (рис.11.2,д) или изменением их формы (переход к кольцевым МОП) (рис.11.2,е).

Количество конфигураций сложных элементов растет очень быстро. Поэтому даже в элементах произвольной логики стремятся перейти от произвольного размещения компонентов (рис.11.3,а) к упорядоченному

(рис.11.3,б).

205

Рис.11.3. Топология вентилей: а – произвольное размещение; б – стандартные ячейки

Введение рядов для размещения элементов – переход к стандартным ячейкам – является первым шагом на этом пути.

11.2. Стандартные ячейки

Библиотека стандартных ячеек содержит набор схем с компактной топологией, у которых одинаковая высота, а ширина может быть различной (рис.11.4). Ограничение на высоту ячейки не препятствует оптимизации размеров транзисторов в схеме. Межсоединения ячеек должны размещаться в определенных местах, чтобы облегчить их взаимную коммутацию.

Основная проблема проектирования на стандартных ячейках заключается в определении маршрутов соединений.

Рис.11.4 .Топология стандартных ячеек.

Стандартные ячейки размещаются рядами, а зазоры между рядами используют для трасс межсоединений. В такую структуру легко вписываются и макроячейки (рис.11.5).

206

Рис.11.5. Стандартные ячейки и макроячейки

11.3. Вентильные матрицы.

Вентильная матрица представляет собой однородную структуру, состоящую из несоединенных между собой вентилей (или заготовок для них), расположенных в виде матрицы (рис.11.6). Вентильные матрицы, занимающие весь кристалл, называют базовыми матричными кристаллами (БМК).

Рис.11.6. Матрица вентилей: а – без коммутации; б – c коммутацией

Иногда в виде матрицы расположены несоединенные транзисторы (рис.11.7), получившие название «море вентилей».

207

Рис.11.7. Море вентилей: а – без коммутации; б – с коммутацией

В обоих случаях необходимо задать тип вентиля подсоединением транзисторов к шинам питания и топологию межсоединений образованных вентилей.

Поскольку соединять нужно уже размещенные вентили, эффективным оказывается применение САПР, что значительно сокращает время проектирования. Таким образом, по сравнению с полным проектированием на заказ проектирование с использованием матриц вентилей является менее дорогим и более быстрым.

11.4. Программируемые матрицы

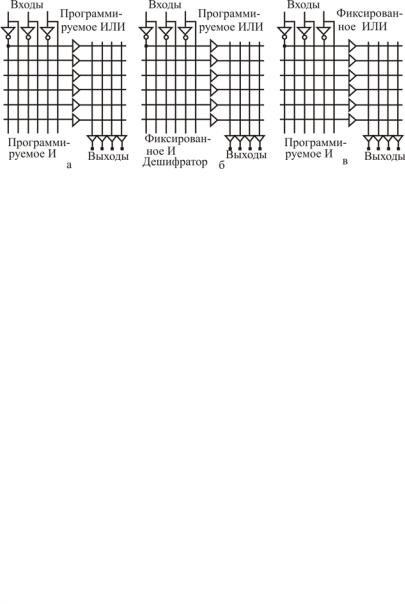

Однородные матричные структуры позволяют достигать высокой удельной (на единицу площади) производительности во многих задачах, где не требуются сложные итерационные алгоритмы. Кроме того, они проще в разработке и тестировании. Поэтому они находят широкое применение в интегральных схемах. К таким схемам относятся ПЗУ, в которых в качестве элемента используется всего один транзистор предельно малых размеров. Наряду с ПЗУ применяются другие матричные структуры. На рис.11.8 приведены три основные матричные структуры:

1)программируемая логическая матрица – ПЛМ (PLA);

2)постоянное запоминающее устройство – ПЗУ (PROM);

3)программируемая матричная логика – ПМЛ (PAL).

208

Рис.11.8. Типы программируемых матриц: а – ПЛМ; б – ПЗУ; в – ПМЛ

Каждая из структур содержит две матрицы, выполняющие проводные функции. Первая матрица выполняет функцию И, вторая – функцию ИЛИ. При этом:

вПЛМ в обеих матрицах могут быть записаны (запрограммированы) произвольные комбинации, т.е. ее выходы выполняют произвольные логические функции над входами в стандартной форме (дизъюнкцию конъюнкций);

вПЗУ первая матрица является дешифратором, а вторая содержит произвольные коды;

вПЛМ в первой матрице произвольные комбинации, а в строчках второй матрицы только одно соединение, т.е. она выполняет более узкие функции, чем ПЛМ тех же размеров.

11.5.Программируемые пользователем матрицы

Широкое распространение получили матричные структуры с программируемыми пользователем соединениями. Современная технология позволяет получать как однократные (создаваемые за счет электрического пробоя диэлектрика – “программируемые полем”) соединения, так и соединения с помощью ключей, управляемых запоминающими элементами. Причем сами элементы памяти могут быть и в виде триггеров, и в виде запоминающих МОП-транзисторов.

Программируемые полем логические матрицы содержат ряды ячеек, соединенных каналами (рис 11.9).

209

Рис.11.9. Программируемые полем логические матрицы

В составе схемы имеются дополнительные блоки, осуществляющие по внешним командам подачу сигналов формирования соединений. Обычно это импульсы повышенного напряжения, вызывающие разрушение специального тонкого диэлектрика между полупроводниковыми слоями. В результате образуется требуемое соединение между ячейками и шинами матрицы.

Программирование схемы может быть получено и с использованием элементов оперативной памяти, встроенных в отдельные ячейки (модули), например, статических триггеров на КМОП. Достоинство такого программирования состоит в использовании обычной КМОП технологии. Подобные программируемые логические схемы (ПЛИС), за последнее десятилетие получили очень широкое развитие.