Для магистратуры / CMOS_IC

.pdf

140

Примечание: В скобках для сравнения даны времена задержки инвертора

3.2. Параметры быстродействия вентилей.

Для оценки быстродействия логических схем необходимы упрощенные макромодели вентилей, параметры которых просто определить по их структуре и размерам транзисторов, а при необходимости измерить экспериментально.

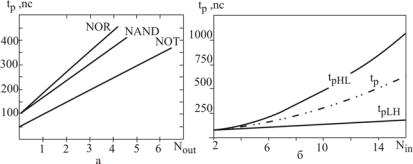

На задержку вентиля tp оказывает влияние выходная цепь – коэффициент разветвления Nout (количество подключенных нагрузок) (рис.3.3,а) и входная цепь – коэффициент объединения Nin (количество входов) (рис.3.3,б).

Рис.3.3. Зависимость времени задержки tp различных вентилей от коэффициента разветвления (а) и от коэффициента объединения (б).

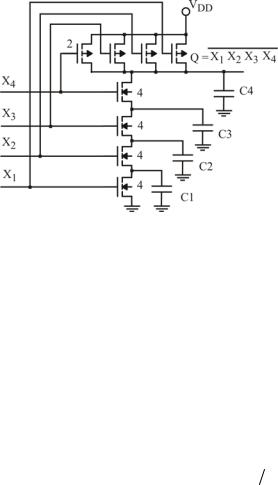

Задержка линейно зависит от числа выходов КМОП, потому что каждый выход (затвор) добавляет определенную емкость и нелинейно зависит от числа входов, так как входные транзисторы включены последовательно и представляют собой распределенную структуру (особенно при большом их количестве). Так, в схеме NAND4 (рис.3.4), tp ~ (С1 + 2 С2 + 3С3 + 4С4), поскольку каждый последующий конденсатор разряжается через возрастающее сопротивление.

В общем случае задержка КМОП-вентиля может быть представлена в виде

tp = a1Nin +a2 Nin2 +a0 Nout , |

(3.1) |

где a0, a1, a2 – феноменологические коэффициенты.

С увеличением количества входов резко растет время, что ограничивает применение многовходовых КМОП-вентилей. Обычно используют вентили с количеством входов не более четырех.

141

Рис.3.4. Схема многовходового вентиля – NAND4 c паразитными емкостями.

Задержку, зависящую от входной цепи, назовем внутренней (па-

разитной) задержкой: tpin = a1 Nin + a2 (Nin)2, а задержку, зависящую от выходной цепи, назовем внешней (нагрузочной): tpout = a0 Nout. Выражение

(3.1) запишем в виде

tp = tpin + tpout |

(3.1,а) |

При подаче сигнала на вход согласованного вентиля сигнал на выходе появляется с задержкой, не превышающей максимальной задержки tp. У несогласованного вентиля необходимо рассматривать две задержки: максимальную задержку включения (перехода из 0 в 1 – 0↑1) и максимальную задержку выключения (перехода из 1 в 0 – 1↓0).

Внешняя задержка пропорциональна величине емкости нагрузки Cout и может быть выражена через задержку вентиля tg, нагруженного на внешнюю емкость, равную его входной емкости Cin:

tp = tpin + tpout = tpin Cout Cin |

(3.1,б) |

Если входы вентиля несимметричны или имеют разные входные емкости, то и задержки по разным входам будут различны.

3.3. Эквивалентный инвертор

Анализ схем на произвольных вентилях удобно свести к анализу схем на инверторах – эквивалентных вентилях, для которых уже были получены оценки быстродействия, т.е. было установлено, что для цепочки КМОП-инверторов оптимальная нагрузка отдельного каскада равна четырем. С этой целью представим tg через задержку согласованного инвертора t0:

142

tg = (CgateRgate CinvRinv )t0 = gt0 . |

(3.2) |

Введем безразмерные величины: g = (Cgate Rgate / Cinv Rinv) – логическая нагрузка;

h = Cout / Cin, – электрическая нагрузка; f = tpout / t0,– нагрузочная задержка; p = tpin / t0, – паразитная нагрузка; d = tp / t0, – задержка (общая). Теперь задержку вентиля (3.1,б) можно представить в виде безразмерной задержки эквивалентного инвертора

d = p + f = p + gh |

(3.3) |

Таким образом, цепочку вентилей можно заменить цепочкой эквивалентных инверторов с задержками согласно (3.3).

Цепочка из N последовательных вентилей с возрастающим аспектным отношением транзисторов, равным n, позволяет передать двоичный сигнал с емкости Сin на емкость Cout

N

Cout ∏gi = Cin nN (3.4) i=1

c задержкой

N

td = ∑tdi i

Если же сигнал в цепочке разветвляется с коэффициентом раз-

ветвления b = (Con+Coff) / Con, (Con – емкость нагрузки в цепочке, Coff – емкость нагрузки вне цепочки), то (3.4) приобретает вид

N

Cout ∏gibi = Cin nN . (3.4.а) i=1

Таким образом, возрастание логической нагрузки вентилей и наличие разветвлений эквивалентно увеличению нагрузки.

3.4 Варианты вентилей

Параметры быстродействия вентиля (логическая нагрузка g, паразитная задержка p) зависят от принципа положенного в основу его построения. В согласованных вентилях за основу принято равенство максимальных выходных сопротивлений (они обеспечивают одинаковые задержки переключения); в гармонических вентилях – минимальное среднее выходное сопротивление (они обеспечивают минимальную среднюю задержку переключения); в «минимальных» вентилях согласованность максимальных выходных сопротивлений с выходным сопротивлением минимального инвертора (они обеспечивают минимальную задержку переключения из единицы в ноль).

143

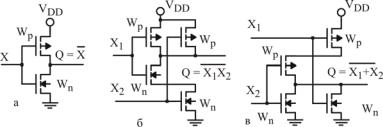

Простейшие КМОП-вентили (рис.3.5), характеризуются шириной каналов n-МОП и p-МОП.

Рис.3.5. Простейшие вентили: а – NOT; б – NAND2; в – NOR2

Связь параметров быстродействия с шириной каналов простейших КМОП-вентилей приведена в табл.3.2

Параметры быстродействия |

|

|

|

Таблица 3.2 |

|

||||||

различных вентилей |

|

|

|

|

|

||||||

Пара- |

Согласованные |

Гармонические |

|

Минимальные |

|

||||||

метр |

N |

N |

N |

N |

N |

|

N |

N |

N |

|

N |

|

O |

A |

O |

O |

A |

|

O |

O |

A |

|

O |

|

T |

N |

R |

T |

N |

|

R |

T |

N |

|

R |

|

|

D |

2 |

|

D |

|

2 |

|

D |

|

2 |

|

|

2 |

|

|

2 |

|

|

|

2 |

|

|

Wp |

2 |

2 |

4 |

1.41 |

2 |

|

2 |

1 |

1 |

|

2 |

Wn |

1 |

2 |

1 |

1 |

2 |

|

1 |

1 |

2 |

|

1 |

p |

1 |

2 |

2 |

0.8 |

2 |

|

4/3 |

2/3 |

4/3 |

|

4/3 |

gu |

1 |

4/3 |

5/3 |

1.15 |

4/3 |

|

2 |

4/3 |

2 |

|

2 |

gd |

1 |

4/3 |

5/3 |

0.81 |

4/3 |

|

1 |

2/3 |

1 |

|

1 |

gavg |

1 |

4/3 |

5/3 |

0.98 |

4/3 |

|

3/2 |

1 |

3/2 |

|

3/2 |

Примечание: gu – логическая нагрузка единицы; gd – логическая нагрузка нуля; gavg – средняя логическая нагрузка.

Унесогласованных вентилей выходное сопротивление, а значит,

илогическая нагрузка зависит от выходного сигнала.

Паразитная задержка и логическая нагрузка увеличиваются с возрастанием сложности вентилей.

144

Глава 4. Комбинационные логические схемы

Комбинационная логическая схема преобразует входные двоичные сигналы в выходные двоичные сигналы в соответствии с логической функцией. В стационарном состоянии при установившихся входных напряжениях (после окончания переходных процессов) выходные напряжения определены однозначно и не зависят от предыстории.

В отличие от вентиля логическая схема имеет несколько выходов и, как правило, не сводится к набору независимых вентилей. Как и многие вентили, логическая схема допускает различные варианты реализации и методы синтеза, в том числе на уровнях:

транзисторном; вентильном;

блочном (из более простых логических схем).

При проектировании логических схем в качестве критериев оптимизации наиболее часто выступают:

быстродействие; потребляемая мощность;

площадь, занимаемая схемой на кристалле.

При проектировании КМОП-схем необходимо учитывать определенные особенности, в том числе:

1)возможность синтезировать сложные функции сопровождается ограничением числа ярусов и снижением быстродействия;

2)каждое инвертирование входных сигналов требует отдельного вентиля (инвертора), поэтому схемы типа NAND, NOR реализуются проще, чем схема XOR;

3)КМОП-схемы не допускают объединения по выходу, выполнения проводных функций.

Достоинствами комбинационных КМОП-схем (и вентилей) явля-

ются:

1)отсутствие потребления в статике;

2)полный размах выходного напряжения;

3)связь выхода через открытый ключ с питанием;

4)высокий запас помехоустойчивости;

5)простота проектирования.

Комбинационные КМОП-схемы имеют и недостатки, часть которых следует из достоинств:

1)удвоение количества входов (n-МОП и p-МОП);

2)различие в параметрах транзисторов (p-МОП «слабее» n- МОП);

3)наличие сквозных токов при переключении;

4)зависимость задержки от входов и предыстории.

145

4.1. Типовые комбинационные КМОП-схемы

Драйверы. В качестве драйверов (магистральных усилителей) можно использовать обычные КМОП-вентили и инверторы с большим аспектным отношением транзисторов.

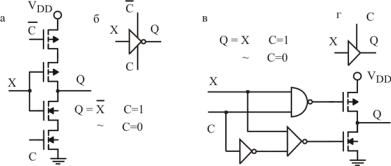

В ряде случае целесообразно объединять драйверы (и просто вентили) по выходу. В стандартных КМОП-вентилях при таком объединении могут постоянно протекать сквозные токи. Для исключения сквозных токов необходимо использовать специальные КМОП-схемы с третьим состоянием (тактируемые КМОП) (рис.4.1). В таких схемах тактовый импульс может быть введен непосредственно в блоки вентиля (рис.4.1,а), а может коммутировать входной сигнал с помощью других вентилей (

рис.4.1,в).

Рис.4.1. КМОП-вентили с третьим состоянием: а – с парафазным тактированием; б

– его условное обозначение; в – с однофазным тактированием; г – его условное обозначение.

В обоих случаях при отсутствии сигнала управления (С = 0) выход отсоединен от источника питания. Схема сохраняет на выходе предыдущее состояние в течение длительного времени, определяемого токами утечки. При объединении таких схем по выходу и подаче управления только на один из объединенных вентилей на общем выходе будет проинвертированный (рис4.1,б) или прямой (рис.4.1,г) вход выбранного вентиля.

Подобные схемы используют в мультиплексорах, выходных каскадах ИС и др.

Шифратор преобразует код, содержащий только одну единицу, в двоичный код.. Он сокращает количество сигнальных проводников по логарифмическому закону. При m входах шифратора у него не более M = log2(m) выходов. Поскольку в исходном коде присутствует ограниченное

146

количество комбинаций, то построение КМОП-шифратора упрощается. В его схемах блоки р могут не быть комплементарны блокам n. В качестве

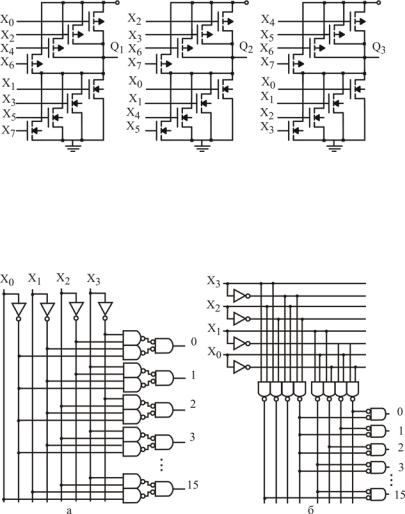

Рис.4.2. Восьмивходовой КМОП шифратор.

примера приведем восьмивходовой КМОП-шифратор (рис.4.2). Дешифратор выполняет обратную операцию. Для каждой вход-

ной комбинации M разрядного числа он возбуждает (переводит в состояние единицы) одну выходную шину из m = 2М возможных, рис.4.3.

Рис.4.3. Дешифраторы: а – одноступенчатый; б – двухступенчатый

Формально каждая выходная шина является выходом М-входовой схемы И. Таких вентилей в составе дешифратора m = 2М. При малых М подобная линейная одноступенчатая конструкция дешифратора оправда-

147

на. С возрастанием М аппаратурные затраты растут экспоненциально, что приводит к необходимости использовать многоступенчатые дешифраторы: матричные (прямоугольные), пирамидальные, комбинированные.

На рис.4.3 приведены модификации дешифратора с М = 4.

На входах обоих дешифраторов дополнительно формируются проинвертированные сигналы.

Водноступенчатом дешифраторе (рис.4.3,а) все 16 возможных кодовых комбинаций поступает на четырехвходовые схемы И(NAND4). Схемы NAND4 построены на NAND2 и NOR2.

Вдвухступенчатом (матричном) дешифраторе (рис.4.3,б), введены два предварительных дешифратора на два входа. При этом у каждого из них возбужден только один выход. Выходы предварительных дешифраторов подаются на вторую ступень из схем NOR2.

Мультиплексор (MUX) преобразует параллельный код в после-

довательный (во времени) (рис.4.4). На его входы подаются сигналы X1 – X4 и импульсы управления F1 – F4, следующие один за другим без перекрытия. Выход схемы Q имеет вид

Q = X1F1 X2 F2 X3F3 X4 F4 = X1F1 + X2 F2 + X3F3 + X4 F4 .

На выход Q сигналы поступают последовательно со сдвигом во времени.

Рис.4.4. Мультиплексор – демультиплексор.

Демультиплексор (DEMUX) выполняет операцию обратную мультплексированию – преобразует последовательный код в параллельный (cм. рис.4.4). Входная последовательность на его входах преобразуется в выходные сигналы. Комбинационная схема демультиплексора сохраняет сдвиг сигналов во времени, введенный мультиплексором. Для их совмещения во времени требуются схемы с памятью.

4.2. Сумматор.

Одноразрядный сумматор (SUM)– одна из широко распространенных логических схем, часто являющаяся библиотечным элементом. Его логическая функция

148 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S = ABC +ABC +ABC +ABC, |

(4.1) |

|||||||||||||

|

|

|

|

|

|

|

|

|||||||

C0 = ABC |

+ABC +ABC +ABC , |

(4.2) |

||||||||||||

где S – выход суммы; C0 –выход переноса; A – первое слагаемое; B – второе слагаемое; С – входной перенос.

На основе этих формул можно построить одноразрядный сумматор в виде двух независимых вентилей, реализующих функции (4.1) и (4.2). Однако это будут неоптимальные схемы, так как в их составе присутствуют четырехъярусные вентили. Общее количество транзисторов в них равно 3×4×2×2 = 48 .

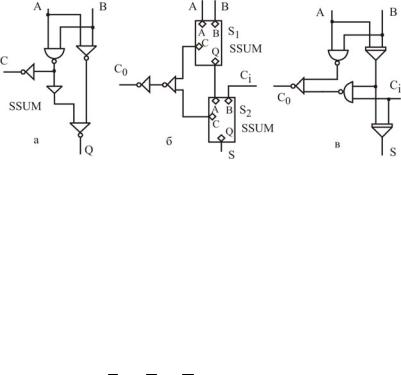

Известны более эффективные модификации одноразрядных сумматоров (рис.4.5). Часто такие сумматоры строят на основе полусуммато-

ров (SSUM), реализующих функции Q = XOR (A,B) и C = AB

(рис.4.5,а).

Рис.4.5. Сумматоры: а – полусумматор; б – одноразрядный сумматор на основе полусумматоров; в – одноразрядный сумматор на основе XOR.

Соединение двух полусумматоров и схемы ИЛИ (рис.4.5,б) дает одноразрядный сумматор. Фактически, в полусумматорах реализована функция XOR и даже с меньшими затратами, чем в библиотечном элементе, но она несимметрична. Кроме того, в этой модификации сумматора от входов А и В до выхода переноса С0 четыре элемента, а в схеме рис.4.5,в – таких элементов два. Поэтому, несмотря на большие затраты (44 транзистора вместо 32), схема на симметричных XOR (рис.4.5,в) более подходит для построения многоразрядных сумматоров, где задержка цепи переноса является определяющей.

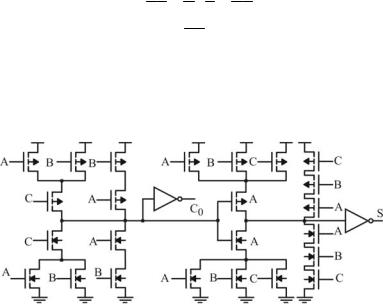

Исходные выражения (4.1) и (4.2) можно преобразовать к виду

C0 = ABC + ABC + ABC + ABC = AB + BC + AC = (4.3) (A + B)(B + C)(A + C)

149

S = ABC + ABC + ABC + ABC =

(4.4)

(A + B + C)CO + ABC

Полученные выражения с точностью до инвертирования достаточно просто реализуются двумя взаимосвязанными КМОП-вентилями. Причем в силу симметрии блок р и блок n не являются комплементарными, но сохраняют главное свойство КМОП – отсутствие тока в статике. Полный сумматор такого типа содержит всего 28 транзисторов (рис.4.6).

Рис.4.6 Комбинационный одноразрядный сумматор

Параллельный сумматор .Соединением нескольких одноразрядных сумматоров получают параллельный сумматор, в котором выход переноса C0 соединен со входом переноса следующего разряда Ci. При подаче на входы А и B многоразрядных чисел в параллельном коде результат на выходе S устанавливается после прохождения сигнала переноса. Максимально возможная длина переноса равна разрядности суммируемых чисел. Время переноса является определяющим. Поэтому важно минимизировать количество вентилей в цепи переноса. У вышерассмотренных одноразрядных сумматоров при распространении переноса он в каждом разряде проходит через два вентиля.

Преобразованием логической функции сумматора можно упростить цепь переноса. Сама функция суммы остается без изменений

S = XOR (Ci, P) |

(4.5) |

P = XOR (A, B) |

(4.5,а) |

В ранее рассмотренной модификации сумматора перенос выступал равноправно со слагаемыми. Однако в связи с тем, что именно он определяет быстродействие в параллельном сумматоре, его целесообразно выделить особо. Вводятся функция генерации переноса G = A B и функ-