- •Introduction to Digital Integrated Circuit Design

- •Aims and Objectives

- •Course Outline

- •Recommended Books

- •Supporting Material

- •Design Project

- •Assessment

- •Based on slides/material by…

- •Recommended Reading

- •Outline

- •Integrated Circuits

- •A Brief History

- •History of Integration

- •History of Technology

- •IP based SoC Design

- •Annual Sales

- •Any Device, Any Time, Anywhere

- •Outline

- •Implementation Methodologies

- •Full-custom

- •Custom Design - Layout

- •Standard-Cell–Based ICs

- •Full-custom Standard Cell

- •Routing a Standard Cell-based IC

- •Standard Cell Libraries

- •Macrocell-Based Design

- •Macrocell-Based Design Example

- •Gate-Array–Based ICs

- •Gate-Array–Based ICs (con’t)

- •Gate Array Approach - Example

- •Prewired Arrays

- •Programmable Logic Devices

- •EPLD Block Diagram

- •Field-Programmable Gate Arrays Fuse-based

- •Interconnect

- •Field-Programmable Gate Arrays RAM-based

- •RAM-based FPGA Basic Cell (CLB)

- •Outline

- •Design Abstraction Levels

- •ASIC Design Flow

- •ASIC Design Flow (con’t)

- •Outline

- •Moore’s Law

- •Moore’s Law – Intel Microprocessors

- •Evolution in Complexity

- •Scaling

- •Scaling Implications

- •Performance Improvement

- •Cost Improvement

- •Interconnect Woes

- •Reachable Radius

- •Dynamic Power

- •Static Power

- •Productivity

- •Very Few Companies Can Design High-End ICs

- •Less First Silicon Success and the Changing Rate of Failures

- •Physical Limits

- •Outline

- •Integrated Circuits Economics

- •Non-Recurring Engineering Costs (NRE)

- •Recurring Costs

- •Fixed Cost

- •New IC Design is Fairly Capital Intensive

- •Cost Breakdown

- •Outline

- •Silicon in 2010

- •ITRS

- •Summary

- •Journals and Conferences

- •Further Reading

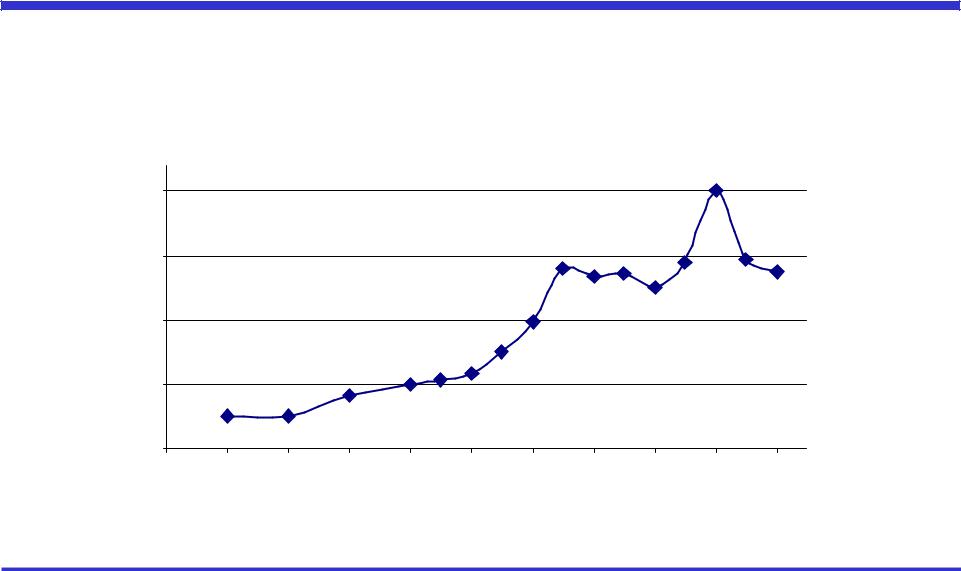

Annual Sales

1018 transistors manufactured in 2003

•100 million for every human on the planet

|

Global |

200 |

|

|

|

|

|

|

|

|

|

|

US$) of (Billions |

|

|

|

|

|

|

|

|

|

|

|

|

Billings Semiconductor |

150 |

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|

|

|

|

|

|

|

|

|

||

50 |

|

|

|

|

|

|

|

|

|

|

||

0 |

1984 |

1986 |

1988 |

1990 |

1992 |

1994 |

1996 |

1998 |

2000 |

2002 |

||

|

|

1982 |

||||||||||

|

|

|

|

|

|

|

Year |

|

|

|

|

|

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 17 |

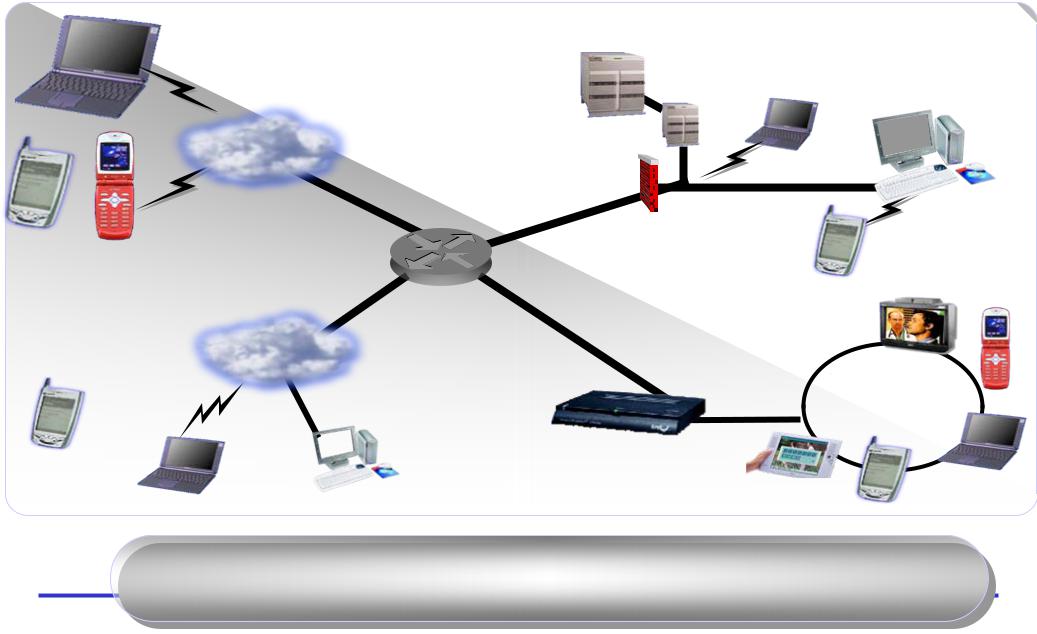

Any Device, Any Time, Anywhere

|

|

|

|

|

|

|

|

|

Cellular: Voice + Data |

|

|

|

|

|

|

|

|

@ the Office |

|

10/100/GbE0/100/GbE |

|||

|

|

|

|||||

|

Everywhere Else |

|

802.11b/a/g/a/g |

|

|

||

|

|

|

|

||||

|

|

|

|

|

|

||

|

@ Hotspots |

|

|

|

|

|

|

|

|

@ Home |

|

|

|||

|

802.11b/a/g |

Broadband |

|

|

802802..11b/a/g11b/a/g |

||

|

|

10/100 |

|

|

|||

|

|

|

|

CellularCellular |

|||

|

|

|

|

|

|||

|

|

|

|

|

|

||

|

|

|

|

|

Source: Greg Spirakis |

||

|

|

2010: 1.5 billion interconnected PCs,PCs, |

|

|

|||

|

|

|

|

PCs, |

|

|

|

Introduction |

2.5 billion interconnected PDAsPDAs |

Lecture 1 - 18 |

|

||||

|

|

|

|

PDAs |

|||

Outline

History

Implementation methodologies

Design flow

Technology scaling

VLSI/IC economics

Future trends

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 19 |

Implementation Methodologies

Digital Circuit Implementation Approaches

Custom |

Semi-custom |

Cell-Based |

Array-Based |

Standard Cells |

Macro Cells |

Pre-diffused |

Pre-wired |

|

Compiled Cells |

||||

|

(Gate Arrays) |

(FPGA) |

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 20 |