- •Introduction to Digital Integrated Circuit Design

- •Aims and Objectives

- •Course Outline

- •Recommended Books

- •Supporting Material

- •Design Project

- •Assessment

- •Based on slides/material by…

- •Recommended Reading

- •Outline

- •Integrated Circuits

- •A Brief History

- •History of Integration

- •History of Technology

- •IP based SoC Design

- •Annual Sales

- •Any Device, Any Time, Anywhere

- •Outline

- •Implementation Methodologies

- •Full-custom

- •Custom Design - Layout

- •Standard-Cell–Based ICs

- •Full-custom Standard Cell

- •Routing a Standard Cell-based IC

- •Standard Cell Libraries

- •Macrocell-Based Design

- •Macrocell-Based Design Example

- •Gate-Array–Based ICs

- •Gate-Array–Based ICs (con’t)

- •Gate Array Approach - Example

- •Prewired Arrays

- •Programmable Logic Devices

- •EPLD Block Diagram

- •Field-Programmable Gate Arrays Fuse-based

- •Interconnect

- •Field-Programmable Gate Arrays RAM-based

- •RAM-based FPGA Basic Cell (CLB)

- •Outline

- •Design Abstraction Levels

- •ASIC Design Flow

- •ASIC Design Flow (con’t)

- •Outline

- •Moore’s Law

- •Moore’s Law – Intel Microprocessors

- •Evolution in Complexity

- •Scaling

- •Scaling Implications

- •Performance Improvement

- •Cost Improvement

- •Interconnect Woes

- •Reachable Radius

- •Dynamic Power

- •Static Power

- •Productivity

- •Very Few Companies Can Design High-End ICs

- •Less First Silicon Success and the Changing Rate of Failures

- •Physical Limits

- •Outline

- •Integrated Circuits Economics

- •Non-Recurring Engineering Costs (NRE)

- •Recurring Costs

- •Fixed Cost

- •New IC Design is Fairly Capital Intensive

- •Cost Breakdown

- •Outline

- •Silicon in 2010

- •ITRS

- •Summary

- •Journals and Conferences

- •Further Reading

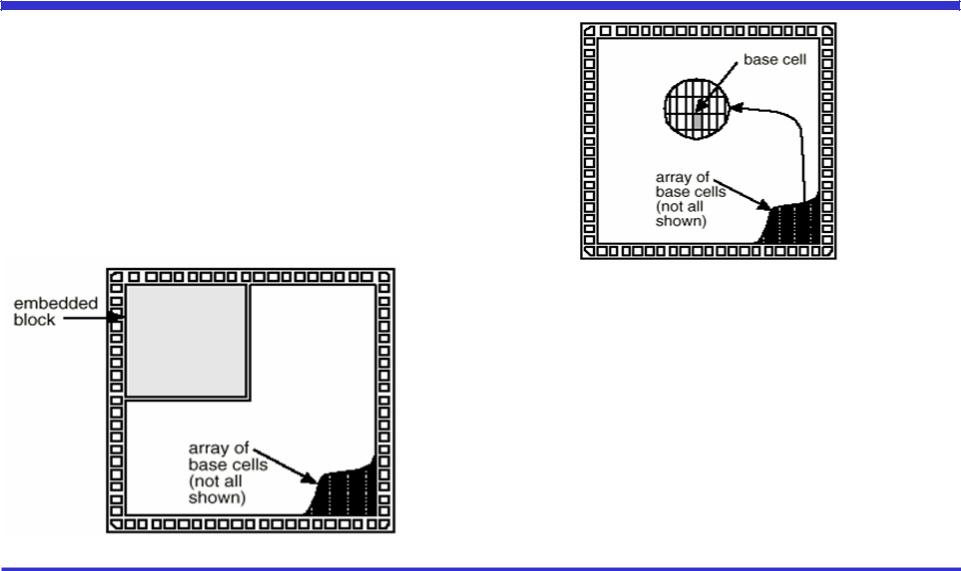

Gate-Array–Based ICs

A gate array, masked gate array, MGA, or prediffused array uses macros (books) to reduce turnaround time and comprises a base array made from a base cell or primitive cell. There are three types:

•Channeled gate arrays

•Channelless gate arrays

•Structured gate arrays

A channeled gate array

•The interconnect uses predefined spaces between rows of base cells

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 29 |

Gate-Array–Based ICs (con’t)

A channelless gate array (channelfree gate array, sea-of-gates array, or SOG array)

•Routing uses rows of unused transistors

An embedded gate array or structured gate array (masterslice or masterimage)

•Either channeled or channelless

•Custom blocks (the same for each design) can be embedded

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 30 |

Gate Array Approach - Example

|

polysilicon |

VD D |

|

|

metal |

GND |

possible |

contact |

Uncommited

Cell

In1 In2 In3 In4

Out

Committed

Cell

(4-input NOR)

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 31 |

Prewired Arrays

Categories of prewired arrays (or field-programmable devices):

•Fuse-based (program-once)

•Non-volatile EPROM based

•RAM based

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 32 |