- •Introduction to Digital Integrated Circuit Design

- •Aims and Objectives

- •Course Outline

- •Recommended Books

- •Supporting Material

- •Design Project

- •Assessment

- •Based on slides/material by…

- •Recommended Reading

- •Outline

- •Integrated Circuits

- •A Brief History

- •History of Integration

- •History of Technology

- •IP based SoC Design

- •Annual Sales

- •Any Device, Any Time, Anywhere

- •Outline

- •Implementation Methodologies

- •Full-custom

- •Custom Design - Layout

- •Standard-Cell–Based ICs

- •Full-custom Standard Cell

- •Routing a Standard Cell-based IC

- •Standard Cell Libraries

- •Macrocell-Based Design

- •Macrocell-Based Design Example

- •Gate-Array–Based ICs

- •Gate-Array–Based ICs (con’t)

- •Gate Array Approach - Example

- •Prewired Arrays

- •Programmable Logic Devices

- •EPLD Block Diagram

- •Field-Programmable Gate Arrays Fuse-based

- •Interconnect

- •Field-Programmable Gate Arrays RAM-based

- •RAM-based FPGA Basic Cell (CLB)

- •Outline

- •Design Abstraction Levels

- •ASIC Design Flow

- •ASIC Design Flow (con’t)

- •Outline

- •Moore’s Law

- •Moore’s Law – Intel Microprocessors

- •Evolution in Complexity

- •Scaling

- •Scaling Implications

- •Performance Improvement

- •Cost Improvement

- •Interconnect Woes

- •Reachable Radius

- •Dynamic Power

- •Static Power

- •Productivity

- •Very Few Companies Can Design High-End ICs

- •Less First Silicon Success and the Changing Rate of Failures

- •Physical Limits

- •Outline

- •Integrated Circuits Economics

- •Non-Recurring Engineering Costs (NRE)

- •Recurring Costs

- •Fixed Cost

- •New IC Design is Fairly Capital Intensive

- •Cost Breakdown

- •Outline

- •Silicon in 2010

- •ITRS

- •Summary

- •Journals and Conferences

- •Further Reading

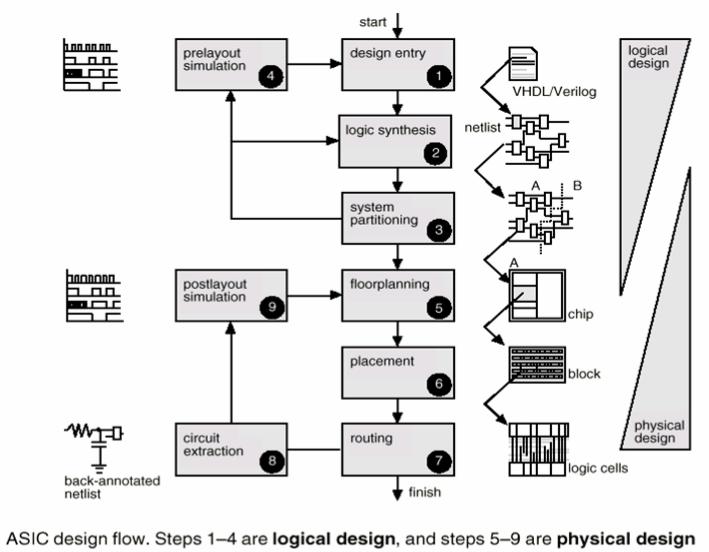

ASIC Design Flow

A design flow is a sequence of steps to design an ASIC

•Design entry.

•Logic synthesis.

•Pre-layout simulation.

•Floorplanning.

•Placement.

•Routing.

•Extraction.

•Postlayout simulation.

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 41 |

ASIC Design Flow (con’t)

|

|

|

|

|

|

|

|

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 42 |

|

Outline

History

Implementation methodologies

Design flow

Technology scaling

VLSI/IC economics

Future trends

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 43 |

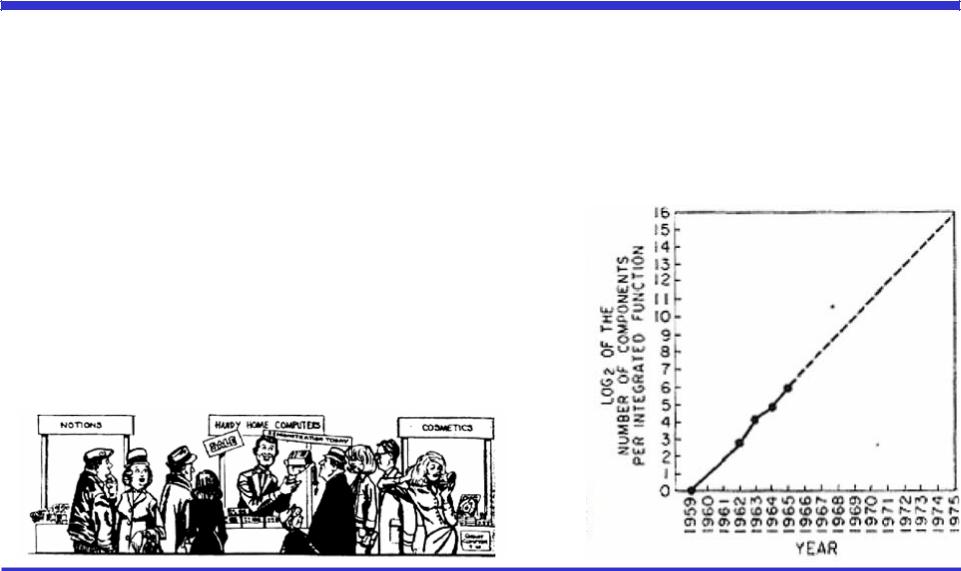

Moore’s Law

In 1965, Gordon Moore, co-founder of Intel, predicted the exponential growth of the number of transistors on an IC (number of transistors per square inch in ICs to double every year)

Predicted > 65,000 transistors by 1975!

In subsequent years, the pace slowed down a bit, but density has doubled approximately every 18 months, and this is the current definition of Moore's Law.

Growth limited by power

Most experts, including Moore himself, expect Moore's Law to hold for at least another two decades

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 44 |