- •Introduction to Digital Integrated Circuit Design

- •Aims and Objectives

- •Course Outline

- •Recommended Books

- •Supporting Material

- •Design Project

- •Assessment

- •Based on slides/material by…

- •Recommended Reading

- •Outline

- •Integrated Circuits

- •A Brief History

- •History of Integration

- •History of Technology

- •IP based SoC Design

- •Annual Sales

- •Any Device, Any Time, Anywhere

- •Outline

- •Implementation Methodologies

- •Full-custom

- •Custom Design - Layout

- •Standard-Cell–Based ICs

- •Full-custom Standard Cell

- •Routing a Standard Cell-based IC

- •Standard Cell Libraries

- •Macrocell-Based Design

- •Macrocell-Based Design Example

- •Gate-Array–Based ICs

- •Gate-Array–Based ICs (con’t)

- •Gate Array Approach - Example

- •Prewired Arrays

- •Programmable Logic Devices

- •EPLD Block Diagram

- •Field-Programmable Gate Arrays Fuse-based

- •Interconnect

- •Field-Programmable Gate Arrays RAM-based

- •RAM-based FPGA Basic Cell (CLB)

- •Outline

- •Design Abstraction Levels

- •ASIC Design Flow

- •ASIC Design Flow (con’t)

- •Outline

- •Moore’s Law

- •Moore’s Law – Intel Microprocessors

- •Evolution in Complexity

- •Scaling

- •Scaling Implications

- •Performance Improvement

- •Cost Improvement

- •Interconnect Woes

- •Reachable Radius

- •Dynamic Power

- •Static Power

- •Productivity

- •Very Few Companies Can Design High-End ICs

- •Less First Silicon Success and the Changing Rate of Failures

- •Physical Limits

- •Outline

- •Integrated Circuits Economics

- •Non-Recurring Engineering Costs (NRE)

- •Recurring Costs

- •Fixed Cost

- •New IC Design is Fairly Capital Intensive

- •Cost Breakdown

- •Outline

- •Silicon in 2010

- •ITRS

- •Summary

- •Journals and Conferences

- •Further Reading

Scaling Implications

Improved Performance

Improved Cost

Interconnect Woes

Power Woes

Productivity Challenges

Physical Limits

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 49 |

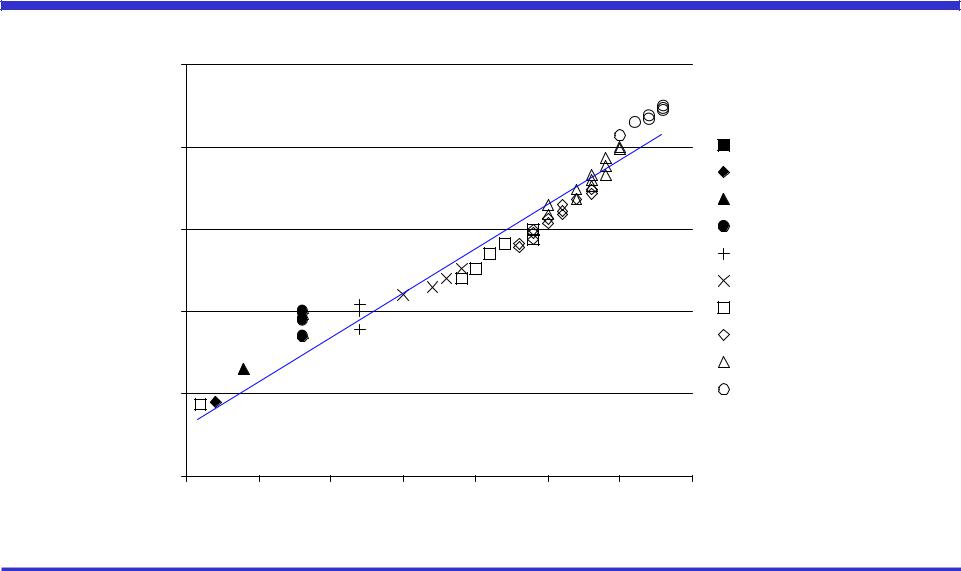

Performance Improvement

(MHz) Speed Clock

10,000

1,000

100

10

1

4004

8008

8080

8086

80286

Intel386

Intel486

Pentium

Pentium Pro/II/III

Pentium 4

|

|

|

|

|

|

|

|

|

1970 |

1975 |

1980 |

1985 |

1990 |

1995 |

2000 |

2005 |

|

Year

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 50 |

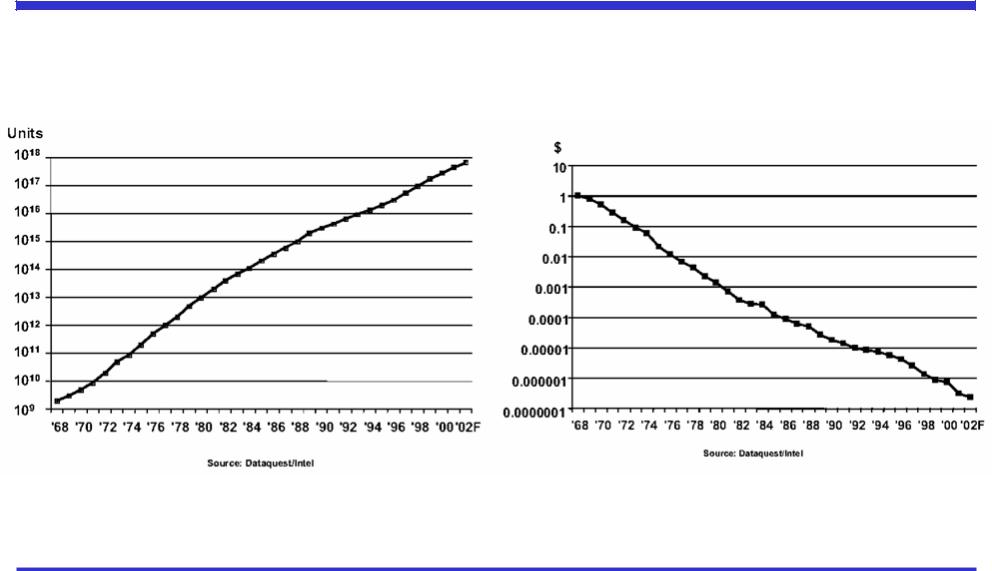

Cost Improvement

In 2003, $0.01 bought you 100,000 transistors

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 51 |

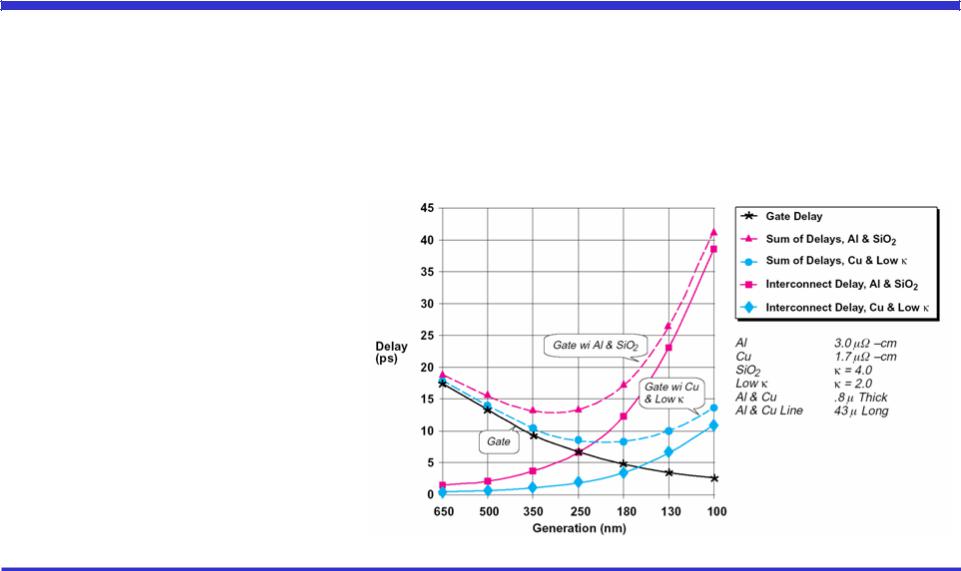

Interconnect Woes

SIA made a gloomy forecast in 1997

•Delay would reach minimum at 250 – 180 nm, then get worse because of wires

But…

•Misleading scale

•Global wires

100 kgate blocks ok

Introduction & Trends |

Introduction to Digital Integrated Circuit Design |

Lecture 1 - 52 |