- •Створення комбінаційних схем на контактних і безконтактних елементах

- •1.1. Мета роботи

- •1.2. Теоретична частина

- •Функція одного аргументу

- •Функції двох аргументів

- •1.2.2. Способи завдання фал

- •1.2.3. Форми представлення фал

- •1.2.4. Основні закони і тотожності алгебри логіки

- •1.2.5. Реалізація фал на контактах реле та інтегральних логічних елементах

- •Реалізація і позначення основних логічних операцій

- •1.3. Порядок виконання роботи

- •1.4. Зміст звіту

- •Варіанти фал

- •Мінімізація функцій алгебри логіки методом карт карно

- •2.1. Мета роботи

- •2.2. Теоретична частина

- •2.2.1. Функціонально повні системи фал, базис і його вибір

- •Приналежність фал двох змінних до «чудових» класів функцій

- •2.2.2. Мінімізація фал методом карт Карно

- •2.3. Порядок виконання роботи

- •2.4. Зміст звіту

- •Варіанти фал трьох змінних

- •Варіанти фал чотирьох змінних

- •Логічне проектування спеціальних комбінаційних схем

- •3.2.2. Дешифратори

- •3.3. Порядок виконання роботи

- •3.4. Зміст звіту

- •Варіанти завдання та значення параметрів

- •Відповідність комбінацій двійкового коду комбінаціям коду Грея

- •4.3. Порядок виконання роботи

- •Таблиця переходів

- •4.4. Зміст звіту

- •Вибір типу синтезуємого тригера і базису його реалізації

- •Синтез синхронних лічильних схем

- •5.1. Мета роботи

- •5.2. Теоретична частина

- •Матриці переходів для різних типів тригерів

- •Таблиця переходів і функцій збудження лічильника

- •5.3. Порядок виконання роботи

- •5.4. Зміст звіту

- •Варіанти лічильних схем, що синтезуються

- •Бібліографічний список

Синтез синхронних лічильних схем

5.1. Мета роботи

Метою даної роботи є оволодіння навиками логічного проектування синхронних лічильних схем.

5.2. Теоретична частина

Лічильником

називається схема, призначена для

зберігання числа і зміни його під дією

вхідних сигналів на одиницю або задану

константу. Кількість стійких станів

лічильної схеми називається її модулем.

Номер стану схеми відлічується

звичайно від

деякого початкового стану. Всі лічильні

схеми можна розподілити на синхронні

і асинхронні. У синхронних лічильників

на синхронізуючі входи всіх тригерів

одночасно поступають сигнали, підрахунок

яких і здійснює дана схема. У асинхронних

лічильників на синхронізуючі входи

тригерів поступають сигнали з виходів

інших тригерів або логічних елементів.

Під час проектування виникає

необхідність

в створенні лічильних схем з будь-яким

модулем ![]() .

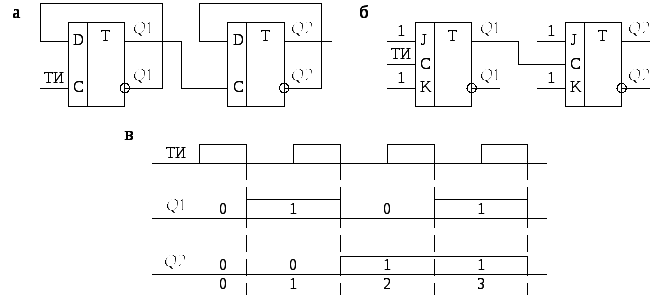

Приклад асинхронних лічильних схем

з

.

Приклад асинхронних лічильних схем

з ![]() ,

реалізованих

на JK- і

D-тригерах

і часова діаграма їх роботи, зображені

на рис. 5.1.

,

реалізованих

на JK- і

D-тригерах

і часова діаграма їх роботи, зображені

на рис. 5.1.

Рис.

5.1. Асинхронні

лічильні схеми:

а,б–

реалізація лічильників з![]() на D- і JK-тригерах;в– часова діаграма

їх роботи

на D- і JK-тригерах;в– часова діаграма

їх роботи

Асинхронні

лічильні схеми, зазвичай, більш прості

в реалізації, але їх проектування

у ряді випадків

ускладнюється відмінністю у внутрішній

організації тригерів, що використовуються

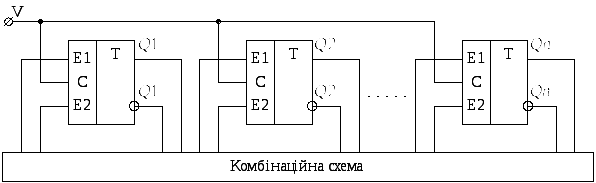

в схемі. Під час проектування синхронних

лічильників дана відмінність істотного

значення не має. Синхронний лічильник

з будь-яким модулем представляється

логічною структурою, що складається з

ряду тригерів і комбінаційної схеми

(рис. 5.2).

Комбінаційна

схема, таким

чином, проводить перетворення інформації,

що поступає на її входи, щоб з приходом

чергового прочитаного імпульсу здійснити

необхідний перехід лічильника з

попереднього стану в наступний. Функції

збудження кожного ![]() -го

тригера

-го

тригера ![]() визначені для

одного і того ж моменту часу, що і їх

аргументи (вхідні сигнали тригерів

лічильної схеми) і є перемикачами схеми.

Тому, для вибраного типу

тригерів, що

використовуються для побудови схем,

задача логічного проектування лічильника

полягає в складанні функцій збудження

кожного тригера і мінімізації їх в

заданому базисі.

визначені для

одного і того ж моменту часу, що і їх

аргументи (вхідні сигнали тригерів

лічильної схеми) і є перемикачами схеми.

Тому, для вибраного типу

тригерів, що

використовуються для побудови схем,

задача логічного проектування лічильника

полягає в складанні функцій збудження

кожного тригера і мінімізації їх в

заданому базисі.

Рис. 5.2. Зображення лічильної схеми

Для визначення функцій збудження кожного тригера схеми, використовують складені для даного типу тригера матриці переходів, приведені в табл. 5.1.

Таблиця 5.1

Матриці переходів для різних типів тригерів

|

Перехід |

Функції збудження | ||||||

|

|

|

|

|

|

|

| |

|

|

0 |

X |

0 |

|

|

X |

0 |

|

|

1 |

X |

1 |

1 |

1 |

0 |

1 |

|

|

X |

1 |

0 |

0 |

1 |

1 |

0 |

|

|

X |

0 |

1 |

|

|

0 |

X |

Кожний

рядок матриці переходів відповідає

одному з можливих переходів схеми

тригера. Значення функцій збудження

визначають на підставі логіки

функціонування даного типу тригера.

Якщо здійснюваний перехід повністю

визначається однією функцією збудження,

то як значення іншої записується символ

«Х», який вказує, що дана функція може

приймати будь-яке значення. Під час

запису матриці переходів для

DV-тригера

замість числових значень функцій

використані невизначені коефіцієнти

![]() ,

кожний з яких

може приймати значення «0» або «1».

Використання невизначених коефіцієнтів

обумовлено здійсненням тригером

переходів

,

кожний з яких

може приймати значення «0» або «1».

Використання невизначених коефіцієнтів

обумовлено здійсненням тригером

переходів ![]() ,

,

![]() при трьох

різних наборах функцій збудження

при трьох

різних наборах функцій збудження

![]() і

і

![]() .Так перехід

.Так перехід ![]() для

для

![]() може відбуватися

за будь-якого значення сигналу на

вході

може відбуватися

за будь-якого значення сигналу на

вході

![]() ,

а для

,

а для![]() –тільки за

подачі на вхід

–тільки за

подачі на вхід

![]() нуля.Отже,

якщо відповідне даному переходу значення

функції позначити через

нуля.Отже,

якщо відповідне даному переходу значення

функції позначити через

![]() ,

то для

,

то для

![]() необхідно

записати

необхідно

записати

![]() .

.

Методику логічного проектування синхронних лічильних схем розглянемо на прикладі синтезу двійково-десяткового лічильника на JK-тригерах. Для визначення функцій збудження кожного тригера схеми складається кодована таблиця переходів (табл. 5.2), в якій будь-якому стану схеми ставиться у відповідність певне двійкове число.

Таблиця 5.2