- •До лабораторних робіт

- •1 Інтегральні схеми. Короткий огляд

- •1.1 Основні технічні характеристики мікросхем

- •1.2 Типи логіки

- •1.3 Стандартні мікросхеми

- •1.4 Семіотика стандартних мікросхем

- •1.5 Мікросхеми-аналоги

- •1.6 Технічна документація

- •1.7 Типи корпусів імпортних мікросхем

- •Таблиця 1.4 – Приклади розмірностей (кількість виводів) деяких стандартних корпусів мікросхем

- •2 Варіанти індивідуальних завдань

- •2.1 Приклад виконання та індивідуальні варіанти проектної частини роботи

- •2.2 Каталог мікросхем для дослідницької частини роботи

- •2.3 Приклади формулярів завдань для дослідницької частини роботи

- •3 Програма electronics workbench

- •3.1 Комп'ютерне моделювання

- •3.2 Платформи комп'ютерного моделювання

- •3.3 Опис програми

- •3.4 Функціональний генератор

- •3.5 Генератор слів

- •3.6 Формування тестової послідовності

- •3.7 Логічний аналізатор

- •3.8 Логічний перетворювач

- •3.9 Введення таблиці істинності

- •3.10 Логічний аналіз комбінаційної схеми

- •4 Вказівки до виконання роботи

- •4.1 Хід роботи

- •4.2 Зміст звіту про виконання дослідницької частини

- •5 Контрольні питання

- •5.1 Контрольні питання

- •Література

2.3 Приклади формулярів завдань для дослідницької частини роботи

Таблиця 2.3 – Мікросхема 74154

|

4x16 decoder / demultiplexer |

74154 | |

|

|

4-to-16 Decoder/Demultiplexer truth table:

_ _ Inputs | Outputs G1 G2 | D C B A | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 ------|---------|-------------------------------------- 0 0 | 0 0 0 0 | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 | 0 0 0 1 | 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 | 0 0 1 0 | 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 | 0 0 1 1 | 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 | 0 1 0 0 | 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 0 0 | 0 1 0 1 | 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 0 0 | 0 1 1 0 | 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 0 0 | 0 1 1 1 | 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 0 | 1 0 0 0 | 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 | 1 0 0 1 | 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 0 0 | 1 0 1 0 | 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 0 0 | 1 0 1 1 | 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 0 0 | 1 1 0 0 | 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 0 0 | 1 1 0 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 | 1 1 1 0 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 0 | 1 1 1 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 | X X X X | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 | X X X X | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | X X X X | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | |

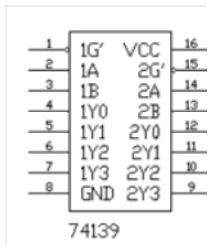

Таблиця 2.4 – Мікросхема 74139

|

Dual 2x4 decoder / demultiplexer |

74139 | |

|

|

2-to-4 decoder/demultiplexer truth table:

_ Select | Outputs Enable G B A | Y0 Y1 Y2 Y3 -------------------|--------------- 1 X X | 1 1 1 1 0 0 0 | 0 1 1 1 0 0 1 | 1 0 1 1 0 1 0 | 1 1 0 1 0 1 1 | 1 1 1 0 | |

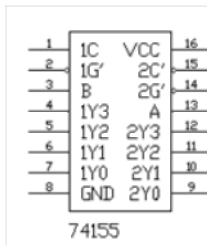

Таблиця 2.5 – Мікросхема 74155

|

Dual 2x4 decoder / demultiplexer |

74155 | |

|

|

Decoder/Demultiplexer truth table:

Select | Strobe | Data | Outputs A B | G' | C | Y0 Y1 Y2 Y3 -------|--------|------|----------------- X X | 1 | X | 1 1 1 1 0 0 | 0 | 1 | 0 1 1 1 0 1 | 0 | 1 | 1 0 1 1 1 0 | 0 | 1 | 1 1 0 1 1 1 | 0 | 1 | 1 1 1 0 X X | X | 0 | 1 1 1 1 | |

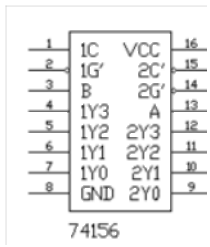

Таблиця 2.6 – Мікросхема 74156

|

Dual 2x4 decoder / demultiplexer |

74156 | |

|

|

This device contains two 2-to-4 decoders/demultipexers. For this IC, we recommend the LS-OC model for realistic performance.

Select | Strobe | Data | Outputs A B | G' | C | Y0 Y1 Y2 Y3 -------|--------|------|---------------- X X | 1 | X | 1 1 1 1 0 0 | 0 | 1 | 0 1 1 1 0 1 | 0 | 1 | 1 0 1 1 1 0 | 0 | 1 | 1 1 0 1 1 1 | 0 | 1 | 1 1 1 0 X X | X | 0 | 1 1 1 1

| |

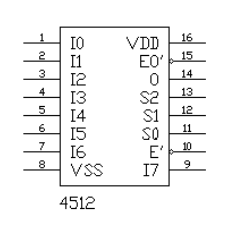

Таблиця 2.7 – Мікросхема 4512

|

8x1 multiplexer with 3-state out |

4512 | |

|

|

This device is a 8-input multiplexer with 3-state outputs.

_ _ Select Data EO E C B A I0 I1 I2 I3 I4 I5 I6 I7| O -------|---------|-------------------------------|----- 0 1 | X X X | X X X X X X X X | 0 0 0 | 0 0 0 | 0 X X X X X X X | 0 0 0 | 0 0 0 | 1 X X X X X X X | 1 0 0 | 0 0 1 | X 0 X X X X X X | 0 0 0 | 0 0 1 | X 1 X X X X X X | 1 0 0 | 0 1 0 | X X 0 X X X X X | 0 0 0 | 0 1 0 | X X 1 X X X X X | 1 0 0 | 0 1 1 | X X X 0 X X X X | 0 0 0 | 0 1 1 | X X X 1 X X X X | 1 0 0 | 1 0 0 | X X X X 0 X X X | 0 0 0 | 1 0 0 | X X X X 1 X X X | 1 0 0 | 1 0 1 | X X X X X 0 X X | 0 0 0 | 1 0 1 | X X X X X 1 X X | 1 0 0 | 1 1 0 | X X X X X X 0 X | 0 0 0 | 1 1 0 | X X X X X X 1 X | 1 0 0 | 1 1 1 | X X X X X X X 0 | 0 0 0 | 1 1 1 | X X X X X X X 1 | 1 1 X | X X X | X X X X X X X X | Z __ EO = Output Enable (Active-low) _ E = Enable input (Active-low)

Z = High impedance | |

Таблиця 2.8 – Мікросхема 4019

|

Quad 2x1 multiplexer |

4019 | |

|

|

This device contains four 2-input multiplexers.

SELECT INPUTS OUTPUT Sa Sb A0 B0 | O0 ---------------|------ L L X X | L H L L X | L H L H X | H L H X L | L L H X H | H H H H X | H H H X H | H H H L L | L | |