- •До лабораторних робіт

- •1 Інтегральні схеми. Короткий огляд

- •1.1 Основні технічні характеристики мікросхем

- •1.2 Типи логіки

- •1.3 Стандартні мікросхеми

- •1.4 Семіотика стандартних мікросхем

- •1.5 Мікросхеми-аналоги

- •1.6 Технічна документація

- •1.7 Типи корпусів імпортних мікросхем

- •Таблиця 1.4 – Приклади розмірностей (кількість виводів) деяких стандартних корпусів мікросхем

- •2 Варіанти індивідуальних завдань

- •2.1 Приклад виконання та індивідуальні варіанти проектної частини роботи

- •2.2 Каталог мікросхем для дослідницької частини роботи

- •2.3 Приклади формулярів завдань для дослідницької частини роботи

- •3 Програма electronics workbench

- •3.1 Комп'ютерне моделювання

- •3.2 Платформи комп'ютерного моделювання

- •3.3 Опис програми

- •3.4 Функціональний генератор

- •3.5 Генератор слів

- •3.6 Формування тестової послідовності

- •3.7 Логічний аналізатор

- •3.8 Логічний перетворювач

- •3.9 Введення таблиці істинності

- •3.10 Логічний аналіз комбінаційної схеми

- •4 Вказівки до виконання роботи

- •4.1 Хід роботи

- •4.2 Зміст звіту про виконання дослідницької частини

- •5 Контрольні питання

- •5.1 Контрольні питання

- •Література

Таблиця 1.4 – Приклади розмірностей (кількість виводів) деяких стандартних корпусів мікросхем

|

Тип корпусу |

Допустима кількість виводів |

|

DIP |

8,14,16,18,20,22,24,28,32,36,40,42,48,52,64 |

|

SIP |

7,8,9,12 |

|

SOIC |

8,14,24,28 |

|

TSOP |

24,26,28,32,40,44,48,50 |

|

LCC |

16,32,36,44,48,64 |

2 Варіанти індивідуальних завдань

2.1 Приклад виконання та індивідуальні варіанти проектної частини роботи

Методика проектування мікросхем на основі функціонального опису внутрішньої логічної схеми містить основні етапи:

Визначення таблиці істинності та умовного графічного позначення (УГП) заданого пристрою. Цей етап є базовим та, якщо виконаний коректно, полегшує виконання наступних етапів.

Формування функцій вихідних сигналів схеми на основі таблиці істиності.

Синтез логічної схеми пристрою.

Вибір відповідного типу корпусу та визначення цоколівки із позначенням зовнішніх вхідних та вихідних сигналів.

Увага! При виконанні лабораторної роботи останнім, п’ятим пунктом, по завершенні основної методики, є визначення за допомогою Інтернету декількох стандартних аналогів спроектованої мікросхеми.

Методика проектування докладно розглянута на прикладі виконання проектної частини (див. далі).

Варіанти індивідуальних завдань визначаються згідно номеру в журналі викладача.

Таблиця 2.1 - Варіанти індивідуальних завдань для проектування мікросхем

|

№ вар. |

Функціональний опис пристрою |

|

1, 11 |

Синхронний 4-розрязний лічильник |

|

2, 12 |

Синхронний JK-тригер із стартовими установками 0 та 1 |

|

3, 13 |

4-розрядний двійковий суматор |

|

4, 14 |

СинхроннийRS тригер із стартовими установками 0 та 1 |

|

5, 15 |

Двійково-десятковий дешифратор зі стробом |

|

6, 16 |

Двійково-десятковий лічильник |

|

7, 17 |

4-розрядний пріоритетний шифратор |

|

8, 18 |

Дешифратор-демультиплексор 2х4 |

|

9, 19 |

Здвоєний дешифратор 3х8 |

|

10, 20 |

Здвоєний мультиплексор 4х1 зі стробом |

|

21, 24 |

Два D-тригера «защіпка» |

|

22, 25 |

Здвоєна 4-розрядна схема контролю парності із стробом виборки |

|

23, 26 |

Синхронний D-тригер зі спрацьовуванням по фронту |

Приклад виконання проектної частини даної лабораторної роботи.

Постановка задачі: Спроектувати мікросхему для подвоєного дешифратора 2х4 із входом стробування.

|

|

Strobe E |

Select A/B CS |

Data |

Outputs | ||||

|

A |

B |

Y | ||||||

|

|

|

0 |

1 |

2 |

3 | |||

|

0 |

* |

* |

* |

0 |

0 |

0 |

0 | |

|

1 |

0 |

0 0 |

* |

1 |

0 |

0 |

0 | |

|

0 1 |

* |

0 |

1 |

0 |

0 | |||

|

1 0 |

* |

0 |

0 |

1 |

0 | |||

|

1 1 |

* |

0 |

0 |

0 |

1 | |||

|

1 |

* |

0 0 |

1 |

0 |

0 |

0 | ||

|

* |

0 1 |

0 |

1 |

0 |

0 | |||

|

* |

1 0 |

0 |

0 |

1 |

0 | |||

|

* |

1 1 |

0 |

0 |

0 |

1 | |||

1) Визначимо таблицю істинності та умовне графічне позначення (УМП)

пристрою, який потрібно спроектувати, на основі його функціонального опису, наданому в постановці задачі.

Сформуємо функції вихідних сигналів пристрою на основі таблиці істинності:

![]()

![]()

![]()

![]()

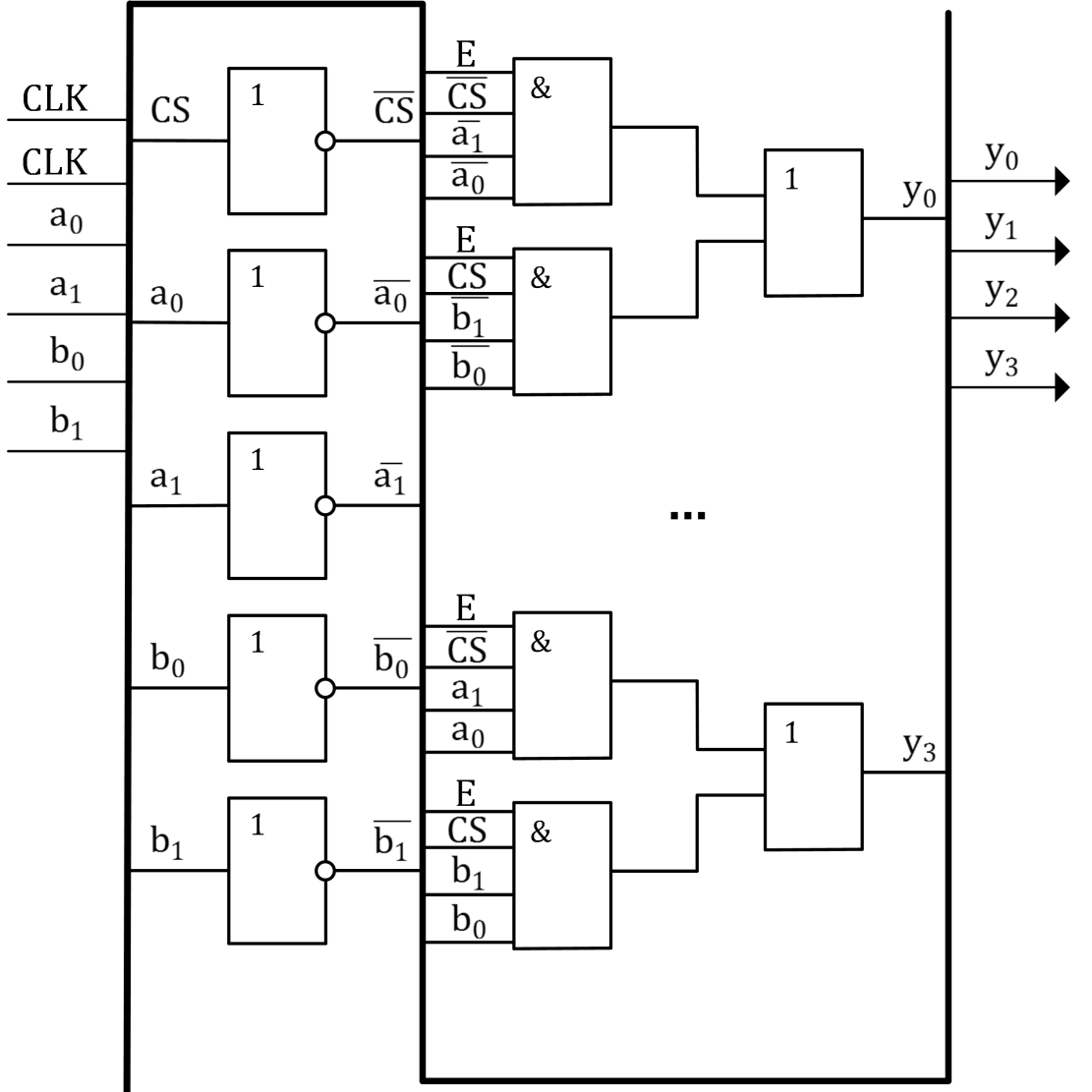

Синтезуємо логічну схему подвоєного дешифратора згідно з отриманими формулами.

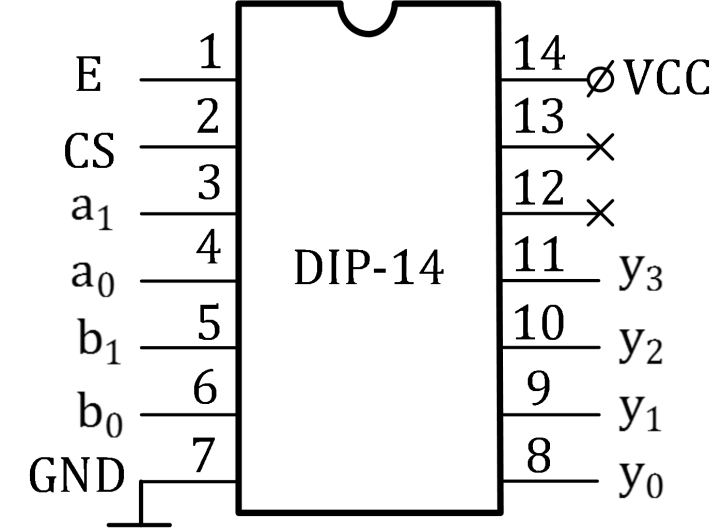

Оберемо відповідний DIP-корпус, для чого необхідно спершу визначити потрібне число виводів (пінов) в корпусі, яке позначимо

:

:

![]() ,

,

де ![]() –загальне число зовнішніх

виводів схеми,яке включає

в себечисло входів

–загальне число зовнішніх

виводів схеми,яке включає

в себечисло входів![]() ,

число виходів

,

число виходів![]() ,

а також входиGNDтаVCC.

,

а також входиGNDтаVCC.

Для даноїзадачірозрахуємо значення:

![]()

![]()

![]()

Таким чином, ![]() 2,отже, обираємо корпусDIP-14 (див.

табл.1.4).

2,отже, обираємо корпусDIP-14 (див.

табл.1.4).

Цоколівка мікросхеми із позначенням відповідних сигналів має вигляд:

Аналогами спроектированоїмікросхеми можна вважати:KP1533UD4,SN74ALS154,K155UD4.