- •Введение

- •Предмет, научные основы и краткая история развития дисциплины

- •Раздел I

- •Классификация дискретных устройств

- •Понятие о математическом описании дискретных устройств

- •Структура дискретных устройств (автоматов)

- •Глава 2 логические функции и их свойства

- •Логические функции и способы их задания

- •Основные операции алгебры логики и их релейная интерпретация

- •Элементарные логические функции и функциональная полнота систем логических функций

- •Техническая реализация логических функций

- •Глава 3 преобразование логических функций

- •Основные законы алгебры логики

- •Основные формулы равносильных преобразований

- •Аналитические формы представления логических функций

- •Задачи и сущность минимизации логических функций

- •Таблично-аналитический метод минимизации логических функций

- •Карты Карно

- •Минимизация логических функций по картам Карно

- •Решетка соседних чисел и обобщенных кодов

- •Минимизация логических функций на основе решетки соседних чисел и обобщенных кодов

- •Минимизация логических функций на основе поразрядного сравнения рабочих и запрещенных наборов

- •Минимизация логических функций методом поразрядного сравнения рабочих и запрещенных обобщенных кодов

- •Общие выводы

- •Раздел II

- •Анализ комбинационных дискретных устройств, построенных на бесконтактных элементах

- •Глава 5 описание и анализ условий функционирования дискретных устройств с памятью

- •Задачи и последовательность анализа дискретных устройств

- •Элементарные автоматы памяти (элементы памяти)

- •Анализ дискретных устройств с памятью, построенных на бесконтактных элементах

- •Переходные процессы в дискретных устройствах с памятью (состязания элементов памяти)

- •Переходные процессы в комбинационных дискретных устройствах. Причины возникновения состязания сигналов

- •Определение состязаний сигналов в комбинационных дискретных устройствах, построенных на бесконтактных элементах

- •Аналитический метод анализа переходных процессов в комбинационных ду

- •Устранение состязаний сигналов в комбинационных дискретных устройствах

- •Оглавление

- •Раздел I 4

- •Раздел II 64

Элементарные автоматы памяти (элементы памяти)

Для дискретных устройств с памятью характерным является наличие блока памяти, состоящего из отдельных элементов памяти, а также значительного числа контуров обратной связи.

При построении блоков памяти ДУ используются устройства, имеющие два устойчивых состояния. Такие устройства принято называть элементарными автоматами памяти или элементами памяти.

Простейшими элементами памяти являются различного рода задержки, позволяющие хранить информацию в течение такта. Отметим, что контур обратной связи также представляет собой задержку. Реализация памяти ДУ на задержке не всегда целесообразна, так как в общем случае структура получается сложной и, кроме того, задержка хранит информацию кратковременно (один такт).

Для неограниченного хранения информации применяются различного рода триггеры.

Задержки хранят информацию, поступившую на их вход, кратковременно, в течение одного такта. При снятии входного сигнала информация самопроизвольно исчезает. Триггеры фиксируют входные сигналы и после их окончания. Записанная в триггер информация может храниться неопределенное время. Для стирания записанной информации на вход триггера необходимо подавать определенный сигнал. Возможно как импульсное, так и потенциальное управление элементов памяти. Большинство элементов памяти на интегральных схемах требует потенциального управления. Аналогично выходные сигналы также могут быть как импульсными, так и потенциальными.

Триггеры с импульсным управлением весьма критичны к параметрам управляющих сигналов.

Наибольшее распространение в ДУ получили следующие элементы памяти:

элемент (линия) задержки на один такт;

триггер с раздельными входами;

триггер со счетным входом;

триггер с комбинированными входами.

Рассмотрим эти элементы памяти.

Э лемент

задержки (задержка) – это устройство,

предназначенное для задержки проходящих

через него сигналов на некоторое времяt, определяемое параметрами элемента.

На рис.5.2 приведены условные графические

обозначения элементов задержки

(D-триггер) с одним и несколькими

выходами. Цифры, стоящие возле выходов

на дополнительном поле, являются

условными обозначениями величины

задержки сигнала на каждом из выходов.

лемент

задержки (задержка) – это устройство,

предназначенное для задержки проходящих

через него сигналов на некоторое времяt, определяемое параметрами элемента.

На рис.5.2 приведены условные графические

обозначения элементов задержки

(D-триггер) с одним и несколькими

выходами. Цифры, стоящие возле выходов

на дополнительном поле, являются

условными обозначениями величины

задержки сигнала на каждом из выходов.

Условиями функционирования элемента задержки на один такт описываются таблицей переходов (табл.5.1) и таблицей выходов (табл.5.2). элемент задержки является автоматом Мура, его выходной сигнал определяется только состоянием автомата, и поэтому обе таблицы могут быть объединены в одну таблицу – отмеченную таблицу переходов (табл.5.3), в которой кружком отмечаем устойчивые такты (состояния). Отмеченная таблица переходов часто называется таблицей переходов-выходов.

|

Таблица 5.1 |

|

Таблица 5.2 |

|

Таблица 5.3 | |||||||

|

S(t) |

x(t) |

|

y(t) |

x(t) |

|

S(t) |

x(t) |

z(t) | |||

|

y(t) |

0 |

1 |

|

0 |

1 |

|

y(t) |

0 |

1 | ||

|

|

0 |

1 |

|

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

|

0 |

1 |

|

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

y(t+ 1) |

|

z(t) |

|

y(t+ 1),z(t) | |||||||

Таблица переходов-выходов для состояния автомата (линии задержки) в последующем такте y(t+ 1) представляет собой карту Карно.

Получим СДНФ функции переходов, как сумму кодов единичных клеток, образующих максимальный правильный контур:

![]()

Очевидной является функция выходов z(t) =y(t).

Таким образом для линии задержки (D-триггера) функция переходов:y(t+ 1) =x(t) илиy(t) =x(t- 1), а функция выходов:z(t) =y(t).

При решении задачи синтеза ДУ для получения логических функций, описывающих условия работы блока управления памятью, необходимо знать значения входных сигналов элементов памяти, которые обеспечивают требуемые изменения их состояний. Эти значения могут быть определены из таблицы переходов элемента памяти.

Однако для удобства определения значений входов строится специальная таблица, задающая значения входных сигналов для всех возможных пар состояний элементов памяти. Такая таблица носит название таблицы входов элемента памяти (ЭП). Строки таблицы входов ЭП соответствуют его состояниям в момент времени t, а столбцы – состояниям в момент времениt+ 1. В клетки таблицы входов записываются значения входных сигналов, вызывающие переход элемента памяти из состояния, соответствующего строке, в состояние, соответствующее столбцу.

Т аблица

входов (табл.5.4) для элемента задержки

построена на основании его таблицы

переходов (табл.5.1).

аблица

входов (табл.5.4) для элемента задержки

построена на основании его таблицы

переходов (табл.5.1).

|

Таблица 5.4 | ||

|

y(t) |

y(t+ 1) | |

|

0 |

1 | |

|

0 |

0 |

1 |

|

1 |

0 |

1 |

|

x(t) | ||

Функция возбуждения

элемента задержки имеет вид

![]() ,

т.е. его выходной сигнал на один такт

опережает его состояние, а следовательно,

и выходной сигнал.

,

т.е. его выходной сигнал на один такт

опережает его состояние, а следовательно,

и выходной сигнал.

Граф переходов элемента задержки представлен на рис.5.3.

Триггер с раздельными входами – это логический элемент с двумя устойчивыми состояниями, имеющий два входа: единичный вход S, служащий для записи информации в триггере, и нулевой входR– для стирания записанной в триггере информации.

П ри

значениях входовS= 1,R= 0

триггер принимает состояние 1 (y= 1),

а при значенияхS= 0,R= 1

– состояние 0 (y= 0). При входном

набореS=R= 0 состояние

триггера не изменяется и сохраняется

равным его предыдущему значению. Входной

наборS=R= 1 не

используется.

ри

значениях входовS= 1,R= 0

триггер принимает состояние 1 (y= 1),

а при значенияхS= 0,R= 1

– состояние 0 (y= 0). При входном

набореS=R= 0 состояние

триггера не изменяется и сохраняется

равным его предыдущему значению. Входной

наборS=R= 1 не

используется.

Условное графическое обозначение триггера с раздельными входами приведено на рис.5.4.

Триггер с раздельными входами часто называют триггером RS-типа (RS-триггером).

Условия функционирования триггера RS-типа описываются таблицей переходов (табл.5.5), таблицей выходов (табл.5.6), отмеченной таблицей переходов (табл.5.7) и таблицей входов (табл.5.8).

|

|

|

Таблица 5.5 |

|

|

Таблица 5.6 |

|

| ||||||||

|

|

|

y(t) |

S(t),R(t) |

|

|

y(t) |

S(t),R(t) |

|

| ||||||

|

|

|

00 |

10 |

01 |

11 |

|

|

00 |

10 |

01 |

|

| |||

|

|

|

0 |

0 |

1 |

0 |

– |

|

|

0 |

0 |

0 |

0 |

|

| |

|

|

|

1 |

1 |

1 |

0 |

– |

|

|

1 |

1 |

1 |

1 |

|

| |

|

|

|

y(t+ 1) |

|

|

z(t) |

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

Таблица 5.7 |

|

|

Таблица 5.8 |

|

| ||||||||

|

|

|

y(t) |

S(t),R(t) |

z(t) |

|

|

y(t) |

y(t+ 1) |

|

| |||||

|

|

|

00 |

10 |

11 |

01 |

|

|

0 |

1 |

|

| ||||

|

|

|

0 |

0 |

1 |

– |

0 |

0 |

|

|

0 |

0~ |

10 |

|

| |

|

|

|

1 |

1 |

1 |

– |

0 |

1 |

|

|

1 |

01 |

~0 |

|

| |

|

|

|

y(t+ 1),z(t) |

|

|

S(t),R(t) |

|

| ||||||||

Как видно из таблицы переходов, состояние триггера не изменяется, y(t+ 1) =y(t), если на оба входа схемы поступает сигнал, соответствующий логическому нулю (S=R= 0). При подаче на единичный вход сигнала, соответствующего логической единице (S= 1), а на нулевой вход сигнала, соответствующего логическому нулю (R= 0), происходит подтверждение предшествующего состояния, если триггер находился в единичном состоянии (y= 1), и переброс в единичное, если триггер находился в нулевом состоянии (y= 0).

При подаче сигналов S= 0 иR= 1 происходит подтверждение предшествующего состояния, если триггер находился в нулевом состоянии (y= 0), и переброс в нулевое состояние, если триггер в единичном состоянии (y= 1).

В случае одновременного поступления на

входы логических единиц (S=R= 1)

триггер принимает неопределенное

состояние. Поэтому ДУ с использованиемRS-триггеров должны строиться с

учетом исключения состояния входовS=R= 1, т.е. должно

выполняться условиеS·R= 0.

случае одновременного поступления на

входы логических единиц (S=R= 1)

триггер принимает неопределенное

состояние. Поэтому ДУ с использованиемRS-триггеров должны строиться с

учетом исключения состояния входовS=R= 1, т.е. должно

выполняться условиеS·R= 0.

Граф переходов RS-триггера представлен на рис.5.5.

Из табл.5.7, как из карты Карно, получим функцию переходов RS-триггера:

![]()

очевидно, что функция выходов z(t) =y(t).

Итак, окончательно получаем для RS-триггера с прямым управлением:

![]()

z(t) =y(t).

П ри

построении триггеров с раздельными

входами на интегральных логических

элементах нередко используются инверсные

значения управляющих сигналов, что

позволяет получить более простую

структуру. В этом случае переключение

триггера осуществляется сигналамиS= 1,R= 0 илиS= 0,R= 1, при входных сигналахS= 1,R= 1 триггер сохраняет предыдущее

состояние, а входная комбинацияS= 0,R= 0 является неиспользуемой

(

ри

построении триггеров с раздельными

входами на интегральных логических

элементах нередко используются инверсные

значения управляющих сигналов, что

позволяет получить более простую

структуру. В этом случае переключение

триггера осуществляется сигналамиS= 1,R= 0 илиS= 0,R= 1, при входных сигналахS= 1,R= 1 триггер сохраняет предыдущее

состояние, а входная комбинацияS= 0,R= 0 является неиспользуемой

(![]() ).

Условное графическое обозначениеRS-триггера с инверсным управлением,

приведено на рис.5.6.

).

Условное графическое обозначениеRS-триггера с инверсным управлением,

приведено на рис.5.6.

|

|

|

Таблица 5.9 |

|

|

Таблица 5.10 |

|

| ||||||||

|

|

|

y(t) |

S(t),R(t) |

z(t) |

|

|

y(t) |

y(t+ 1) |

|

| |||||

|

|

|

00 |

10 |

11 |

01 |

|

|

0 |

1 |

|

| ||||

|

|

|

0 |

– |

0 |

0 |

1 |

0 |

|

|

0 |

1~ |

01 |

|

| |

|

|

|

1 |

– |

0 |

1 |

1 |

1 |

|

|

1 |

10 |

~1 |

|

| |

|

|

|

y(t+ 1),z(t) |

|

|

S(t),R(t) |

|

| ||||||||

Отмеченная таблица переходов и таблица входов приведены в таблицах 5.9 и 5.10.

Функция переходов (характеристическое уравнение) RS-триггера с инверсным управлением имеет вид:

![]()

функция выходов: z(t) =y(t).

Граф переходов представлен на рис.5.7.

У ниверсальныйJK-триггер – это логический элемент,

имеющий два входа: единичный входJи нулевой входK.

ниверсальныйJK-триггер – это логический элемент,

имеющий два входа: единичный входJи нулевой входK.

При значениях входов J=K= 0 состояние триггера не меняется и сохраняется равным его предыдущему значению. При значениях сигналовJ= 1,K= 0 триггер принимает состояние 1 (y= 1), а при значенияхJ= 0,K= 1 – состояние 0 (y= 0). При значениях сигналовJ=K= 1 триггер перебрасывается в противоположное состояние.

У словное

графическое обозначениеJK-триггера

приведено на рис.5.8, отмеченная таблица

переходов и таблица входов – в таблицах

5.11 и 5.12.

словное

графическое обозначениеJK-триггера

приведено на рис.5.8, отмеченная таблица

переходов и таблица входов – в таблицах

5.11 и 5.12.

|

|

|

Таблица 5.11 |

|

|

Таблица 5.12 |

|

| ||||||||

|

|

|

y(t) |

J(t),K(t) |

z(t) |

|

|

y(t) |

y(t+ 1) |

|

| |||||

|

|

|

00 |

10 |

11 |

01 |

|

|

0 |

1 |

|

| ||||

|

|

|

0 |

0 |

1 |

1 |

0 |

0 |

|

|

0 |

0~ |

1~ |

|

| |

|

|

|

1 |

1 |

1 |

0 |

0 |

1 |

|

|

1 |

~1 |

~0 |

|

| |

|

|

|

y(t+ 1),z(t) |

|

|

J(t),K(t) |

|

| ||||||||

Функции переходов и выходов JK-триггера имеют вид:

![]()

z(t) =y(t).

Граф переходов JK-триггера представлен на рис.5.9.

Триггером со счетным входом называется элемент памяти с двумя и более устойчивыми состояниями и одним входом x, изменяющий свое состояние на противоположное всякий раз, когда на вход поступает управляющий (счетный) сигналx= 1.

У словное

графическое изображение триггера со

счетным входом показано на рис.5.10.

словное

графическое изображение триггера со

счетным входом показано на рис.5.10.

В зависимости от технической реализации триггеры со счетным входом подразделяют на импульсные и потенциальные. У импульсных триггеров число устойчивых состояний равно двум, а входной сигнал имеет форму импульса, длительность которого строго определена и не превышает времени перехода триггера из одного устойчивого состояния в другое.

|

|

|

Таблица 5.13 |

|

|

|

|

Таблица 5.14 |

|

| |||||||

|

|

|

y(t) |

x(t) |

z(t) |

|

|

|

|

y(t) |

y(t+ 1) |

|

| ||||

|

|

|

0 |

1 |

|

|

|

|

0 |

1 |

|

| |||||

|

|

|

0 |

0 |

1 |

0 |

|

|

|

|

0 |

0 |

1 |

|

| ||

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

1 |

1 |

0 |

|

| ||

|

|

|

y(t+ 1),z(t) |

|

|

|

|

x(t) |

|

| |||||||

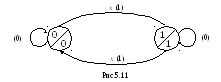

У словия

функционирования импульсного триггера

со счетным входом описываются в отмеченной

таблице переходов (табл.5.13) и таблице

входов (табл.5.14) и графом переходов

(рис.5.11).

словия

функционирования импульсного триггера

со счетным входом описываются в отмеченной

таблице переходов (табл.5.13) и таблице

входов (табл.5.14) и графом переходов

(рис.5.11).

Из табл.5.13 следует, что функция переходов триггера со счетным входом

![]()

а функция выходов

z(t) =y(t).

Триггер со счетным входом обычно называют триггером типа T(T-триггер).

В литературе описаны также и различные другие типы триггеров, функции переходов и выходов которых могут быть взяты при необходимости.

0

0

1

1