- •Министерство образования и науки

- •Содержание

- •Информационный процесс, Сигналы

- •Логические состояния

- •Системы счисления

- •Логические элементы и таблица истинности

- •Логическое сложение, дизъюнкция, элемент или

- •Логическое умножение, конъюнкция, элемент и

- •Логический элемент не, отрицание, инверсия

- •Минимизация логических выражений с помощью карт карно

- •Карта карно для двух переменных

- •Карта карно с тремя переменными

- •Карта карно для четырех переменных

- •Комбинационные функциональные схемы

- •Счетверенная двухвходовая схема выборки

- •Мультиплексоры

- •Сумматоры

- •Компараторы

- •Обратные преобразования, записанные в дополнительном коде

- •Арифметика в дополнительном коде

- •Последовательная логика

- •Регистры

- •Параллельно – параллельный четырехразрядный регистр на rs – триггерах

- •Счетный триггер

- •Счетчики

- •Счетчик на сложение

- •Счетчик на вычитание

- •Реверсивный счетчик

- •Счетчик заданной длины

- •Линейные дешифраторы

- •Линейный дешифратор на 10

- •Основы микропроцессорной техники Архитектура эвм

- •Работа эвм

- •Группировки бит

- •Буквенно-цифровой код

- •Тристабильные элементы

- •Структура оперативной памяти

- •Основы микропроцессорной техники

- •Архитектура простой эвм

- •Структура простейшей памяти

- •Состав команд

- •Структура типового микропроцессора

- •Функционирование Эвм

- •Микропроцессор. Поставляемая разработчиком документация

- •Использование регистра, адреса / данных

- •Этапы обработки требования прерывания в микропроцессоре

- •Указатель стека

- •Программирование микропроцессора Состав команд арифметических действий

- •Состав команд логических операций

- •Команда или

- •Команда или – исключающее

- •Команда циклического сдвига с переносом

- •Состав команд операций передачи данных

- •Состав команд операций ветвления

- •Состав команд операций вызова подпрограмм и возврата в основную программу

- •Программирование микропроцессара запись программы

- •Ветвление программ

- •Использование подпрограмм

- •Интерфейс микропроцессора

- •Основные элементы интерфейса портов ввода/вывода

- •Список литературы

Последовательная логика

Все схемы, рассматриваемые ранее, строились на основе комбинационной логике. Для таких схем состояние выхода полностью определяется текущим состоянием выходов, то есть у таких схем отсутствует предыстория (предыдущее состояние не влияет на текущее).

Наличие памяти позволяет строить системы с очень большими возможностями. Под элементом памяти мы будем понимать устройство, которое под действием управляющих сигналов может сохранять свое состояние на выходе неопределенно долгое время, а так же текущее состояние этого элемента неким заданным образом связано с предысторией.

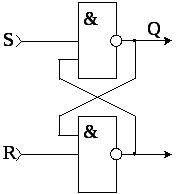

RS – триггер

Многие виды памяти в цифровых системах реализуются на основе триггеров.

Триггер – цифровое устройство с двумя

устойчивыми состояниями выхода, причем

состояние выхода определяется текущим

состоянием входов и предыдущим состоянием

триггера. RS– триггер

имеет два входаS(Set)

иR(Reset), а

так же имеет два выходаQ– прямой и

![]() -

инверсный.

-

инверсный.

|

R |

S |

Q |

|

|

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

|

0 |

0 |

1 |

0 |

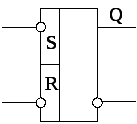

На схемах электрических принципиальных RS– триггер изображают:

Если мы говорим, что в триггер записана 1, то это означает, что под действием управляющих входов Q= 1.

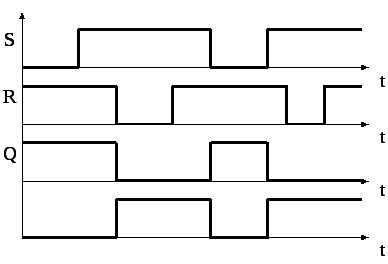

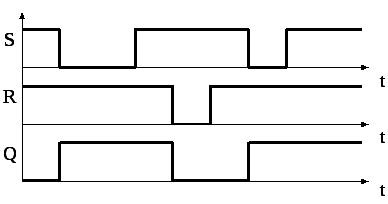

Для анализа работы этой схемы удобно пользоваться диаграммой состояния.

Важной особенностью работы триггеров является то, что, как правило, мы не знаем состояние триггера в момент включения, поэтому либо принимаем какие-то специальные меры или если это не важно, то произвольно задаются любым состоянием.

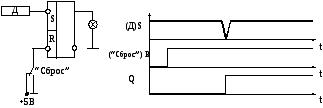

Рассмотрим примеры применения RS– триггера:

Фиксация кратковременных событий.

В различных научных и технологических задачах встречаются ситуации, когда некое важное событие существует очень короткое время, а знание о том, произошло это событие или нет, является очень важным. Используя свойства RS– триггера сохранять свое предыдущее состояние позволяет решить эту задачу.

В начальный момент времени кратковременно нажимаем кнопку «Сброс», т. е. на R– вход подаем 0. В это время на выходе датчика Д = 1 (событие не произошло), т. е.S=1,R=0. В соответствии с правиламиRS– триггераQ=0. Это состояние будет сохраняться до тех пор, пока на выходе датчика не появится сигнал 0. В этот момент времениS=0, аR=1. Триггер “опрокинется” (изменит свое состояние на противоположное)Q=1. После того, как сигнал кончился (S=1,R=1) и триггер сохраняет свое предыдущее состояние до того момента, пока мы не нажмем кнопку «Сброс».

2. Бездребезговая кнопка.

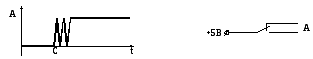

Механические контакты переключателей изготавливаются, как правило, из упругих токопроводящих материалов, а это означает, что в силу своей упругости контакт при переключении может несколько раз отскочить и вернуться в исходное положение. Если такая кнопка находится в системе управления, то эта система воспримет ситуацию дребезга как несколько нажатий на кнопку, а это приведет к неадекватной реакции.

На диаграмме это выглядит так:

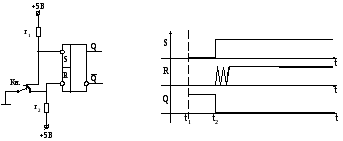

Используя наши знания RS– триггера можно построить схему, исключающую дребезг механических контактов.

Схема включает в себя следующие элементы: RS– триггер, резисторыr1иr2, кнопка (Кн.), дребезг которой необходимо подавить. Резисторыr1иr2одним своим выводом подключены к источникам ЭДС +5В (1), а другим к выходамRиSсоответственно. Подвижный контакт кнопки подключен к Земле (0). В исходном состоянии подвижный контакт кнопки через нормально замкнутый контакт подключен кS– входу, т. е.S=0, а нормально разомкнутый контакт имеет потенциальный контакт +5В через регистрr2и подключен кR– входу (1). Таким образом, по правилу работыRS– триггера в момент времениt1,Q=1. В момент времениt2произошло переключение кнопки и на нижнем ее контакте образовался «дребезг». Однако, в моментt2наS– вход через регистрr1подается уровень логической единицы.

В момент первого касания (t2) подвижного контакта нижнего контакта наR– вход от подвижного контакта подается 0. И по правилам работыRS– триггера (S=1,R=0) триггер опрокинется, т.е.Q=0. Дальнейшее срабатывание кнопки, вызванное дребезгом, не изменит состояние триггера, т.е. на выходеQдребезг не наблюдается.