- •Министерство образования и науки

- •Содержание

- •Информационный процесс, Сигналы

- •Логические состояния

- •Системы счисления

- •Логические элементы и таблица истинности

- •Логическое сложение, дизъюнкция, элемент или

- •Логическое умножение, конъюнкция, элемент и

- •Логический элемент не, отрицание, инверсия

- •Минимизация логических выражений с помощью карт карно

- •Карта карно для двух переменных

- •Карта карно с тремя переменными

- •Карта карно для четырех переменных

- •Комбинационные функциональные схемы

- •Счетверенная двухвходовая схема выборки

- •Мультиплексоры

- •Сумматоры

- •Компараторы

- •Обратные преобразования, записанные в дополнительном коде

- •Арифметика в дополнительном коде

- •Последовательная логика

- •Регистры

- •Параллельно – параллельный четырехразрядный регистр на rs – триггерах

- •Счетный триггер

- •Счетчики

- •Счетчик на сложение

- •Счетчик на вычитание

- •Реверсивный счетчик

- •Счетчик заданной длины

- •Линейные дешифраторы

- •Линейный дешифратор на 10

- •Основы микропроцессорной техники Архитектура эвм

- •Работа эвм

- •Группировки бит

- •Буквенно-цифровой код

- •Тристабильные элементы

- •Структура оперативной памяти

- •Основы микропроцессорной техники

- •Архитектура простой эвм

- •Структура простейшей памяти

- •Состав команд

- •Структура типового микропроцессора

- •Функционирование Эвм

- •Микропроцессор. Поставляемая разработчиком документация

- •Использование регистра, адреса / данных

- •Этапы обработки требования прерывания в микропроцессоре

- •Указатель стека

- •Программирование микропроцессора Состав команд арифметических действий

- •Состав команд логических операций

- •Команда или

- •Команда или – исключающее

- •Команда циклического сдвига с переносом

- •Состав команд операций передачи данных

- •Состав команд операций ветвления

- •Состав команд операций вызова подпрограмм и возврата в основную программу

- •Программирование микропроцессара запись программы

- •Ветвление программ

- •Использование подпрограмм

- •Интерфейс микропроцессора

- •Основные элементы интерфейса портов ввода/вывода

- •Список литературы

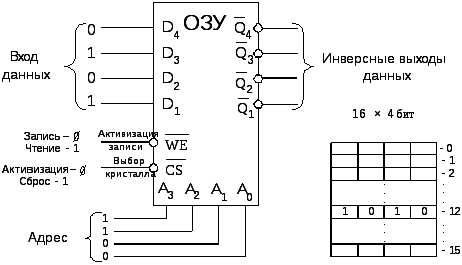

Структура оперативной памяти

ОЗУ с объемом памяти 64 бит выполняет

операцию записи /чтение поступающих

данных в ячейку памяти с заданным

адресом. На входы данных (D1–D4) поступает для

записи (например) слово 0101, а положение

слова в ячейке определяется адресом

1100, поступающим на адресные входа А0– А3, затем две команды управления![]() -

выбор кристалла и

-

выбор кристалла и![]() - запись/чтение переводит ОЗУ в состояние

записи (чтения) данных извне.

- запись/чтение переводит ОЗУ в состояние

записи (чтения) данных извне.

Порядок работы ОЗУ следующий:

На ШД и ША выставляются соответственно данные (0101) и адрес ячейки ОЗУ (1100). При этом входа

и

и находятся

вL– состоянии.

находятся

вL– состоянии.С дешифратора адреса устройства (микросхема) низким уровнем поступает команда

(выбор кристалла).

(выбор кристалла).На шине управления в проводе чтение/запись (

)

устанавливается 0 и информация с входовD1–D4(0101) запишется в ячейку памяти с адресом

1100 (12).

)

устанавливается 0 и информация с входовD1–D4(0101) запишется в ячейку памяти с адресом

1100 (12).По окончании команды чтение/запись управляющие входа

и

и переводится вL– состояние.

В режиме запись выхода

переводится вL– состояние.

В режиме запись выхода так же находятся вL–

состоянии.

так же находятся вL–

состоянии.

Основы микропроцессорной техники

Когда программист изучает новый тип микропроцессора (МП), он должен выяснить следующие вопросы:

Какова архитектура этого МП.

Система команд.

Простейшие системы, использующий данный МП (порты ввода/вывода, таймер и т.п.).

Системы управления.

Назначение выводов МП.

Понятие архитектура относится к организации регистров МП, числа бит шины адреса и шины данных и т.п.

Система команд – это список операций, который МП может выполнять. Этот список включает в себя: передачу данных, арифметические и логические операции, команды сравнения данных и ветвления и операции ввода/вывода. Кроме того, программист должен разобраться с различными способами адресации.

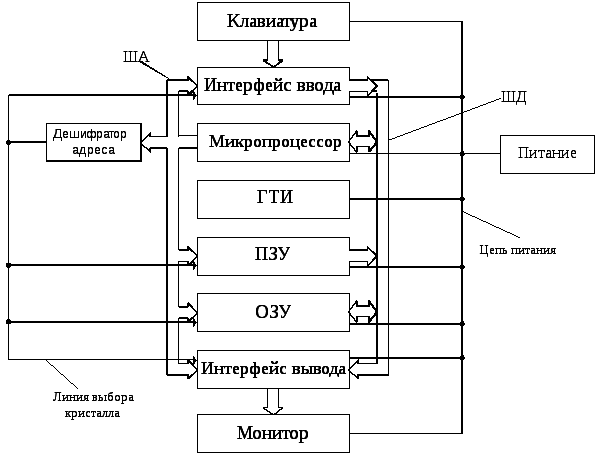

Архитектура простой эвм

МП является центром всех операций, ему необходимо питание и тактовые импульсы. ГТИ может быть отдельным устройством или входить в состав (быть интегрированным) МП.

Типовой МП содержит 16 (32, 64…) адресных линий, которые образуют однонаправленную ША. А так же, обычно, 8 (16, 32…) линий, которые составляют двунаправленную ШД. В представленной архитектуре имеет места 2 типа памяти: ОЗУ и ПЗУ. ПЗУ представляет собой память, которая содержит программу – монитор системы, а так же пользовательские программы. ПЗУ имеет адресные входы, а так же входы активизации только чтения и выбора кристалла. Тристабильные выходы ПЗУ подключены к ШД. ОЗУ тоже, что и ПЗУ, только предусмотрено использование полной команды чтение/запись.

Для того, чтобы активизировать (включить в работу) требуемое устройство, дешифратор адреса считывает данные с ША. Комбинационной логикой линейной комбинации ША активизируется линия выбора соответствующего кристалла, включая, таким образом, выбранное устройство.

ГТИ предназначено для формирования базовой задающей тактовой последовательности импульсов, обеспечивающей временную синхронизацию работы всей системы.

Структура простейшей памяти

Запись в память или считывание из нее происходит при наличии доступа в память. Обычно память выполняется с последовательным или произвольным доступом. Последовательный доступ означает, что к требуемым данным нужно последовательно пройти всю память, расположенную до размещения искомых данных.

В случае, произвольного доступа данные могут быть записаны (считаны) в любую ячейку памяти за определенное фиксированное время называемое временем доступа в памяти.

ОЗУ и ПЗУ ЭВМ являются устройствами с произвольным доступам к памяти, т.к. они обеспечивают существенно большее быстродействие, по – сравнению с последовательным доступом.

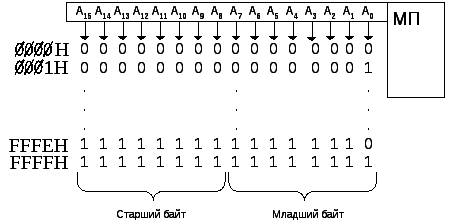

Изучаемый тип МП будет иметь 16 линий адреса, которые могут обеспечить 65536 различных комбинаций 0 и 1, т.к. запись не экономична, то двоичный адрес принято представлять в 16-тиричной системе.

Так как размер ячейки памяти 8 бит (1 байт), а адрес – 2 байта, то для хранения адреса в памяти необходимо выделять 2 ячейки, в одну из которых помещают старший байт адреса, а в другую младший байт адреса.