Агаханян Електронные устройства в медицинских приборах 2010

.pdf

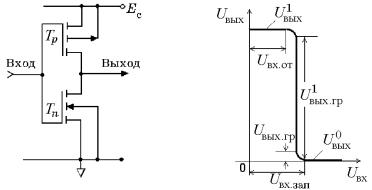

Рис. 2.11. Схема электронного ключа на комплементарных парах МДП-транзисторов (а) и его переключательная характеристика (б)

Переключательная характеристика КМДП-ключа показана на рис. 2.11, б. При низких входных напряжениях Тп закрыт, а Тр открыт и работает в крутой области ВАХ. Однако ток стока Iср открытого транзистора также равен нулю. Он определяется током утечки закрытого транзистора Тп. При этом на выходе ключа уста-

навливается потенциал, близкий к напряжению источника питания,

т.е. Uвых1 ~− Ес .

По мере увеличения входного напряжения разность потенциалов между затвором и истоком транзистора Тп возрастает, а Тр, наоборот, уменьшается (по абсолютному значению). При входном напряжении Uвх.от , равном пороговому напряжению Тп, т.е.

Uвх.от = Uпорп , транзистор Тп начинает проводить ток Iсп. Если на-

пряжение источника питания выбрано из условия: |

|

Ес > Uпорп – Uпорр , |

(2.2) |

то ток Iсп протекает через открытый транзистор Тр, поэтому начинается спад выходного потенциала. Этот спад происходит медленно, до тех пор, пока транзистор Тр работает в крутой области ВАХ. Когда перепад выходного потенциала

Uвых = Ес −Uвых1 .гр

оказывается равным напряжению стокового перекрытия Тр (т.е. Uвых =Uс.перр ), то транзистор Тр тоже переходит в пологую об-

51

ласть ВАХ. Тогда при дальнейшем увеличении Uвх выходной потенциал резко снижается до уровня Uвых0 .гр , при котором оказыва-

ется в крутой области ВАХ транзистор Тп. Это препятствует стремительному спаду выходного потенциала при последующем увеличении входного напряжения. Когда Uвх становится равным

Uвх.зап = Ес −Uпорр ,

транзистор Тр запирается, и выходной потенциал фиксируется на нулевом уровне: Uвых0 = 0.

Особенностью КМДП-ключа является то, что в установившемся режиме один из транзисторов оказывается закрытым, поэтому ключ практически не потребляет тока. При этом потребляемая ключом мощность оказывается минимальной: она практически определяется токами утечки, отбираемыми от источника питания закрытыми транзисторами. Суммарная мощность, потребляемая КМДП-ключом, в основном определяется энергией, которая расходуется на перезарядку паразитных емкостей.

Важным преимуществом этого ключа является также более высокое быстродействие, чем у ключевых элементов на транзисторах с одноименной проводимостью. Это объясняется тем, что разряд и заряд паразитных емкостей, шунтирующих выход, производятся мощными импульсами тока транзисторов соответственно Тп и Тр.

2.4. Основные параметры и классификация логических интегральных микросхем

Вустройствах цифровой автоматики, компьютерах и в целом ряде импульсных устройств широко применяются логические интегральные микросхемы (ИМС), позволяющие автоматизировать выполнение определенных правил, последовательность и порядок которых определяются функциями устройства и реализуемой программой.

Внастоящее время наибольшее распространение получили логические элементы, работающие с двоичным кодированием информации. В электронных устройствах чаще используются два способа кодирования информации: в виде отличающихся потен-

52

циалов (Uвых1 и Uвых0 ) и с помощью импульсных сигналов, наличие и отсутствие которых соответствуют логическим 1 и 0.

Всоответствии с указанными способами кодирования информации логические элементы делятся на потенциальные и импульсные. Применяются также смешанные способы кодирования, когда в процессе обработки информации производится преобразование потенциальных уровней в импульсные сигналы и наоборот. Такие элементы называются импульсно-потенциальными.

Всовременных ИМС, как правило, используется позитивная (положительная) логика, когда логической 1 соответствует высоко-

потенциальный уровень Uвых1 . Если логической 1 соответствует

низкий потенциальный уровень, то говорят о негативной (отрицательной) логике. Разность высокого и низкого потенциальных уровней

Uлог =Uвых1 −Uвых0 ,

называемая размахом логического сигнала, определяется требованиями к ИМС и условиями работы.

Функциональная схема логического элемента состоит из трех частей. Первая из них – логическая часть – предназначена для выполнения заданной логической операции. Вторая – усилительная – производит усиление маломощных сигналов и совместно с третьей частью (формирующей, или выходной) обеспечивает формирование потенциальных уровней или импульсных сигналов с электрическими характеристиками, соответствующими кодируемой информации на выходе элемента. Указанные функции выполняются пассивными и активными элементами, некоторые из которых осуществляют одновременно несколько функций.

По способу передачи информации логические элементы разбиваются на три группы: асинхронные, тактируемые (синхронизированные) и полисинхронные. В асинхронных логических элементах время передачи информации в самой схеме определяется собственным временем задержки. В тактируемых ИМС информация квантуется в определенные моменты времени, устанавливаемые тактовой частотой работы устройства. В полисинхронных элементах переда-

53

ча и преобразование информации зависит от последовательности синхронизирующих сигналов.

Параметры, характеризующие логические элементы, делятся на следующие группы:

•функциональные, определяющие логические возможности при применении ИМС в аппаратуре;

•измеряемые, т.е. входные и выходные токи и напряжения, пороговые напряжения логических 1 (Uпор1 ) и 0 (Uпор0 ), при кото-

рых происходит переход ИМС из одного сотояния в другое;

•режимные, к которым относятся токи и напряжения, задаваемые на выводах ИМС;

•технико-экономические, позволяющие сравнивать ИМС по технологическому уровню изготовления.

Быстродействие цифровых ИМС характеризуется динамическими параметрами, к числу которых относятся:

•t1,0 – время перехода ИМС из состояния логической 1 в состояние логического 0, измеренное на уровнях 0,9 и 0,1 как интервал времени, в течение которого выходное напряжение переходит

от Uвых1 в Uвых0 ;

• t0,1 – время перехода ИМС из состояния логического 0 к логической 1, измеряемое на уровнях 0,1 и 0,9 как интервал времени

при переходе из Uвых0 в Uвых1 ;

• t1,0зд – время задержки включения, измеряемое на заданных

уровнях как интервал времени между входным и выходным импульсами при переходе ИМС из состояния Uвых1 в Uвых0 ;

• tзд0,1 – время задержки выключения, измеряемое так же, как

t1,0зд , только при переходе ИМС из состояния Uвых0 в Uвых1 . Логические ИМС обычно реализуются в виде комплекта, обра-

зующего функционально полную систему, на основе которой можно построить любую логическую схему цифрового автомата, компьютера и т.д. Функционально полную систему образуют логические элементы Пирса и Шеффера.

54

Элемент Пирса реализует функцию дизъюнкции в виде преобразования ИЛИ-НЕ, суть которого заключается в следующем. Логический элемент из состояния 1 переходит в состояние 0 тогда, когда хотя бы на один из входов поступает сигнал, соответствующий высокому уровню. При этом входной сигнал усиливается ИМС и появляется на выходе в инвертированном виде, что и обес-

печивает переход из Uвых1 в Uвых0 .

Элемент Шеффера И-НЕ реализует функцию отрицания конъюнкции: он переходит из состояния Uвых1 в состояние Uвых0 только

тогда, когда на всех входах логической схемы устанавливаются сигналы высокого уровня по амплитуде, превышающей пороговый уровень ИМС.

Из обширного класса логических элементов на биполярных транзисторах наиболее часто применяются транзисторнотранзисторные логические микросхемы и логические микросхемы на переключателях тока. Ниже приводится описание этих элементов, а также рассматриваются логические элементы на МДПтранзисторах с индуцированным каналом.

2.5.Транзисторно-транзисторные логические микросхемы

Элементы транзисторно-транзисторной логики (ТТЛ) появились в результате усовершенствования технологии изготовления микросхем диодно-транзисторной логики (ДТЛ).

Рис. 2.12. Микросхема ТТЛ с простым инвертором

55

На рис. 2.12 показана схема ТТЛ-элемента с диодной сборкой в виде многоэмиттерного транзистора Т1 с разомкнутым коллектором. Эмиттеры транзистора Т1 предназначены для выполнения логической операции И. Когда хотя бы один из этих эмиттеров смещен в прямом направлении, то ток Iб1, поступающий от источника напряжения Е1, отбирается прямо смещенным эмиттером, поэтому инвертор Т2 остается в закрытом состоянии. Только при одновременном установлении на всех входах ТТЛ-элемента высокого по-

тенциала Uвх1 , запирающего эмиттерные переходы транзистора Т1,

ток Iб1 через коллекторный переход Т1 поступает в базу транзистора Т2, выполняющего функцию инвертирующего усилителя. При этом инвертор Т2 отпирается и насыщается, поэтому на выходе

ТТЛ-элемента устанавливается низкий потенциал: Uвых0 =Uкэн (где

Uкэн – выходной потенциал насыщенного транзистора Т2). Таким образом, многоэмиттерный транзистор Т1, реализующий логическую операцию И, совместно с инвертором Т2 обеспечивает выполнение логической функции отрицания конъюнкции (И–НЕ).

Рис. 2.13. Переключательная характеристика элемента ТТЛ с простым инвертором

Особенности ТТЛ-микросхемы определяются ее переключательной характеристикой, представленной на рис. 2.13. Она снята при реальных условиях работы, когда рассматриваемый элемент управляется предшествующими микросхемами ТТЛ, поэтому

56

Uвх0 =Uвых0 , а Uвх1 =Uвых1 . При этом к ее выходу подключаются пт эмиттеров последующих ИМС, представляющих собой нагрузку рассматриваемого элемента. В закрытом состоянии инвертора Т2 на выходе элемента устанавливается высокий потенциал Uвых1 , со-

ответствующий логической 1. Как отмечалось, это происходит тогда, когда хотя бы на один из входов поступает сигнал Uвх0 =Uвых0 ,

и элемент оказывается в рабочей точке А (см. рис. 2.13). Инвертор отпирается, когда на всех входах устанавливается напряжение

U вх.от =U э.об −U от.т ,

смещающее эмиттеры в обратном направлении (Uэ.об) и повышающее потенциал базы Т2 до уровня его отпирания Uот.т. Начинается стремительный спад выходного потенциала до тех пор, пока эмиттеры нагрузочных транзисторов остаются закрытыми. При достижении входными сигналами уровня, соответствующего точке 3 (см. рис. 2.13), нагрузочные эмиттеры отпираются и шунтируют выход транзистора Т2, поэтому на переключательной характеристике образуется пологий участок. В точке 4 нагрузочные инверторы выходят из насыщения, их шунтирующее действие ослабляется и начинается более стремительный спад выходного потенциала.

При достижении входными напряжениями уровня Uвх.гр рас-

сматриваемый инвертор Т2 насыщается, и последующее увеличение входных напряжений не приводит к заметному уменьшению

выходного потенциала. При Uвх1 =Uвых1 на выходе микросхемы

ТТЛ устанавливается низкий потенциал Uвых0 =Uкэн , соответст-

вующий логическому 0 (Uкэн – разность потенциалов между коллектором и эмиттером инвертора Т2 в насыщении).

Важным параметром логических элементов является их помехоустойчивость. Микросхема ТТЛ с простым инвертором при воздействии помехи положительной полярности амплитудой, превос-

ходящей Uпом0 =Uвх.от +Uвых0 , может переходить из состояния 1 в состояние 0. Обратный переход возможен под действием помехи

отрицательной полярности амплитудой Uпом1 =Uвых1 −Uвх.гр .

57

Помехоустойчивость и нагрузочную способность ТТЛ-элемента можно повысить путем включения сложного инвертора. Схема такого элемента показана на рис. 2.14. При смещении в обратном направлении всех элементов транзистора Т1 ток его коллектора поступает в базу транзистора Т2 и отпирает его. Тогда отпирается и инвертирующий транзистор Т3, и на выходе микросхемы устанав-

ливается низкий уровень: Uвых0 =Uкэн . Если хотя бы один из эмит-

теров транзистора Т1 смещен в прямом направлении, то фазорасщепитель на Т2 запирается, поэтому перестает проводить и Т3, но при этом заметно увеличивается ток базы транзистора Т4, образующего с Т5 составной транзистор. Тогда на выходе повторителя напряжения на транзисторах Т4 и Т5 устанавливается высокий по-

тенциал Uвых1 . Использование повторителя напряжения существенно повышает нагрузочную способность микросхемы.

Рис. 2.14. Микросхема ТТЛ со сложным инвертором

Быстродействие ТТЛ-элементов определяется временем перезаряда паразитных емкостей и временем рассасывания носителей заряда в базе инвертора (Т1 и Т3 на рис. 2.12 и 2.14 соответственно). Для сокращения времени задержки сигнала применяют микросхемы на транзисторах Шоттки, в которых практически не происходит накопления носителей заряда в базах у коллекторного перехода. По

58

быстродействию ТТЛ-элементы уступают только ИМС с эмиттерными связями, речь о которых пойдет далее.

2.6.Логические микросхемы на переключателях тока

собъединенными эмиттерами

Наиболее быстродействующими логическими ИМС в настоящее время являются элементы на переключателях тока (см. с. 46). Эти элементы работают в режиме переключения тока по эмиттерной цепи, и в них высокое быстродействие обеспечивается, во-первых, за счет предотвращения насыщения транзисторов и, во-вторых, благодаря переключению по эмиттерной цепи, способствующему сокращению продолжительности переходных процессов в базе транзисторов. Немаловажную роль играют ограничение пределов изменения перепадов выходного напряжения и использование эмиттерных повторителей для ввода и съема информации.

Основой этих схем является переключатель тока с объединен-

ным эмиттером (см. рис. 2.6), функциональные возможности которого можно расширить по входной цепи включением нескольких транзисторов вместо одного Т1, как это показано на рис. 2.15.

Рис. 2.15. Микросхема эмиттерно-связанной логики

В этой схеме транзистор Т выполняет функции опорного элемента, как транзистор Т2 в схеме на рис. 2.6. Число входных тран-

59

зисторов увеличено до трех: Т1, Т2 и Т3. Управление переключателем тока производится подачей сигналов на базы входных

транзисторов Т1–Т3. При подаче высокого потенциала Uвх1 на базу

хотя бы одного из входных транзисторов ток I0 переключается в эмиттерную цепь этого транзистора, и на инвертирующем выходе переключателя тока устанавливается низкий потенциал:

Uвых.ин = Ек − I0Rк1 .

При этом опорный транзистор Т запирается, и на неинвертирующем выходе устанавливается высокий потенциал

Uвых.ни ~− Ек .

Чтобы переключить элемент, необходимо одновременно на базы всех входных транзисторов подать низкий потенциал Uвх0 . При

этом транзисторы Т1–Т3 запираются, ток I0 переключается в эмиттер опорного транзистора Т, и происходит изменение выходных потенциалов:

Uвых.ин ~− Ек , Uвых.ни = Ек − I0Rк2 .

Следует иметь в виду, что при непосредственном подключении к любому из выходов переключателя тока ключевых элементов последние будут работать в режиме насыщения. Действительно, при установлении на выходе переключателя тока высокого потенциала, равного почти Ек, потенциал базы транзистора, подключенный к этому выходу, тоже станет равным Ек, и поскольку потенциал коллектора этого транзистора

Uк = Ек − I0Rк1 ,

то транзистор будет работать в области насыщения, что приведет к заметному снижению быстродействия устройства. Если требуется обеспечить нормальную работу в цепи последовательно включенных переключателей тока, то необходимо произвести сдвиг потенциальных уровней с тем, чтобы исключить насыщение входных транзисторов, подключаемых к выходу предыдущего переключателя тока.

Как известно, можно реализовать сдвиг потенциальных уровней за счет перепадов напряжений на электронно-дырочных переходах

60