ВС для ГОС (ПИ) / Орлов, Цилькер - Организация ЭВМ (2004)

.pdf

5 4 8 Глава 12. Топологии вычислительных систем

Рассматриваемая топология относится к типу неблокирующих сетей с реконфигурацией.

Топология Клоша

В 1953 году Клош показал, что многоступенчатая сеть на основе элементов типа кроссбар, содержащая не менее трех ступеней, может обладать характеристиками неблокирующей сети [62,76].

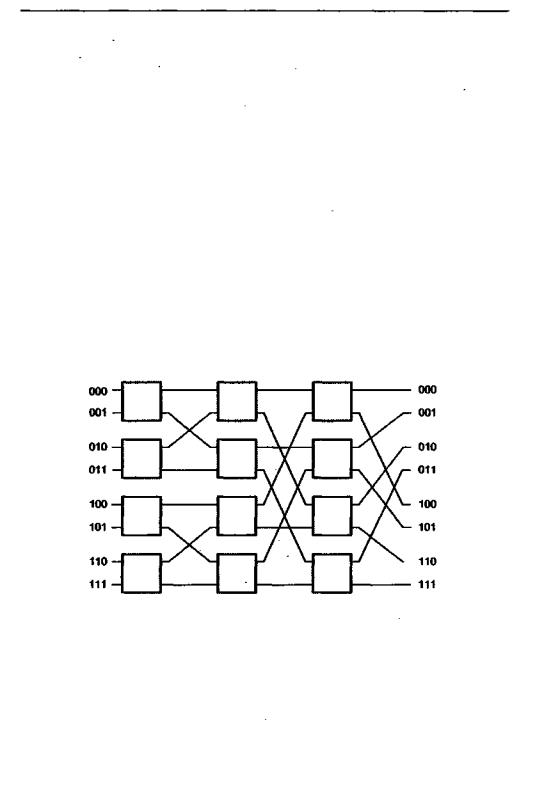

Сеть Клоша с тремя ступенями, показанная на рис. 12.25, содержитr1,кроссбаров во входной ступени, т кроссбаров в промежуточной ступени и r2 кроссбаров в выходной ступени. У каждого коммутатора входной ступени есть n1 входов и т выходов — поодному выходу на каждый кроссбар промежуточной ступени. Коммутаторы промежуточной ступени имеют r1, входов по числу кроссбаров входной ступени и r2 выходов, что соответствует количеству переключателей в выходной ступени сети. Выходная ступень сети строится из кроссбаров с т входами и n2 выходами. Отсюда числа n2 ,n2, r1 ,r2 и т полностью определяют сеть. Число входов сети N = r1n1 а выходов — М = r2n2.

Рис. 12.25. Трехступенчатая сеть с топологией Клоша

Связи внутри составного коммутатора организованы по следующим правилам:

-k-йвыход i-ro входного коммутатора соединен с i-м входом k-го промежуточного коммутатора;

-k-й вход j-го выходного коммутатора соединен c j-м выходом k-го промежуточного коммутатора.

5 5 0 Глава 12. Топологии вычислительныхсистем

ный алгоритм самомаршрутизации, в котором последовательные ступени коммутаторов управляются последовательными битами адреса получателя. Каждая ступень сети на принципе базовой линии делит возможный диапазон маршрутов пополам. Старший бит адреса назначения управляет первой ступенью. При нулевом значении этого бита сообщения с любого из входов поступят на вторую ступень сети с верхних выходов БКЭ первой ступени, то есть они смогут прийти только на верхнюю половину выходов (в нашем примере это выходы с номерами 000-011), а при единичном значении бита— на нижнюю половину выходов (100-111). Второй бит адреса назначения управляет коммутаторами второй ступени, которая делит половину выходов, выбранную первой ступенью, также пополам. Процесс повторяется на последующих ступенях до тех пор, пока младший бит адреса назначения на последней ступени не выберет нужный выход сети. Таким образом, сеть на 8 входов требует наличия трех ступеней коммутации, сеть на 16 входов — 4 ступеней и т. д.

Рис. 12.27.Топология базовойлинии

Как видно из рисунка, сеть с топологией базовой линии совпадает с первыми т (п - 2m) уровнями сети Бенеша на п входов и п выходов. Если к последнему уровню этой сети добавить сеть с инверсной перестановкой битов, то получим так называемую R-сеть. Сеть с инверсной перестановкой битов имеет фиксированные связи входного терминала (amam-1... а1) с выходным терминалом (a1,а2... ат) и фактически представляет собой косвенную двоичную n-кубическую сеть.

Контрольные вопросы

1.Прокомментируйте классификацию сетей по топологии, функциональности узлов, изменяемости взаимосвязей,синхронизации, коммутации иуправлению.

2.Дайте развернутую характеристику метрик, описывающих соединения сети.

3.Сформулируйте достоинства и недостатки наиболее известных функций маршрутизации данных.

4.Обоснуйте достоинства и недостатки линейной топологии сети.

Контрольные вопросы |

5 5 1 |

5.Дайте характеристику плюсов и минусов кольцевой топологии сети. Какие варианты этой топологии практически используются?

6.Проведите сравнительный анализ звездообразной и древовидной топологий сети.

7.Выполните-сравнительный анализ известных вариантов решетчатой топологии сети.

8.Поясните смысл топологии k-ичного n-куба сети. Как строится такой куб?

9.Дайте сравнительную характеристику блокирующих и неблокирующих многоуровневых сетей.

10.Проведите сравнительный анализ одношинной и многошинной топологий динамических сетей, акцентируя их сильные и слабые стороны.

И.Сравните популярные разновидности «баньян»-сетей: «Омега», «Дельта»-. Можно ли причислить к этому классу сети Бенеша, и если можно, то почему?

12.Дайте развернутое объяснение отличий топологии Клоша от «баньян»-сетей. Можно ли найти у них сходные черты, и если можно, то какие?

13.С какой топологией сходна организация двоичной n-кубической сети с косвенными связями? Ответ обоснуйте, приведя конкретный пример.

14.Охарактеризуйте смысл топологии на принципе базовой линии. Изобразите структуру соответствующей сети на 20 входов.

Векторные и ввкторно-конвейерные вычислительные системы 5 5 3

время принято считать, что класс SIMD составляют векторные (векторно-конвей- ерные), матричные, ассоциативные, систолические и VLIW-вычислительные системы. Именно эти ВС и будут предметом рассмотрения в настоящем разделе.

Векторные и векторно-конвейерные вычислительные системы

Хотя производительность ВС общего назначения неуклонно возрастает, по-пре- жнему остаются задачи, требующие существенно большей вычислительной мощности. К таким, прежде всего, следует отнести задачи моделирования реальных процессов и объектов, для которых характерна обработка больших регулярных массивов чисел в форме с плавающей запятой. Такие массивы представляются матрицами и векторами, а алгоритмы их обработки описываются в терминах матричных операций. Как известно, основные матричные операции сводятся к однотипным действиям над парами элементов исходных матриц, которые, чаще всего, можнопроизводитьпараллельно, Вуниверсальных ВС,ориентированныхнаскалярные операции, обработкаматрицвыполняется поэлементно и последовательно. При большой размерности массивов последовательная обработка элементов матриц занимаетслишком много времени, что и приводит к неэффективности универсальных ВС для рассматриваемого класса задач. Для обработки массивов требуются вычислительныесредства,позволяющиеспомощьюединойкомандыпроизводитьдействие сразунадвсемиэлементамимассивов—средствавекторнойобработки.

Понятие вектора и размещение данных в памяти

В средствах векторной обработки под вектором понимается одномерный массив однотипныхданных (обычно в форме с плавающей запятой), регулярным образом размещенных в памяти ВС. Если обработке подвергаются многомерные массивы, их также рассматривают как векторы. Такой подход допустим, если учесть, каким образом многомерные массивы хранятся в памяти ВМ Пусть имеется массив данныхЛ, представляющий собой прямоугольную матрицуразмерности 4x5 (рис. 13.2).

Рис. 13.2. Прямоугольнаяматрицаданных

При размещении матрицы в памяти все ее элементы заносятся в ячейки с последовательными адресами, причем данные могутбыть записаны строка за строкой или столбец за столбцом (рис. 13.3). С учетом такого размещения многомерных массивов в памяти вполне допустимо рассматривать их как векторы и ориентировать соответствующие вычислительные средства на обработку одномерных массивов данных (векторов).

5 5 4 Глава 13. Вычислительные системы класса SIMD

Рис. 13.3. Способы размещения в памяти матрицы 4x5

Действия над многомерными массивами имеют свою специфику. Например, в двумерном массиве обработка может вестись как по строкам, так и по столбцам. Это выражается в том, с каким шагом должен меняться адрес очередного выбираемого из памяти элемента. Так, если рассмотренная в примере матрица расположена в памяти построчно, адреса последовательных элементов строки различаются на единицу, а для элементов столбца шаг равен пяти. При размещении матрицы по столбцам единице будет равен шаг по столбцу, а шаг по строке — четырем. В векторной концепции для обозначения шага, с которым элементы вектора извлекаются из памяти, применяют термин шаг по индексу (stride).

Еще одной характеристикой вектора является число составляющих его элемен- тов—длинавектора.

Понятие векторного процессора

Векторный процессор — это процессор, в котором операндами некоторых команд могут выступать упорядоченные массивы данных — векторы. Векторный процессор может быть реализован в двух вариантах. В первом он представляет собой дополнительный блок к универсальной вычислительной машине (системе). Во втором — векторный процессор — это основа самостоятельной ВС.

Рассмотрим возможные подходы к архитектуре средств векторной обработки. Наиболее распространенные из них сводятся к трем группам:

*конвейерное АЛУ;

*массив АЛУ;

*массив процессорных элементов.

Последний вариант — один из случаев многопроцессорной системы, известной как матричная ВС. Понятие векторного процессора имеет отношение к двум первым группам, причем, как правило, к первой. Эти две категории иллюстрирует рис. 13.4 [200].

Состояние, в которое пе-

Состояние, в которое пе- то БКЭ, расположенный на

то БКЭ, расположенный на  — перекрестное соединение. На рис. 12.22 показан процесс прохождения сообщения по сети «Омега» 8 х 8 от входного терминала 2 (010

— перекрестное соединение. На рис. 12.22 показан процесс прохождения сообщения по сети «Омега» 8 х 8 от входного терминала 2 (010