- •Московский институт электронной техники Аппаратно-программный комплекс для изучения и исследования микропроцессоров и программируемой логики

- •Введение

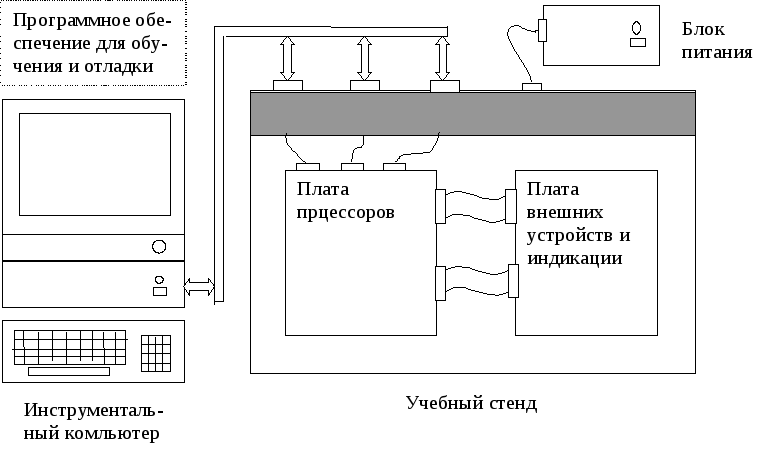

- •Оборудование учебного рабочего места

- •Описание плат учебного стенда

- •Плата процессоров

- •Платы внешних устройств и индикации.

- •Процесс разработки

- •Конструкторские файлы, вспомогательные файлы и проекты.

- •Конструкторские файлы

- •Вспомогательные файлы

- •Меню Help (Помощь)

- •Начало проектирования

- •Назначение ресурсов, устройств и имен.

- •Настройка устройства проекта.

- •Расположение узлов.

- •Анализ времен.

- •Язык описания Альтеры ahdl.

- •Язык vhdl

- •Язык Verilog hdl

- •Примитивы, мегафункции и макрофункции.

- •Примитивы.

- •Мегафункции.

- •Макрофункции старого стиля.

- •Иерархия проекта.

- •Обработка проекта

- •Входные файлы компилятора.

- •Процесс компиляции.

- •Запуск компиляции.

- •Модули компилятора и выходные файлы.

- •Средства управления базами данных Database Builder.

- •Синтезатор Логики - Logic Synthesier

- •Разделитель – Partitioner.

- •Разводчик - Fitter.

- •Функциональный экстрактор snf

- •Экстрактор времен snf

- •Экстрактор связей snf.

- •Обработчик списков соединений edif (Edif Netlist Writer)

- •Обработчик списков соединений Verilog (Verilog Netlist Writer)

- •Обработчик списков соединений vhdl (vhdl Netlist Writer)

- •Ассемблер (Assembler).

- •Утилита Design Doctor.

- •Обнаружение ошибок и нахождение места их возникновения.

- •Анализ проекта.

- •Функциональное моделирование (симуляция).

- •Временная симуляция.

- •Связанная многопроектная симуляция.

- •Особенности симулятора.

- •Программирование устройства.

- •Шаг 2. Создание графического файла схемы (Graphic Design File).

- •Шаг 3. Компиляция проекта.

- •Шаг 4. Подготовка файла симуляции проекта.

- •Шаг 5. Симуляция.

- •Шаг 6. Анализ результатов работы Симулятора.

- •Шаг 7. Программирование устройства Altera.

- •Шаг 2. Проверка работоспособности собранной схемы триггера с помощью Редактора Временных Диаграмм.

- •Шаг 3. Сохранение элемента как примитив (символ).

- •Шаг 4. Сборка схемы трехразрядного счетчика.

- •Шаг 5. Проверка работы схемы с помощью Редактора Временных Диаграмм.

- •Интегрированная среда разработки и отладки.

- •Работа в интегрированной среде.

- •Команды меню.

- •Команды меню Файл

- •Команды меню Редактирование

- •Команды меню Показать

- •Команды меню Компиляция

- •Команды меню Отладка

- •Команды меню Окно

- •Команды меню Справка

- •Настройка параметров среды

- •Общие настройки

- •Настройка редактора

- •Настройка коммуникаций.

- •Компиляция

- •Окно ошибок.

- •Запуск программы на выполнение.

- •Сброс процессора.

- •Отладка

- •Ресурсы процессора.

- •Окно регистров

- •Окно памяти.

Московский институт электронной техники Аппаратно-программный комплекс для изучения и исследования микропроцессоров и программируемой логики

1999 г.

Введение 3

Оборудование учебного рабочего места 3

Описание плат учебного стенда 4

.Плата процессоров 4

.Платы внешних устройств и индикации. 7

Описание Системы Автоматизированного Проектирования MAX+PLUSII. 12

Разработка с помощью САПР MAX+PLUSII. 13

.Процесс разработки 14

.Запуск MAX+PLUS II 15

.Менеджер MAX+PLUSII. 16

.Приложения MAX+PLUSII 17

.Конструкторские файлы, вспомогательные файлы и проекты. 19

.Справочная система MAX+PLUSII. 20

.Начало проектирования 21

.Общие особенности проектирования MAX+PLUSII. 22

.Общие функции редакторов 26

.Графический редактор MAX+PLUSII 26

.Редактор примитивов MAX+PLUSII 28

.Текстовый редактор MAX+PLUSII. 29

.Редактор временных диаграмм MAX+PLUS. 30

.Редактор топологии MAX+PLUSII. 31

.Язык описания Альтеры AHDL. 33

.Язык VHDL 34

.Язык Verilog HDL 36

.Примитивы, мегафункции и макрофункции. 37

.Иерархия проекта. 38

.Обработка проекта 40

Последовательность действий по созданию проекта в САПР MAX+PLUSII 60

.Шаг 1. Запуск MAX+PLUSII. 60

.Шаг 2. Создание графического файла схемы (Graphic Design File). 60

.Шаг 3. Компиляция проекта. 64

.Шаг 4. Подготовка файла симуляции проекта. 66

.Шаг 5. Симуляция. 68

.Шаг 6. Анализ результатов работы Симулятора. 69

.Шаг 7. Программирование устройства Altera. 69

Пример разработки D-триггера с помощью САПР MAX+PLUSII. 70

.Шаг 1. Сборка схемы D-триггера в Графическом Редакторе MAX+PLUSII. 70

.Шаг 2. Проверка работоспособности собранной схемы триггера с помощью Редактора Временных Диаграмм. 76

.Шаг 3. Сохранение элемента как примитив (символ). 78

.Шаг 4. Сборка схемы трехразрядного счетчика. 78

.Шаг 5. Проверка работы схемы с помощью Редактора Временных Диаграмм. 78

Интегрированная среда разработки и отладки. 81

.Работа в интегрированной среде. 83

.Команды меню. 84

.Настройка параметров среды 88

.Настройка коммуникаций. 90

.Компиляция 92

.Отладка 94

Введение

Широкое внедрение интеллектуальных многопроцессорных структур во многом определяется уровнем подготовки инженерных кадров к использованию современной элементной базы. Для изучения микропроцессоров и получения практических навыков работы с ними в технических ВУЗах используются специальные учебные и отладочные модули (стенды), ориентированные на изучение конкретных микропроцессоров. В Московском институте электронной техники проведена разработка аппаратуры комплекса аппаратно-программных средств, позволяющего изучать не только конкретные типы микропроцессоров, но и предоставляющего дополнительные возможности по изучению программируемой логики и многопроцессорных структур.

Оборудование учебного рабочего места

Оборудование аппаратно-программного комплекса, предназначенного для проведения лабораторных работ по изучению современных микропроцессоров и программируемой логики, показано на рис. 1. Лабораторное рабочее место состоит из учебного стенда с встроенным блоком питания и подключенного к стенду инструментального компьютера.

Рис. 1. Оборудование учебного рабочего места

Конструкция учебного стенда представляет собой корпус (с жестким основанием), на задней стороне которого установлены разъемы для подключения инструментального компьютера.

На верхней стороне корпуса стенда размещаются две платы:

плата микропроцессоров и программируемой логики;

плата внешних устройств и индикации.