- •Гласман К.Ф., Покопцева М.Н.

- •«Аудиовизуальная техника»

- •Введение

- •2. БАЗОВЫЕ ЛОГИЧЕСКИЕ СХЕМЫ

- •2.1. Логические элементы

- •2.1.1. Основные логические функции

- •2.1.2. Составление логических функций

- •2.1.3. Производные основных логических функций

- •2.1.4. Логические элементы как схемы временной селекции

- •2.1.5. Логические состязания

- •2.2 Триггеры

- •2.2.1 Бистабильная ячейка

- •2.2.2. Асинхронные и синхронные триггеры

- •2.2.3. Статический синхронный RS-триггер

- •2.2.4 Статический синхронный D-триггер

- •2.2.5 Триггеры типа M-S ("ведущий-ведомый")

- •2.2.6. Динамический D-триггер

- •3. КОМБИНАЦИОННЫЕ УСТРОЙСТВА

- •3.1. Преобразователи кодов

- •3.1.1. Шифраторы

- •3.1.2. Дешифраторы

- •3.1.4. Преобразователи двоичного кода в двоично-десятичный

- •3.1.5. Преобразователи двоично-десятичного кода в двоичный

- •3.1.6. Взаимное преобразование кода Грея и двоичного кода

- •3.1.7. Схемы контроля четности и нечетности

- •3.2. Мультиплексоры и демультиплексоры

- •3.2.1. Мультиплексоры

- •3.2.2. Мультиплексор как универсальная комбинационная схема

- •3.2.3. Демультиплексоры

- •3.3. Арифметические устройства

- •3.3.1. Компараторы

- •3.3.2. Одноразрядные сумматоры

- •3.3.3. Сумматоры с последовательным переносом

- •3.3.4. Сумматоры с параллельным переносом

- •3.3.5. Устройства для вычитания чисел

28

x

&

&

y = x

x1 x2

& |

|

& |

y = x1 x 2

x1

x2

&  &

&  &

&

y = x1 + x 2

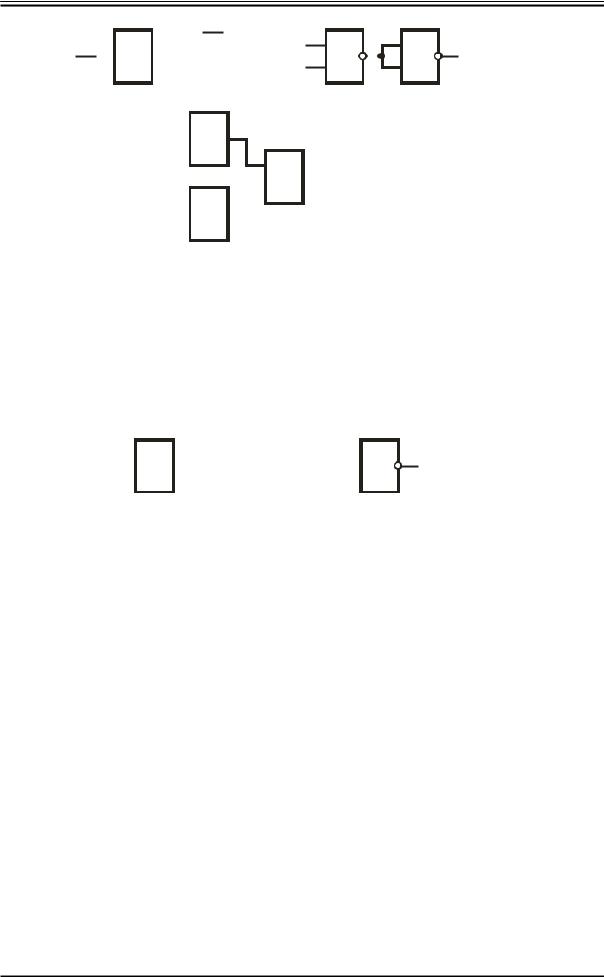

Рис. 2.8. Реализация основных функций на элементах И-НЕ

Если операцию инверсии входных переменных символически отразить кружками на входах элемента, то можно получить условное графическое изображение элемента ИЛИ, эквивалентное основному (рис. 2.9).

x1 |

|

|

|

y = x 1+ x2 |

|

1 |

|||||

x2 |

|

|

|||

|

|

|

|

||

|

|

|

|

||

x1  x2

x2

&

y = x 1+ x2

Рис. 2.9. Эквивалентные формы графического изображения элемента ИЛИ

Схемы, аналогичные показанным на рис. 2.8 и 2.9, могут быть составлены с использованием элементов ИЛИ-НЕ.

2.1.4. Логические элементы как схемы временной селекции

Анализ таблиц истинности логических элементов показывает, что они могут использоваться для временной селекции данных в цифровых устройствах. Если один из входов элемента И рассматривать как вход данных D, а второй - как вход управления G, то на выходной сигнал Q=D

при G=1 и Q=0 при G=0 (рис.2.10).

Это означает, что элемент И может играть роль стробирующей схемы, позволяющей выделять сигнал данных в пределах стробирующего (разрешающего) импульса положительной полярности. Управляющий сигнал G нулевого уровня запрещает прохождение данных на вход элемента. Схема стробирования может быть построена и на элементах ИЛИ, И-НЕ, ИЛИ-НЕ.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1

29 |

БАЗОВЫЕ ЛОГИЧЕСКИЕ СХЕМЫ |

Рис. 2.10. Элемент И как схема стробирования

Если сигнал данных D и управления G подать на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, то, как следует из таблицы истинности, выходной сигнал:

Q = D |

при |

G = 0 |

|

Q = |

|

при |

G =1 |

D |

|||

Это очень важное свойство означает, что на базе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ можно построить управляемый переключатель полярности. Данные передаются на выход элемента в прямой и инверсной (дополнительной) форме в зависимости от управляющего сигнала.

2.1.5. Логические состязания

Если известна логическая формула, связывающая входные и выходные переменные проектируемого устройства, то нетрудно составить схему, отдельные элементы которой выполняют логические операции в соответствии с заданной формулой. Но и тогда, когда структура схемы полностью соответствует заданной логической формуле, выходные переменные могут на отдельных интервалах времени принимать значения, не равные расчетным. Это может быть вызвано тем, что сигналы, представляющие переменные, поступают на входы выполняющего некоторую операцию элемента с различными временными задержками. Такие явления называют логическими состязаниями.

Существо процессов, которые происходят при логических состязаниях, можно выяснить на простом примере. Известно, что произведение логической переменной на ее инверсию тождественно равно

0(правило отрицания), т.е.:

xx = 0

Такое произведение может быть реализовано с помощью схемы, показанной на рис. 2.11а. Временные диаграммы, показывающие процессы в схеме при изменении значения переменной x, представлены на рис. 2.11б. Так как сигнал, представляющий переменную у, появляется на выходе элемента НЕ с задержкой, то x y ≠ 0 в интервале, равном длительности задержки. Временная диаграмма, показывающая переменную z, построена с учетом задержки в элементе И. Так как время задержки и длительность