- •Гласман К.Ф., Покопцева М.Н.

- •«Аудиовизуальная техника»

- •Введение

- •2. БАЗОВЫЕ ЛОГИЧЕСКИЕ СХЕМЫ

- •2.1. Логические элементы

- •2.1.1. Основные логические функции

- •2.1.2. Составление логических функций

- •2.1.3. Производные основных логических функций

- •2.1.4. Логические элементы как схемы временной селекции

- •2.1.5. Логические состязания

- •2.2 Триггеры

- •2.2.1 Бистабильная ячейка

- •2.2.2. Асинхронные и синхронные триггеры

- •2.2.3. Статический синхронный RS-триггер

- •2.2.4 Статический синхронный D-триггер

- •2.2.5 Триггеры типа M-S ("ведущий-ведомый")

- •2.2.6. Динамический D-триггер

- •3. КОМБИНАЦИОННЫЕ УСТРОЙСТВА

- •3.1. Преобразователи кодов

- •3.1.1. Шифраторы

- •3.1.2. Дешифраторы

- •3.1.4. Преобразователи двоичного кода в двоично-десятичный

- •3.1.5. Преобразователи двоично-десятичного кода в двоичный

- •3.1.6. Взаимное преобразование кода Грея и двоичного кода

- •3.1.7. Схемы контроля четности и нечетности

- •3.2. Мультиплексоры и демультиплексоры

- •3.2.1. Мультиплексоры

- •3.2.2. Мультиплексор как универсальная комбинационная схема

- •3.2.3. Демультиплексоры

- •3.3. Арифметические устройства

- •3.3.1. Компараторы

- •3.3.2. Одноразрядные сумматоры

- •3.3.3. Сумматоры с последовательным переносом

- •3.3.4. Сумматоры с параллельным переносом

- •3.3.5. Устройства для вычитания чисел

63 |

КОМБИНАЦИОННЫЕ УСТРОЙСТВА |

|

|

разряда четного и нечетного паритета (табл. 3.5). Для наращивания разрядности слова данных схемы ИП2 можно соединять последовательно. При этом четный и нечетный выходы первой схемы подключаются соответственно к четному и нечетному входам следующей схемы и т.д.

Таблица 3.5

Таблица истинности ИС К155ИП2

Сумма “1” |

E1 |

E0 |

SE |

S0 |

|

на входах |

|||||

|

|

|

|

||

четное |

1 |

0 |

1 |

0 |

|

нечетное |

1 |

0 |

0 |

1 |

|

четное |

0 |

1 |

0 |

1 |

|

нечетное |

0 |

1 |

1 |

0 |

|

х |

1 |

1 |

0 |

0 |

|

х |

0 |

0 |

1 |

1 |

3.2. Мультиплексоры и демультиплексоры

3.2.1. Мультиплексоры

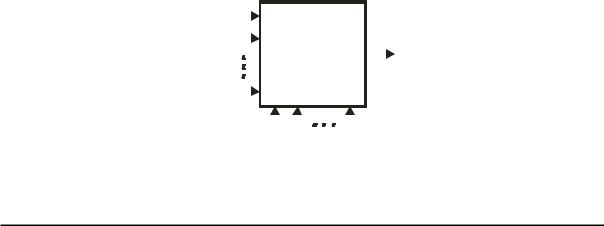

Мультиплексор предназначен для последовательной коммутации нескольких переменных на один выход. Кроме информационных входов

D0 ....Dm−1 |

и выхода Q , мультиплексор имеет адресные входы A0 ....An−1 . |

Двоичный |

вход представленный переменными A0 ....An−1 , определяет |

номер входа, который подключается к выходу (рис. 3.20). При длине

адресного |

слова n можно коммутировать на |

один выход m = 2 n . |

входных |

переменных. Схему мультиплексора |

можно составить из |

дешифратора на m выходов, схем стробирования и элемента ИЛИ с m входами (рис. 3.21). Вход стробирования дешифратора будет входом

стробирования мультиплексора. При G =0 и Q =0 .

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

MS |

|

|

|

Q |

|

|

|

|

|

|

|||

Dm -1 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 A1 |

A |

n-1 |

||||

Рис. 3.20. Обобщенная схема мультиплексора

64

|

а) |

|

|

|

|

|

|

б) |

|

|

|

D0 |

|

|

|

& |

|

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

& |

|

|

|

|

D2 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

Q |

|

D3 |

|

Q |

|||

|

|

|

|

||||||||

D2 |

|

|

|

& |

|

|

A0 |

|

|

||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

A1 |

|

|

||

|

|

|

|

|

|

|

|

||||

D3 |

|

|

|

& |

|

|

|

|

G |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||

A0 |

|

A0 |

DC Q0 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||||

A1 |

|

A1 |

Q1 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||||

G |

|

G |

Q2 |

|

|

|

|

|

|

||

|

Q3 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||||

Рис. 3.21. Мультиплексор на 4 входа: а – схема; б - УГО

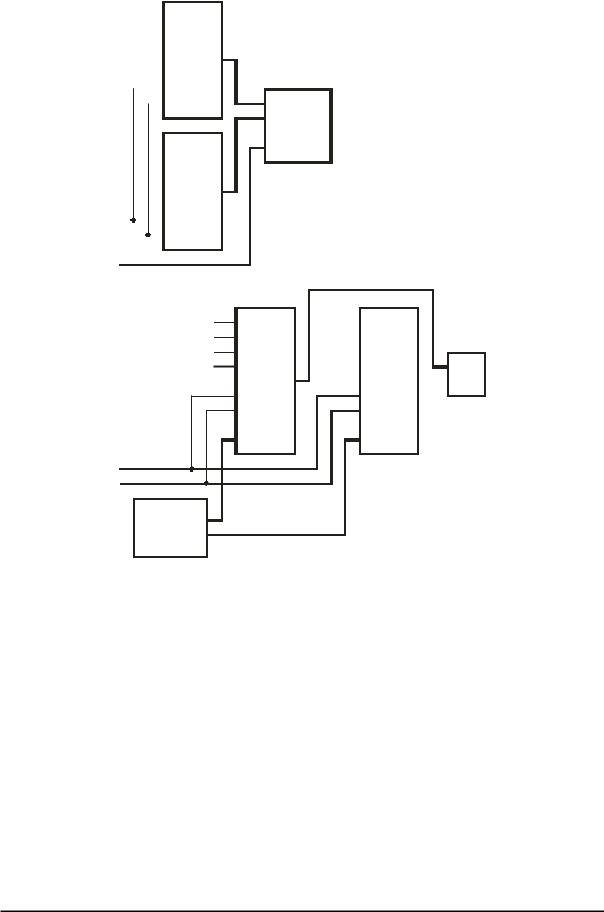

Наращивание числа входов мультиплексора можно выполнять двумя способами. На рис. 3.22а показано построение мультиплексора на 8 входов из мультиплексора на 4 и 2 входа, которые объединены в пирамидальную систему. На объединенные адресные входы мультиплексоров первой ступени поступают младшие разряды адресного кода системы, на вторую ступень подаются старшие разряды адреса. Выходы мультиплексоров первой ступени являются информационными входами второй. Аналогично можно построить многоступенчатую систему на большее число входов.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1

65 |

КОМБИНАЦИОННЫЕ УСТРОЙСТВА |

|

|

а)

D0 |

|

|

|

D0 |

MS |

|

|

|

|||

D1 |

|

|

|

D1 |

|

|

|

|

|

||

D2 |

|

|

|

D2 |

|

|

|

|

|

||

D3 |

|

|

|

D3 |

|

|

|

|

|

||

|

|

|

|

A0 |

|

|

|

|

|

|

|

D4 |

|

|

|

A1 |

MS |

|

|

|

|||

|

|

|

|

||

|

|

|

|

||

|

|

|

D0 |

||

|

|

|

|||

D5 |

|

|

|

D1 |

|

|

|

|

|

||

D6 |

|

|

|

D2 |

|

|

|

|

|

||

D7 |

|

|

|

D3 |

|

|

|

|

|

||

A0 |

|

|

|

A0 |

|

|

|

|

|

||

A1 |

|

|

|

A1 |

|

|

|

|

|

||

A2 |

|

|

|

||

б)

D0

D1

D2

D3

A0

A1

A2 |

|

A0 |

DC |

Q0 |

|

||||

G |

|

G |

|

Q1 |

|

|

|

||

|

|

|

|

|

D0 |

MS |

||

D1 |

|

Q |

|

|

|

|

|

A0 |

|

|

|

|

|

|

|

D0 |

MS |

D4 |

|

D0 |

MS |

||||

|

|||||||||

D1 |

|

D5 |

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

D2 |

|

D6 |

|

D2 |

1 |

|

|

||

|

|

|

|

||||||

D3 |

|

D7 |

|

D3 |

Q |

||||

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

A0 |

|

|

|

A0 |

|

|

|

|

|

A1 |

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G |

|

|

|

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.22. Наращивание числа входов мультиплексора: а – с использованием мультиплексоров; б - с использованием мультиплексоров, дешифратора и элемента ИЛИ

Система, приведенная на рис.3.22б, построена с использованием мультиплексоров с объединенными адресными входами и дешифратора, на вход которого поступает старший разряд адресного кода системы. Благодаря подключению выходов дешифратора ко входам стробирования

мультиплексоров при A2 = 0 на выход Q проходит одна из переменных D0 ....D3 , при A2 =1 - одна из переменных D4....D7 (в зависимости от кода младших разрядов адреса). При таком способе наращивания числа

66

входов необходимо использовать мультиплексоры со входом стробирования.

Примеры ИС:

К555КП1 - мультиплексор на 16 входов со стробированием и инверсным выходом.

К555КП2 - два мультиплексора на 4 входа с объединенными адресными входами и раздельными входами стробирования.

К555КП7 - мультиплексор на 8 входов со стробированием (рис.3.23).

4 |

D0 |

MS |

|

|

|

3 |

|

|

|||

D1 |

|

|

|

|

|

2 |

|

|

|

|

|

D2 |

|

|

|

|

|

1 |

|

|

|

|

|

|

D3 |

|

|

|

|

15 |

|

|

|

|

|

|

D4 |

5 |

|

|

|

14 |

Q |

||||

|

D5 |

|

|

||

13 |

|

|

|||

|

D6 |

|

|

|

|

12 |

|

|

|

|

|

|

D7 |

|

6 |

|

|

|

|

|

|

||

11 |

A0 |

|

|

Q |

|

|

|

||||

|

|

|

|

||

10 |

|

|

|

|

|

|

A1 |

|

|

|

|

9 |

|

|

|

|

|

A2 |

|

|

|

|

|

|

|

|

|

|

|

7 |

G |

|

Рис. 3.23. Мультиплексор К155КП7

3.2.2.Мультиплексор как универсальная комбинационная схема

Мультиплексор с n адресными входами можно использовать для реализации произвольной логической функции n переменных. Для этого надо независимые переменные подавать на адресные входы мультиплексора. При этом каждой комбинации входных переменных будет

соответствовать один из входов Di , подключаемый к выходу мультиплексора. К каждому входуDi надо подвести постоянный уровень (0 или 1), равный значению логической функции для соответствующей комбинации входных переменных. В результате выход мультиплексора Q будет повторять требуемую функцию n переменных.

С помощью одного инвертора мультиплексор можно использовать для реализации произвольной функции (n +1) переменной. На адресные входы мультиплексора подаются n переменных. Эти n переменных (например, x2 ....xn+1 ) и определяют номер входа Di , подключаемого к

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1

|

67 |

КОМБИНАЦИОННЫЕ УСТРОЙСТВА |

||||

|

|

|

|

|

|

|

выходу. Для каждой комбинации |

x2 ....xn+1 |

переменная x1 |

принимает два |

|||

значения - 0 и 1. Значения x1 |

сравниваются со |

значениями заданной |

||||

логической функции y . В результате сравнения - |

подается на вход D , |

|||||

номер которого определяется комбинацией переменных |

x2 ....xn+1 . Это |

|||||

|

x1 или |

|

. При этом выход Q |

|||

может быть одна из четырех величин: 0, 1, |

x1 |

|||||

мультиплексора с n адресными входами равен заданной логической функции (n +1) переменных.

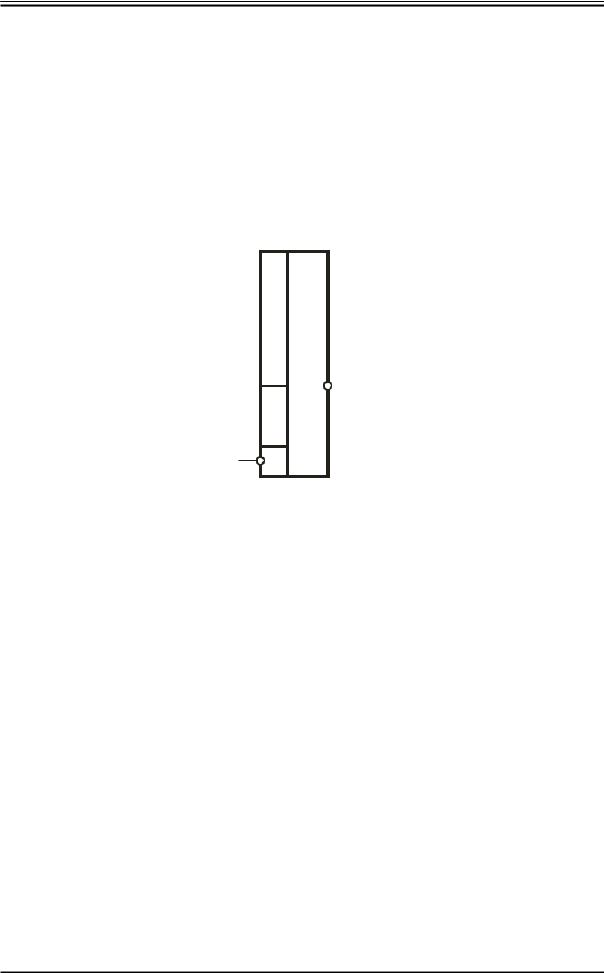

На рис. 3.24 приведена схема реализации элемента "1 и только 1" на мультиплексоре с 4 информационными входами. Выходная переменная этого элемента равна 1 в том случае, если единичный уровень присутствует только на одном входе. Логика работы элемента "1 и только

1" с тремя входами отражена в табл. 3.6. В ней также указаны входы Di мультиплексора, соответствующие каждой комбинации переменных x2 и x3 , которые подключены к адресным входам мультиплексора. В

последнем столбце таблицы приведены величины (постоянные или переменные), которые должны быть на выходе мультиплексора. Для того,

чтобы Q действительно |

было бы |

равно |

заданной |

функции y , эти |

|||||||||||||

величины подаются на соответствующие входы мультиплексора. |

|||||||||||||||||

|

|

|

|

|

|

|

|

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

x1 |

|

|

1 |

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

D2 |

|

|

Q=y |

|

=1 y |

||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

D3 |

|

|

|

|

x2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x2 |

|

|

|

|

|

|

|

A0 |

|

|

|

|

x3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x3 |

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Рис. 3.24. Элемент «1 и только 1» на мультиплексоре

68

Таблица 3.6

Таблица истинности элемента “1 и только 1”

Х3 |

Х2 |

Х1 |

Y |

Вход MS Q |

|||

0 |

0 |

0 |

0 |

D0 |

x1 |

||

0 |

0 |

1 |

1 |

D0 |

|||

|

|

||||||

0 |

1 |

0 |

1 |

D1 |

|

|

|

x1 |

|||||||

0 |

1 |

1 |

0 |

D1 |

|||

|

|

||||||

1 |

0 |

0 |

1 |

D2 |

|

|

|

x1 |

|||||||

1 |

0 |

1 |

0 |

D2 |

|||

|

|

||||||

1 |

1 |

0 |

0 |

D3 |

0 |

|

|

1 |

1 |

1 |

0 |

D3 |

|

||

|

|

||||||

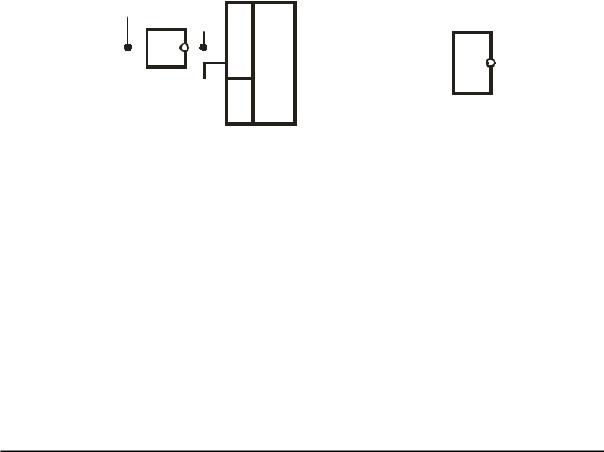

В качестве второго примера на рис. 3.25 приведена схема реализации мажоритарного элемента с тремя входными переменными на мультиплексоре с двумя адресными входами. Функция y , описывающая мажоритарный элемент, равна 1 в том случае, если единичный уровень присутствует более, чем на половине входов (число входов должно быть нечетным). Схема построена на основе данных табл. 3.7. Как видно, наличие инвертора не является обязательным. Мажоритарный элемент может быть реализован на одном мультиплексоре, хотя количество переменных и превышает число адресных входов.

|

|

|

|

|

|

|

D0 |

MS |

|

|

|

|

|

||

x |

|

|

|

|

|

|

D1 |

|

|

|

x |

|

≥M y |

||

|

|

|

|

|

|

|

|

|

|

||||||

1 |

|

|

|

|

|

D2 |

|

Q=y |

|

||||||

|

|

|

|

|

|

|

|||||||||

|

|

“1“ |

|

D3 |

|

x21 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||

x2 |

|

|

|

|

|

A0 |

|

|

|

x3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

x3 |

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Рис. 3.25. Мажоритарный элемент на мультиплексоре

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1