- •Гласман К.Ф., Покопцева М.Н.

- •«Аудиовизуальная техника»

- •Введение

- •2. БАЗОВЫЕ ЛОГИЧЕСКИЕ СХЕМЫ

- •2.1. Логические элементы

- •2.1.1. Основные логические функции

- •2.1.2. Составление логических функций

- •2.1.3. Производные основных логических функций

- •2.1.4. Логические элементы как схемы временной селекции

- •2.1.5. Логические состязания

- •2.2 Триггеры

- •2.2.1 Бистабильная ячейка

- •2.2.2. Асинхронные и синхронные триггеры

- •2.2.3. Статический синхронный RS-триггер

- •2.2.4 Статический синхронный D-триггер

- •2.2.5 Триггеры типа M-S ("ведущий-ведомый")

- •2.2.6. Динамический D-триггер

- •3. КОМБИНАЦИОННЫЕ УСТРОЙСТВА

- •3.1. Преобразователи кодов

- •3.1.1. Шифраторы

- •3.1.2. Дешифраторы

- •3.1.4. Преобразователи двоичного кода в двоично-десятичный

- •3.1.5. Преобразователи двоично-десятичного кода в двоичный

- •3.1.6. Взаимное преобразование кода Грея и двоичного кода

- •3.1.7. Схемы контроля четности и нечетности

- •3.2. Мультиплексоры и демультиплексоры

- •3.2.1. Мультиплексоры

- •3.2.2. Мультиплексор как универсальная комбинационная схема

- •3.2.3. Демультиплексоры

- •3.3. Арифметические устройства

- •3.3.1. Компараторы

- •3.3.2. Одноразрядные сумматоры

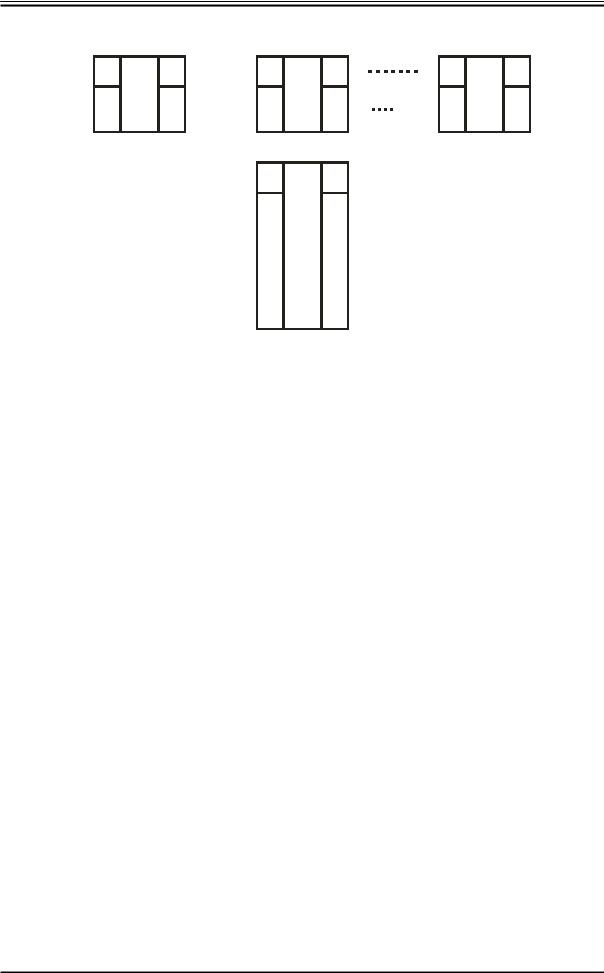

- •3.3.3. Сумматоры с последовательным переносом

- •3.3.4. Сумматоры с параллельным переносом

- •3.3.5. Устройства для вычитания чисел

75 КОМБИНАЦИОННЫЕ УСТРОЙСТВА

а) |

|

|

|

|

|

|

|

|

|

б) |

|

||

c0 |

|

|

|

|

A0 |

HS S0 |

|

|

|

s |

|

C0 |

SM C1 |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

B0 |

C1 |

|

|

0 |

|

A0 |

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

S0 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

A0 |

HS S0 |

|

1 |

|

c1 |

|

B0 |

|||||

|

|

|

|

|

|||||||||

|

|

|

|

|

|||||||||

b0 |

|

B0 |

C1 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||||

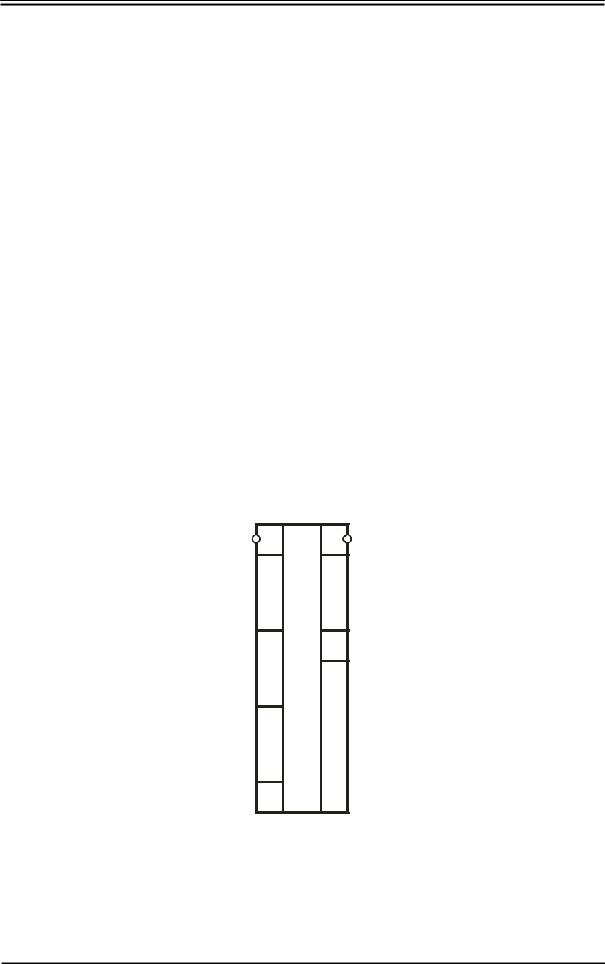

Рис. 3.33. Полный одноразрядный сумматор: а – схема; б - УГО

Таблица 3.11 Таблица истинности полного одноразрядного сумматора

a0 |

b0 |

c0 |

S0 |

c1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Пример ИС:

К155ИМ1 - одноразрядный полный сумматор.

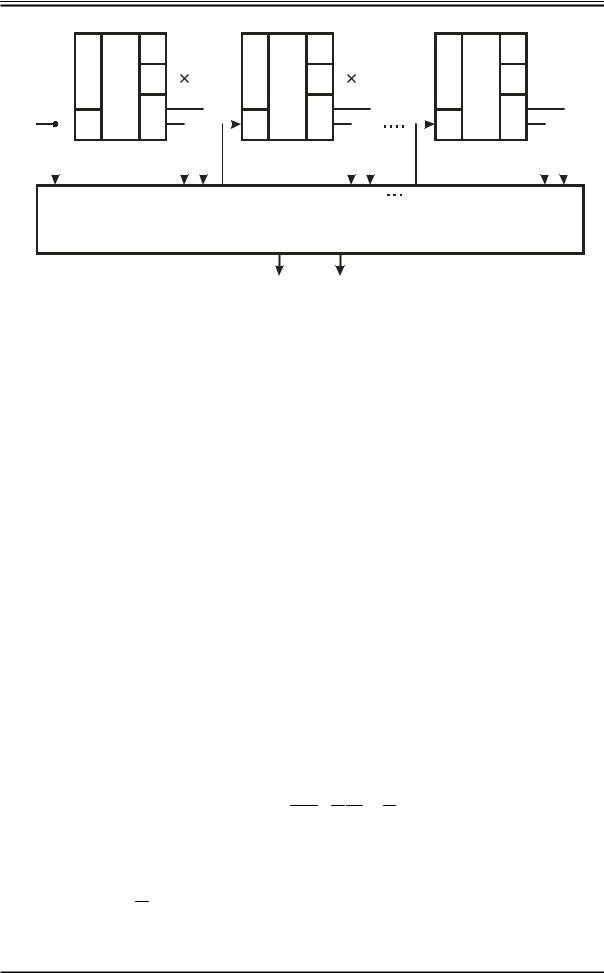

3.3.3. Сумматоры с последовательным переносом

Для сложения двух n-разрядных двоичных чисел необходимо использовать (n-1) полных и один полусумматор (для самого младшего разряда. Выход переноса каждого разряда подключается ко входу переноса следующего по старшинству разряда. Для возможности наращивания разрядности суммируемых чисел и в самом младшем разряде ставят

полный сумматор (рис. 3.34). Значения суммы и переноса S1 и c2 примут истинное значение после того, как закончится выполнение операций в самом младшем сумматоре и поступит сигнал переноса c1 . Верное значение S3 и c4 будет получено после того, как сигналы переноса

последовательно сформируются в каждом сумматоре. Поэтому такие схемы называются сумматорами с последовательным переносом.

76

а)

c0 |

|

C0 SM C1 |

c1 |

|

C0 |

SM C1 |

c2 |

|

c3 |

|

C0 SM C1 |

c4 |

|||||||

|

|

|

|

|

|

|

|

||||||||||||

|

s0 a1 |

|

|

s1 |

|

|

s3 |

||||||||||||

a0 |

|

A0 |

S0 |

|

|

|

A0 |

S0 |

a3 |

|

A0 |

S0 |

|||||||

|

|

|

|

||||||||||||||||

b0 |

|

B0 |

|

b1 |

|

|

|

B0 |

|

|

b3 |

|

B0 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

б) |

|

15 |

|

C0 |

SM C4 14 |

|

|

|

|

|

|

|||||||

|

|

|

|

1011 |

|

A0 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

8 |

|

|

B0 |

S0 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

||||

|

|

|

|

7 |

|

6 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

B1 |

S1 |

|

|

|

|

|

|

|

|||

|

|

|

|

3 |

|

2 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

A2 |

S2 |

|

|

|

|

|

|

|

|||

|

|

|

|

4 |

|

15 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

B2 |

S3 |

|

|

|

|

|

|

|

|||

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

A3 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

B3 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

- 12, +5В - 5 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Рис. 3.34. 4-разрядный сумматор с последовательным переносом: а – схема; б

– УГО ИС К155ИМ3

Примеры ИС:

К155ИМ3 - 4-разрядный сумматор с последовательным переносом

(рис.3.34б).

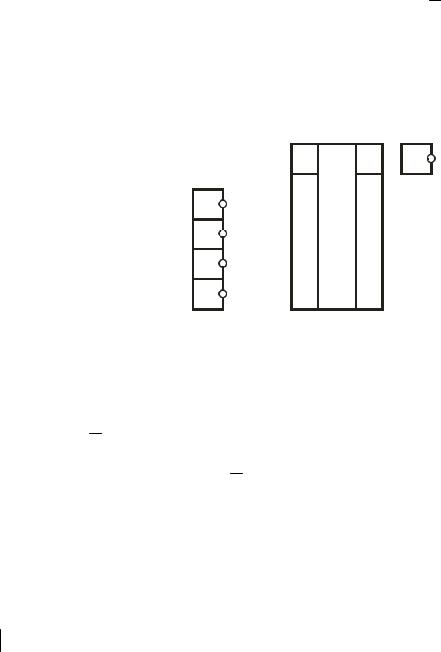

3.3.4. Сумматоры с параллельным переносом

Для уменьшения времени сложения многоразрядных чисел применяют способ суммирования с параллельным переносом, основанный на вычислении всех сигналов переноса непосредственно по значениям

входных переменных. Если обозначить g0 = a0 b0 и p0 = a0 b0 , то

сигнал переноса полного одноразрядного сумматора можно определить следующим образом:

c1 = g0 + p0 c0 .

Сигнал g0 равен единице тогда, когда перенос в данном разряде

обусловлен значениями суммируемых |

величин |

a0 и b0 |

( a0 =b0 =1). |

|

Поэтому g0 называют функцией генерации |

переноса. |

Сигнал |

p0 |

|

показывает, передается ли полученный перенос |

c0 в следующий |

по |

||

старшинству разряд. В связи с |

этим p0 |

называют |

функцией |

|

распространения переноса. |

|

|

|

|

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1

77 |

КОМБИНАЦИОННЫЕ УСТРОЙСТВА |

|

|

Аналогичные функции можно вывести и для остальных разрядов суммируемых чисел:

c2 = a1 b1 +(a1 b1 ) c1 = g1 + p1 c1 = g1 + p1 g0 + p1 p0 c0 ; c3 = g2 + p2 c2 = g2 + p2 g1 + p2 p1 g0 + p2 p1 p0 c0

и т.д.

Из полученных формул следует, что сигнал переноса в каждый разряд может быть вычислен с использованием функций gi и pi

непосредственно по значениям входных переменных. Для нахождения функций генерации и распространения переноса не требуется

дополнительных аппаратурных затрат, так как gi и pi определяются в

каждом одноразрядном сумматоре. Поэтому время формирования всех сигналов переноса одинакового и определяется задержкой распространения в двух элементах (И и ИЛИ). Схема 4-разрядного сумматора с параллельным переносом приведена на рис. 3.35. Сигналы

переноса C1 −C3 формируются с помощью схемы ускоренного переноса,

работающей в соответствии с приведенными выше формулами. Необходимые для ее работы функции генерации и распространения

переноса gi и pi поступают с одноразрядных сумматоров. Схема ускоренного переноса формирует также функции генерации и распространения переноса всего 4-разрядного сумматора G и P , определяемые следующим образом:

c4 = g3 + p3 g2 + p3 p2 g1 + p3 p2 p1 g0 + p3 p2 p1 p0 c0 =G +P c0 .

Наличие выходов G и P позволяет наращивать разрядность суммируемых чисел параллельным способом. Для формирования входных сигналов переноса отдельных 4-разрядных сумматоров можно использовать схему переноса, идентичную показанной на рис. 3.35. На ее

входы pi и gi |

необходимо подавать выходные сигналы P и G |

отдельных 4-разрядных сумматоров с параллельным переносом.

78

a0 |

|

|

|

SM S0 |

s0 |

|

a1 |

|

|

|

SM S0 |

s1 |

|

a3 |

|

|

|

SM S0 |

|

s3 |

|

|

|

A0 |

|

|

|

|

A0 |

|

|

|

|

A0 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

с4 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

b0 |

|

|

B0 |

C1 |

|

|

b1 |

|

|

B0 |

C1 |

|

|

b3 |

|

|

B0 |

C1 |

|

||

|

|

|

|

|

|

|

|

|

|

||||||||||||

c0 |

|

|

G0 |

|

|

|

|

|

|

|

G0 |

|

|

|

|

|

|

G0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

C0 |

P0 |

|

|

|

|

|

|

C0 |

P0 |

|

|

|

|

|

C0 |

P0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C0 |

P0 G0 C1 |

P1 G1 |

C3 |

P3 G3 |

GRP (Схема ускоренного переноса)

G P

Рис. 3.35. 4-разрядный сумматор с параллельным переносом

Примеры ИС:

К155ИП4 - схема ускоренного переноса для 4-разрядных арифметико-логических устройств К155ИП3.

3.3.5. Устройства для вычитания чисел

Устройство для вычитания чисел, представленных в двоичной форме, может быть построено на основе сумматора. Рассмотрим

вычитание двух целых положительных n-разрядных чисел A = an−1...a1a0 и B = bn−1...b1b0 . Разность ( A − B ) можно представить в следующей форме:

D = A – B = A + (C – B) – C .

Если число C выбрано так, что нахождение дополнения B до C , т.е. разности ( C − B ), и вычитание C можно выполнить без специальных схем для вычитания, то разность D действительно определяется с помощью сумматора. Этому условию удовлетворяет, например, число C = 2n −1, код которого представляет собой n единиц. В этом случае дополнение B до C представляет собой поразрядное дополнение числа B до 1:

(C −B) =2n −1−bn−1...b1b0 =bn−1...b1b0 = B,

которое может быть выполнено инвертированием значений всех разрядов числа B . При таком выборе числа C разрядность равна

D = A + B −2n +1.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1

79 |

КОМБИНАЦИОННЫЕ УСТРОЙСТВА |

||||

|

|

|

|

|

|

Если A > B , то (A + |

|

+1) > 2n , что означает появление единицы |

|||

B |

|||||

переноса из разряда с индексом ( n −1) |

в разряд с индексом n при |

||||

суммировании A , |

|

и 1. Вычитанию 2n |

из этой суммы соответствует |

||

B |

|||||

инверсия разряда переноса. Сумму же позволяет получить n -разрядный

сумматор, на входы которого поступают коды A и B . Для добавления 1 надо подать единичный уровень на вход переноса младшего разряда сумматора.

Соответствующая приведенному алгоритму схема показана на рис.

3.36.

|

|

|

|

|

|

|

|

|

S |

|

|

|

|

“1“ |

|

C0 |

SM C4 |

|

1 |

|

|

|

|

|

|

|

|

|||||

|

|

|

a0 |

|

A0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

b0 |

|

1 |

|

|

|

|

|

|

||

|

|

|

B0 |

|

|

|

|

|

||

|

a1 |

|

S0 |

|

|

|

|

|||

b1 |

|

1 |

|

A1 |

|

|

||||

|

|

|

|

|||||||

|

|

|

B1 |

S1 |

|

|

||||

|

a2 |

|

|

|||||||

b2 |

|

1 |

|

A2 |

S2 |

|

|

|||

|

|

|

||||||||

|

|

|

B2 |

S3 |

|

|

||||

|

a3 |

|

|

|||||||

b3 |

|

1 |

|

A3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

B3 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

Рис.3.36. Схема устройства для вычитания чисел

На выходах сумматора действительно появляется двоичный код разности:

A + B +1 − 2n = A + 2n −1 − B +1 − 2n = A − B = dn−1...d1d0 .

Если A < B , то (A + B +1) < 2n и переноса из разряда с индексом

( n −1) в разряд с индексом n нет (перенос равен нулю). В этом случае на выходах сумматора появляется двоичный код, равный

|

|

|

|

|

|

|

|

n |

|

|

|

n |

|

~ |

~ ~ |

|

|

|

|

|

A + |

B +1 = A + 2 |

−1 − B |

+1 = 2 |

|

|

|||||||

|

|

|

|

|

|

− ( A − B) = dn−1 |

...d1d , |

|

||||||||

|

|

|

|

где |

~ |

~ ~ |

|

дополнение |

|

абсолютной |

величины |

разности |

||||

|

|

|

|

|

dn−1 |

...d1d - |

|

|

||||||||

D |

|

= |

|

A − B |

|

до |

2n . При этом |

на |

инвертированном |

выходе |

переноса |

|||||

|

|

|

||||||||||||||

единичный уровень. Объединяя эти два случая, и рассматривая инвертированный выход переноса в качестве знакового разряда, приходим к выводу, что разность представлена на выходе сумматора в дополнительном коде (см. разд. 1.6):

[D]ДК |

0 d |

...d d |

, |

если ( A − B) > 0, |

= ~n−1 |

~1 ~0 |

|

если ( A − B) < 0. |

|

|

1 dn−1...d1d0 , |

|||

80

Описанным способом выполняется вычитание чисел в ИС К155ИП3

.

С помощью сумматора (без дополнительных инверторов) можно выполнять арифметические операции над числами со знаком, если их представить в дополнительном коде. При этом старший разряд будет носителем информации о знаке. Если исходные данные представлены в прямом коде, то они могут быть преобразованы в дополнительный код с помощью схемы рис. 3.37. Пусть на вход поступает число A в прямом коде:

[A]ПК |

= 0 a2a1a0 , |

если A ≥0, |

|

|

1 a2a1a0 , |

если A ≤0. |

|

Если |

знаковый |

разряд S = 0 (число |

A неотрицательное), то |

выходное число повторяет входное: |

|

||

S3 S2 S1S0 = 0 a2 a1a0 . |

|

||

Если |

S =1( A <0 ), то разряды a2 a1a0 |

будут проинвертированы |

|

элементами ИСКЛЮЧАЮЩЕЕ ИЛИ и в сумматоре сложены с 1:

S3S2 S1S0 =1 a~2 a~1a~0 ,

где a~2 a~1a~0 = a2 a1a0 +1.

Если на вход подан отрицательный нуль (1000), то он преобразуется в дополнительный код нуля (0000). Сопоставление этих расчетов с данными табл. 1.5 подтверждает, что схема действительно преобразует прямой код в дополнительный. С ее помощью можно выполнить обратное преобразование.

S |

C0 |

SM C4 |

|

|

|

=1 |

|

|

|

|

|

A0 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|||||

a0 |

|

|

|

|

|

|

|

|

B0 |

S0 |

|

|

|

=1 |

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

B1 |

S1 |

||

|

|

|

|

|

||||||

a1 |

|

|

|

|

|

|

|

|

A2 |

S2 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

B2 |

S3 |

|

|

|

=1 |

|

|

|

|

|

||

|

|

|

|

|

|

|

A3 |

|

||

a2 |

|

|

|

|

|

|

|

|

B3 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.37. Преобразователь прямого кода в дополнительный (или дополнительного в прямой)

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1

81КОМБИНАЦИОННЫЕ УСТРОЙСТВА

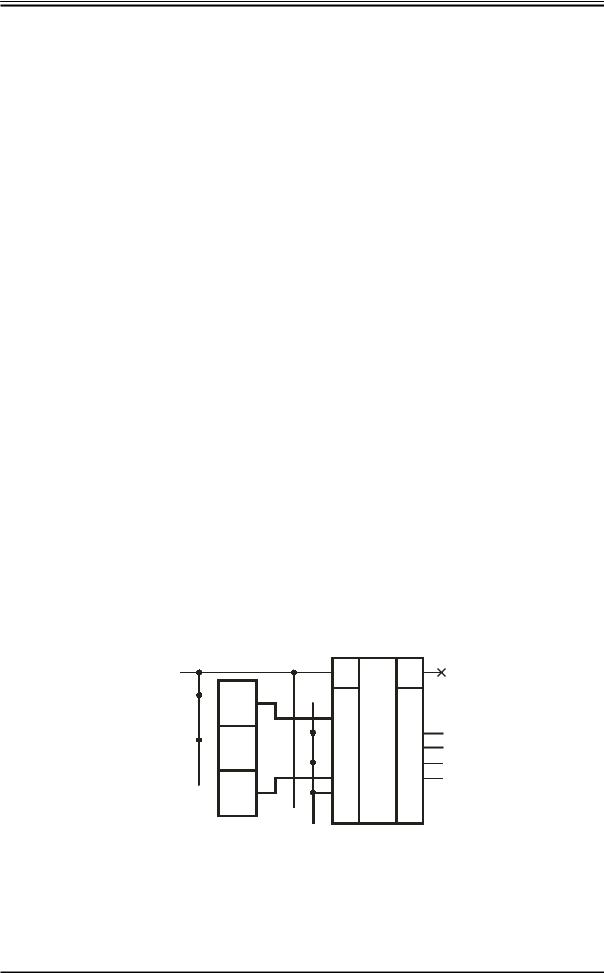

3.3.6.Арифметико-логические устройства

Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций над двумя многоразрядными кодовыми словами данных. Тип выполняемой операции определяется кодовым словом, поступающим на управляющие входы. АЛУ является основным узлом центрального процессора универсальных вычислительных машин и других систем обработки данных в цифровой форме. Оно может насчитывать от одной до десятков ИС. Хотя АЛУ могут выполнять многие функции, основные операции остаются главными.

Примеры ИС:

К531ИК2П - 4-разрядное арифметико-логическое устройство (выполняет 8 арифметических и 3 логических операции).

К155ИП3 - 4-разрядное арифметико-логическое устройство (выполняет 32 арифметических и 16 логических операций).

К155ИП3 (рис.3.38) имеет 4x2 входов A0 − A3 и B0 −B3 для чисел

данных, над которыми выполняются арифметические (М=0) или логические (М=1) операции. Тип операции определяется кодовым словом

выбора функции на входах V0 −V3 . Результат арифметической или логической операции - на выходах F0 −F3 .

7 |

C0 ALU C4 16 |

|||

|

||||

2 |

A0 |

G 17 |

||

23 |

||||

A1 |

|

|

||

21 |

P 15 |

|||

A2 |

||||

19 |

A3 |

|

|

|

1 |

B0 |

K 14 |

||

2022 |

||||

B1 |

|

|

||

18 |

B2 |

F0 |

9 |

|

B3 |

||||

|

||||

6 |

V0 |

F1 10 |

||

5 |

||||

V1 |

|

|

||

4 |

F2 |

11 |

||

V2 |

||||

3 |

|

|||

V3 |

F3 13 |

|||

8 |

||||

M |

||||

|

|

|

||

Рис. 3.38. Арифметико-логическое устройство К155ИП3

Основной элемент АЛУ - 4-разрядный сумматор со схемой ускоренного переноса. Для наращивания разрядности обрабатываемых

82

чисел используются вход C0 и выход C4 - переноса, а также выходы

генерации и распространения переноса G и P . Выход K (с открытым коллектором) используется для определения равенства чисел A и

B ( K =1, если в режиме вычитания при C0 =1 равны коды чисел). Для

организации ускоренного переноса при объединении нескольких АЛУ с целью наращивания разрядности предназначена ИС К155ИП4.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1

83 |

ЛИТЕРАТУРА |

|

|

|

|

ЛИТЕРАТУРА

1.Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. –М.: Мир, 2001.

2.Новиков Ю., Скоробогатов П. Основы микропроцессорной техники: Курс лекций. –М.: ИНТУИТ.РУ, 2003.

3.Белов А. Самоучитель по микропроцессорной технике. –М.: Наука и техника, 2003.

4.Новожилов О.П. Основы цифровой техники: Учебное пособие. –М.: Радио Софт, 2004.

5.Угрюмов Е. Цифровая схемотехника от логического элемента до перспективных БИС/СБИС с программируемыми структурами. –СПб.: БХВ – Петербург, 2004.

6.Бойко В. Схемотехника электронных систем. Цифровые устройства.

–СПб.: БХВ – Петербург, 2004.

7.Бойко В. Схемотехника электронных систем. Микропроцессоры и микроконтроллеры. –БХВ – Петербург, 2004.

8.Нарышкин А.К. Цифровые устройства и микропроцессоры. –М.: Изд. центр «Академия», 2004.

9.Уилкинсон Б. Основы проектирования цифровых схем. –Киев.: Вильямс, 2004.

10.Фрике К. Вводный курс цифровой электроники. –М.: Техносфера, 2004.

11.Опадчий Ю.А. Аналоговая и цифровая электроника. Учебник для ВУЗов. –М.: Горячая линия – Телеком, 2005.

12.Точчи Р. Уидмер Н. Цифровые системы. Теория и практика. –Киев.: Вильямс, 2004.

13.Алексеева Л.А., Буль М.П., Гласман К.Ф., Покопцева М.Н.. Методические указания по выполнению лабораторных работ для студентов специальности 201400 «Аудиовизуальная техника» по курсу «Цифровые устройства и микропроцессоры». – СПб.: СПбГУКиТ, 2002.

84

ОГЛАВЛЕНИЕ

ВВЕДЕНИЕ ……………………………………………………………. |

3 |

1. СИСТЕМЫ СЧИСЛЕНИЯ И КОДЫ …………………………..….. |

8 |

1.1. Системы счисления ……………………………………………. |

8 |

1.2. Двоично-десятичные коды …………...………………………… |

10 |

1.3. Унитарный код ………………………………………………….. |

11 |

1.4. Код Грея …………………………………. …..………………… |

11 |

1.5.Код Джонсона …………………………………………………… 12

1.6.Представление чисел со знаком ……………………………….. 13

1.7. Коды с обнаружением ошибок ………………………………… 16

1.8.Коды с исправлением ошибок …………………………………. 17

1.9.Форматы кодов ………………………………………………….. 20

2.БАЗОВЫЕ ЛОГИЧЕСКИЕ СХЕМЫ ………………………………. 23

2.1. Логические элементы …………………………………………… 23

2.1.1.Основные логические функции ……………………………. 23

2.1.2.Составление логических функций ……………...…………. 25

2.1.3.Производные основных логических функций …………..... 26

2.1.4. Логические элементы как схемы временной селекции ...… 28

2.1.5.Логические состязания ……………………………………… 29

2.2Триггеры …………………………………………………………... 30

2.2.1 Бистабильная ячейка …………………… ……………….... 30

2.2.2.Асинхронные и синхронные триггеры …………..……….. 32

2.2.3.Статический синхронный RS-триггер …………………….. 33

2.2.4Статический синхронный D-триггер ……………………….. 34

2.2.5Триггеры типа M-S ("ведущий-ведомый") …………………. 35

2.2.6.Динамический D-триггер ………………………………….. 38

2.2.7.Триггер Шмитта ………………………………………………. 41

2.3.Импульсные устройства на логических элементах ……………. 43

2.3.1.Интегральные схемы логических элементов

в линейном режиме …………………………………………. 43

2.3.2. Ждущие мультивибраторы ………………………………… |

44 |

2.3.3. Автоколебательные мультивибраторы ……………………. |

46 |

3. КОМБИНАЦИОННЫЕ УСТРОЙСТВА …………………………… |

48 |

3.1.Преобразователи кодов …………………………………………. 48

3.1.1.Шифраторы …………………………………………………. 48

3.1.2.Дешифраторы ……………………………………………….. 50

3.1.3.Дешифраторы - преобразователи двоичнодесятичного кода в код семисегментного индикатора ….. 54

3.1.4.Преобразователи двоичного кода в двоично-десятичный .. 56

3.1.5.Преобразователи двоично-десятичного кода в двоичный .. 58

3.1.6.Взаимное преобразование кода Грея и двоичного кода …. 60

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 1

85 СОДЕРЖАНИЕ

3.1.7. Схемы контроля четности и нечетности ………………… 61

3.2.Мультиплексоры и демультиплексоры ………………………. 63

3.2.1.Мультиплексоры ………………………………………….. 63

3.2.2. Мультиплексор как универсальная комбинационная схема |

66 |

3.2.3. Демультиплексоры ………………………………………… |

69 |

3.3. Арифметические устройства …………………………………… |

70 |

3.3.1.Компараторы ………………………………………………... 70

3.3.2.Одноразрядные сумматоры ………………………………… 73

3.3.3. Сумматоры с последовательным переносом ……………… 75

3.3.4.Сумматоры с параллельным переносом …………………… 76

3.3.5.Устройства для вычитания чисел ………………………….. 78

3.3.6.Арифметико-логические устройства ………………………. 81

ЛИТЕРАТУРА …………………………………………………………… 82