21

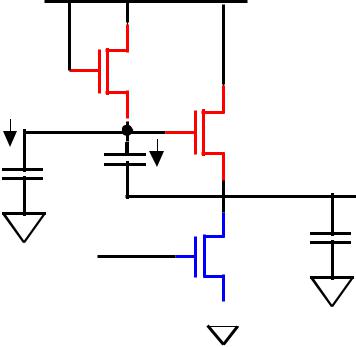

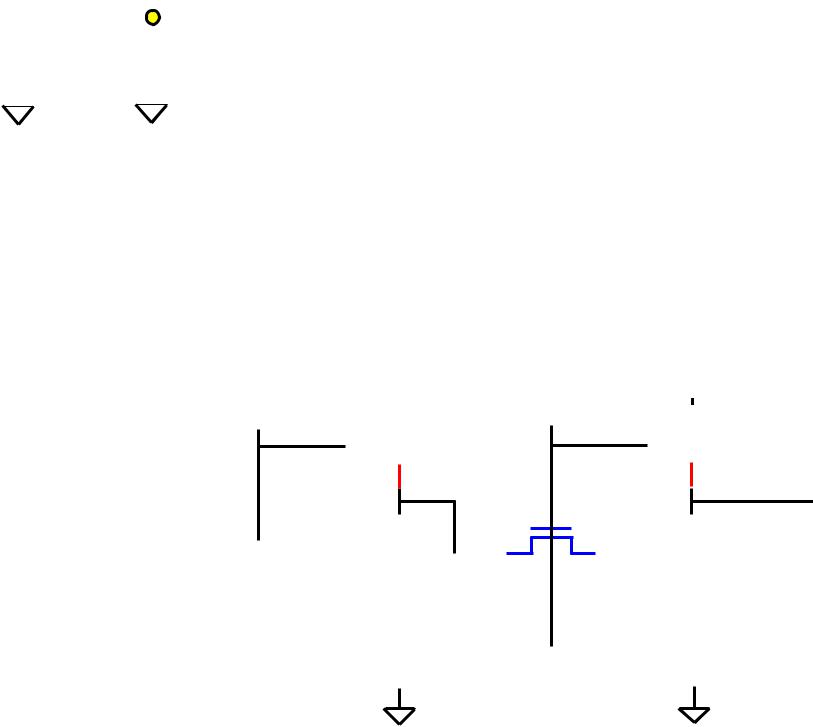

1. AT t = 0− LET Vin = VDD => Vout = VOL |

VDD |

|

|

||||

|

D |

|

|

||||

M1 is LIN, M2 is SAT, M3 is SAT |

|

Vx |

M3 |

D |

|

||

If I |

|

≈ 0 |

iCs |

S |

|

||

|

|

|

|

||||

D3 |

|

|

M2 |

|

|||

=> VGS3 - VT3(Vx) = 0 |

CS |

Cboot |

iCboot |

S |

Vout |

||

i.e. |

|

|

|

|

|

D |

|

Vx = VDD − VT 3(Vx ) |

|

|

|

|

|||

|

Vin |

|

M1 |

Cout |

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

2. AT t = 0, LET Vin |

switch from “1” to “0” |

S |

||

|

|

|

||

|

|

|

|

|

M1 -> OFF, Vout -> INCREASES

+ Vout causes Vx TO INCREASE due to Cboot and diode M3 to become reverse biased such that ID3 = 0. Then iCs + iCboot ≈ 0

iCs ≈ - iCboot => |

CS |

dV |

≈ Cboot |

d(Vout − Vx ) |

||||||||

x |

|

|

||||||||||

dt |

dt |

|||||||||||

|

|

|

|

|

|

|

|

|

||||

|

dVx |

≈ |

|

Cboot |

|

|

dVout |

Find Vx NEEDED for Vout = VDD |

||||

|

(CS + Cboot ) |

|

||||||||||

|

dt |

dt |

|

|

||||||||

Kenneth R. Laker, University of Pennsylvania

22

Find Vx NEEDED for Vout = VDD |

|

|

|

|||||||

dV |

|

C |

|

|

dV |

|

dVx » |

Cboot |

||

|

dt |

» (CS + Cboot ) |

dt |

=> |

|

dVout |

||||

|

(CS + Cboot ) |

|||||||||

|

x |

|

|

boot |

|

out |

|

|

|

|

INTEGRATING: Vout: VOL -> VDD AND Vx: VDD - VT3(Vx) -> Vx

Vx |

» |

|

|

Cboot |

VDD |

|

|

ò dVx |

|

|

ò dVout |

||||

|

|

|

|

|

|

|

|

VDD −VT 3 |

|

|

(CS + Cboot ) |

VOL |

+ Cboot )(VDD - VOL ) |

||

Vx = (VDD |

- VT 3(Vx )) + (CS |

||||||

|

|

|

|

|

|

Cboot |

|

FOR Cboot >> CS the max value for Vx:

Vx (max) = 2VDD − VT 3(Vx ) − VOL

The min value of Vx is that value required to maintain M2 ON (VGS2 = Vx - VDD = VT2n, i.e.

= (VDD |

- VT 3(Vx )) + (C + C |

|

)(VDD - VOL ) |

||

|

|

Cboot |

|

|

|

Kenneth R. Laker, University of Pennsylvania |

|

S |

boot |

|

|

|

|

|

|

|

|

23

= (VDD |

− VT 3(Vx )) + (C + C |

|

)(VDD − VOL ) |

||

|

|

Cboot |

|

|

|

|

|

S |

boot |

|

|

Vx(min) determines the required capacitance ratio, i.e.

|

|

|

Cboot |

|

|

|

= |

VT 2(Vout = VDD ) + VT 3(Vx ) |

||||||||

|

(C |

|

+ C |

boot |

) |

|

|

|

(V − V |

) |

|

|

||||

|

|

S |

|

|

|

|

|

|

|

DD OL |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

Cboot |

= |

|

|

|

|

|

VT 2(Vout = VDD ) + VT 3(Vx ) |

|

||||||

|

|

C |

S |

|

|

V |

|

|

− V − V (V = V ) − V (V ) |

|

||||||

|

|

|

|

|

DD |

|

|

OL |

T 2 out |

DD T 3 x |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MD: “dummy” nMOS enhancement device to realize Cboot >> CS

VDD

M3

M3

Vx

M2

M2

MD

Cboot Vout

CS = Cgb2 + Csb3 |

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

M1 |

||

in |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Kenneth R. Laker, University of Pennsylvania

24

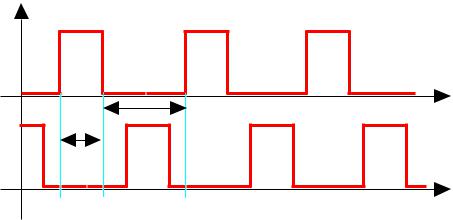

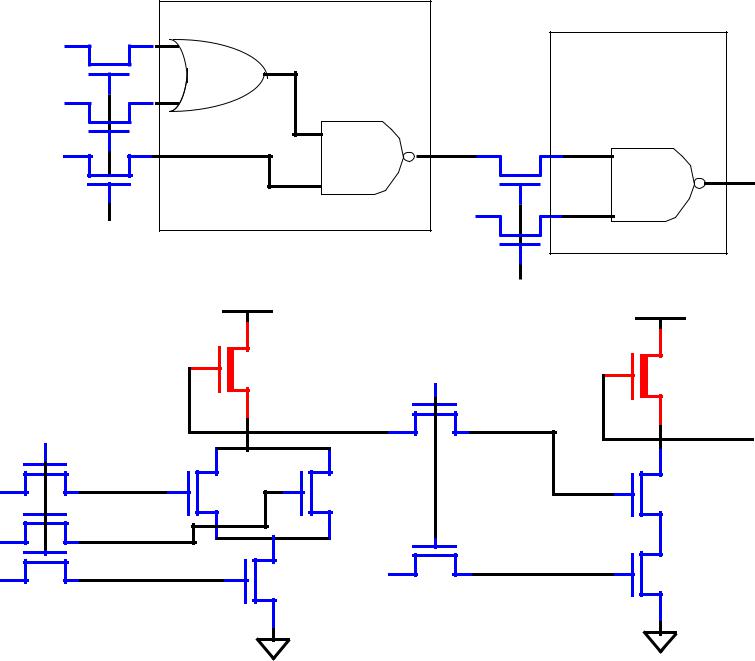

SYNCHRONOUS DYNAMIC CIRUIT TECHNIQUES

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COMB |

|

|

|

F1 |

|

|

|

|

|

|

COMB |

|

|

|

|

|

|

|

COMB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

LOGIC |

|

|

|

|

|

|

|

LOGIC |

|

|

|

|

|

|

|

|

|

LOGIC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

B |

|

|

|

|

|

|

1 |

|

C |

|

|

|

|

|

|

2 |

|

D |

|

|

|

|

|

|

|

3 |

|

|

|

F2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

φ |

1 |

|

|

|

|

|

|

|

φ2 |

|

|

|

|

|

φ |

1 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

φ1, |

φ2 NON-OVERLAPPING CLOCKS |

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

φ1 |

|

phase 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

t

φ2

t

phase 1

LOGIC LEVELS DURING INACTIVE CLOCK PHASE ARE STORED ON INPUT CAPS

Kenneth R. Laker, University of Pennsylvania

25

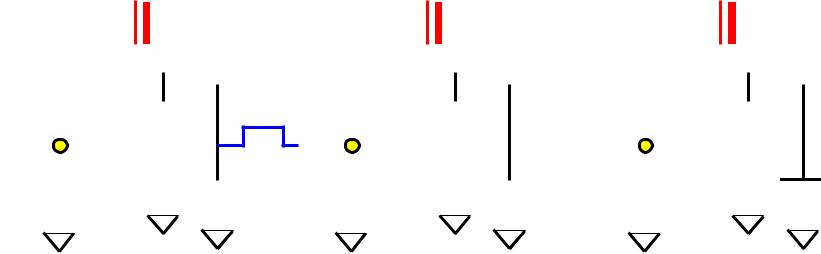

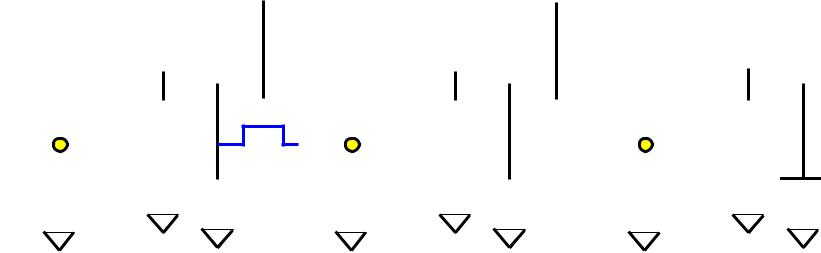

VDD |

VDD |

VDD |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

φ |

1 |

|

|

|

|

|

φ |

2 |

|

|

|

|

|

|

φ |

1 |

|

|

|

|

|

Vout |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout3 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Vin |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

Cin1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Cin2 |

|

|

|

|

|

|

|

|

|

|

|

|

Cin3 |

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 - STAGE DEPLETION LOAD DYNAMIC SHIFT REGISTER

MAX CLOCK FREQUENCY IS DETERMINED BY SIGNAL PROPOGATION DELAY THROUGH ONE INVERTER STAGE

Kenneth R. Laker, University of Pennsylvania

2 - STAGE SYNCRONOUS COMPLEX LOGIC CIRCUIT |

26 |

|||

|

||||

A |

STAGE 1 |

|

|

|

|

|

STAGE 2 |

|

|

|

|

|

|

|

B |

|

|

|

|

C |

|

|

F1 |

|

|

φ1 |

D |

|

|

|

|

|

||

|

VDD |

φ2 |

V |

|

|

|

|

DD |

|

|

|

φ2 |

|

|

φ1 |

|

|

F1 |

|

A |

|

|

|

|

B |

|

|

|

|

C |

|

D |

|

|

Kenneth R. Laker, University of Pennsylvania

ENHANCEMENT - LOAD DYNAMIC SHIFT REGISTER |

27 |

|||||||||||||||||||||||||

|

|

|

|

|||||||||||||||||||||||

|

VDD |

|

φ |

|

VDD |

|

|

φ |

VDD |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

φ2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

φ1 |

|

|

|

|

|

V |

out1 |

|

|

|

|

|

|

Vout2 |

|

|

|

|

|

Vout3 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout3 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Vin |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

Cin1 |

|

|

|

|

|

|

|

|

|

|

|

|

Cin2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Cin3 |

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

φ1 HIGH: Vin transfers to Cin1, 1st and 3rd stage loads are OFF.

φ2 HIGH: 1st stage load turns ON , 1st stage output achieves its valid

logic level, and Vout1 is trasfers to Cin2.

φ1 HIGH: Vout2 transfers to Cin3, next Vin transfers to Cin1(pipeline), 1st and 3rd stage loads are OFF

VOL -> kdriver/kload => RATIOED DYNAMIC LOGIC

Kenneth R. Laker, University of Pennsylvania

28

VDD |

|

VDD |

|

|

|

|

φ1 |

||||||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

φ2 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

φ1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Z |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

nMOS |

|

|

|

|

|

|

|

|

nMOS |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

B |

|

|

|

|

|

|

|

|

|

LOGIC |

|

|

|

|

|

|

|

|

LOGIC |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

C |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

D |

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GENERAL CIRCUIT STRUCTURE OF RATIOED SYNCRONOUS

DYNAMIC LOGIC

Kenneth R. Laker, University of Pennsylvania

|

ENHANCEMENT - LOAD DYNAMIC SHIFT REGISTER |

29 |

|||||||||||||

φ |

VDD |

φ2 |

VDD |

φ1 |

VDD |

|

|||||||||

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vout1 |

|

|

|

|

|

|

Vout2 |

|

|

|

|

Vout3 |

||||||||

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout3 |

||

Vin |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

Cin1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Cin2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cin3 |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cini << Couti-1 for i = 2, 3 => minimize charge sharing

φ1 HIGH: Vin transfers to Cin1, 1st and 3rd stage loads are ON, 1st stage output Vout1 achieves its valid level.

φ2 HIGH: Vout1 transfers to Cin2, 2nd stage load turns ON If Vout1 = HIGH: This level transfers to Cin2.

If Vout1 = LOW: Cout1 fully discharges to Vout1 = 0 due to HIGH level stored on Cin1.

φ1 HIGH: Vout2 transfers to Cin3, next Vin transfers to Cin1(pipeline). VOL -> 0 => RATIOLESS DYNAMIC LOGIC

Kenneth R. Laker, University of Pennsylvania

|

|

|

|

|

|

|

φ2 |

|

|

|

|

|

|

φ2 = 0: Qout1 |

= Cout1Vb and Qin2 = Cin2Va |

30 |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

V |

|

|

|

|

Va |

φ2 = 1: Qtotal |

= Cout1Vb + Cin2Va and Ctotal = Cout1 + Cin2 |

||||||||||||||||||||||||||||||

|

|

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

b |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The resulting voltage across Ctotal is |

|

|

|

||||||||||||||||||

|

|

|

|

|

|

Cout1 |

|

|

|

|

Cin2 |

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V = |

|

|

Qtotal |

= |

Cout1Vb + Cin2Va |

|

|

|

|||||||||||||

|

|

|

CHARGE |

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

Cout1 + Cin2 |

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

R |

Ctotal |

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

SHARING |

If Vb = VDD and Va |

<< Vb => VR |

≈ |

Cout1VDD |

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cout1 |

+ Cin2 |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VR ≈ VDD if Cin2 << Cout1 |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

GENERAL CIRCUIT STRUCTURE OF RATIOLESS SYNCRONOUS |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DYNAMIC LOGIC |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

|

|

|

|

|

VDD |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

φ1 |

|

|

|

|

|

|

|

φ2 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Z

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

nMOS |

|

|

|

|

|

|

|

|

nMOS |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

LOGIC |

|

|

|

|

|

|

|

|

LOGIC |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

2 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

D |

||||||||||||

Kenneth R. Laker, University of Pennsylvania