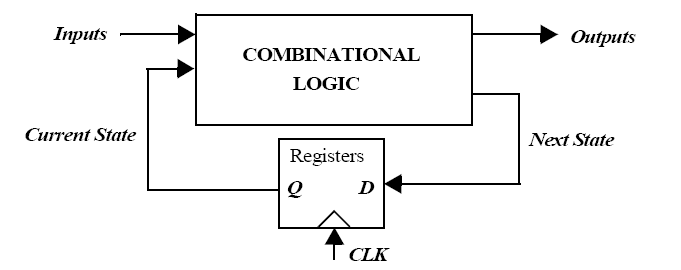

DESIGNING SEQUENTIAL LOGIC CIRCUITS

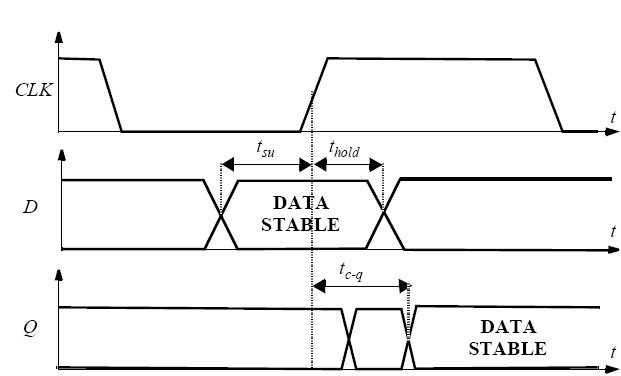

Timing Metrics for Sequential Circuits

![]()

![]()

Classification of Memory Elements

-

Foreground versus Background Memory

-

Static versus Dynamic Memory

-

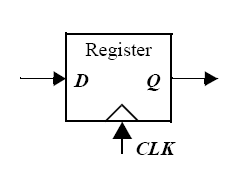

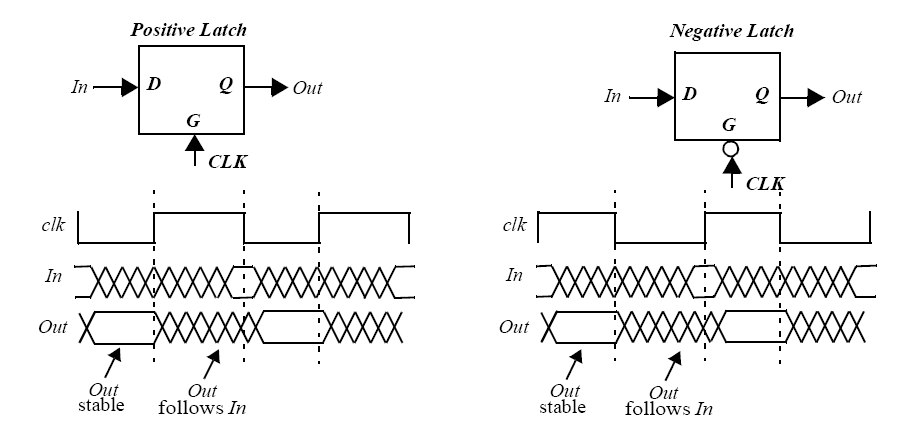

Latches vs. Registers

Static Latches and Registers

-

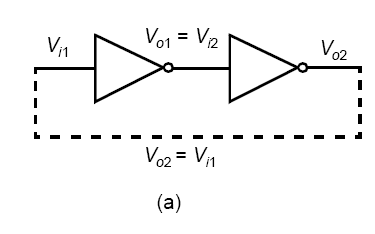

The Bistability Principle

-

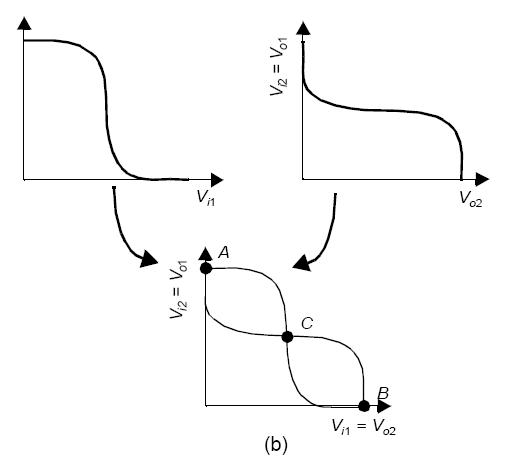

SR Flip-Flops

-

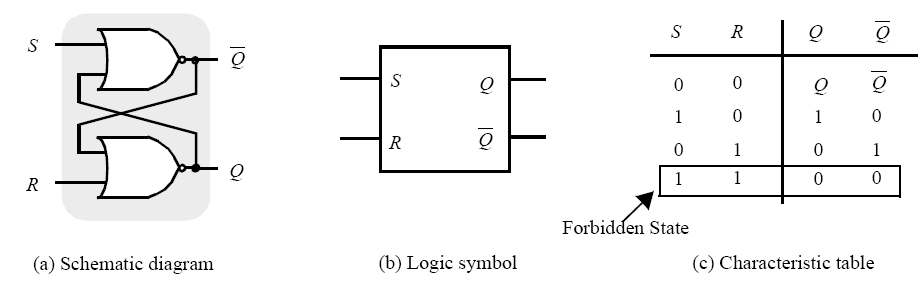

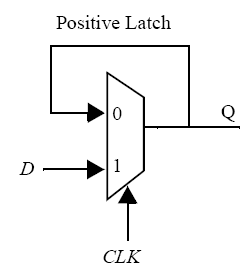

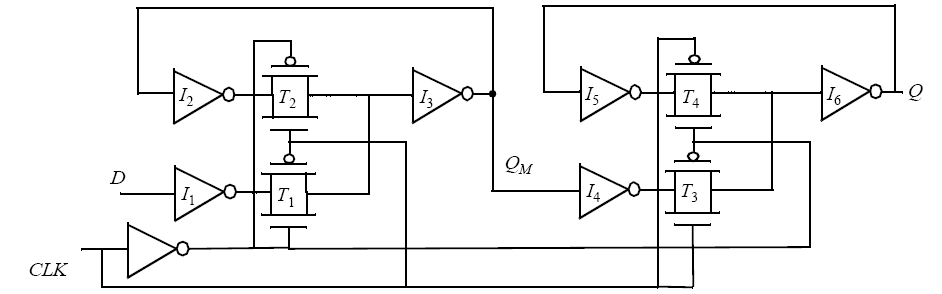

Multiplexer Based Latches

![]()

-

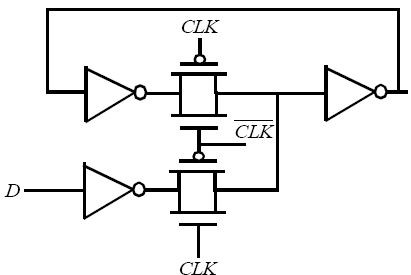

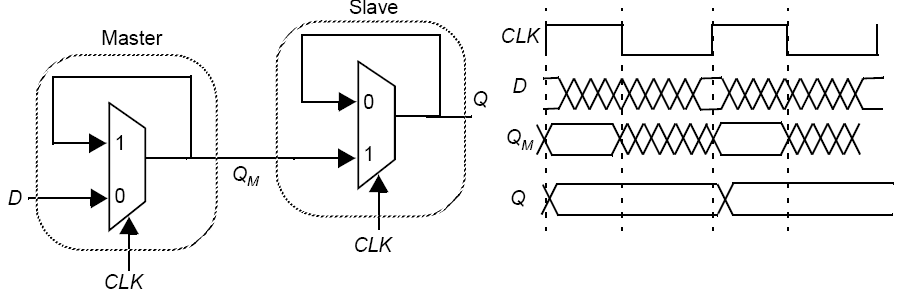

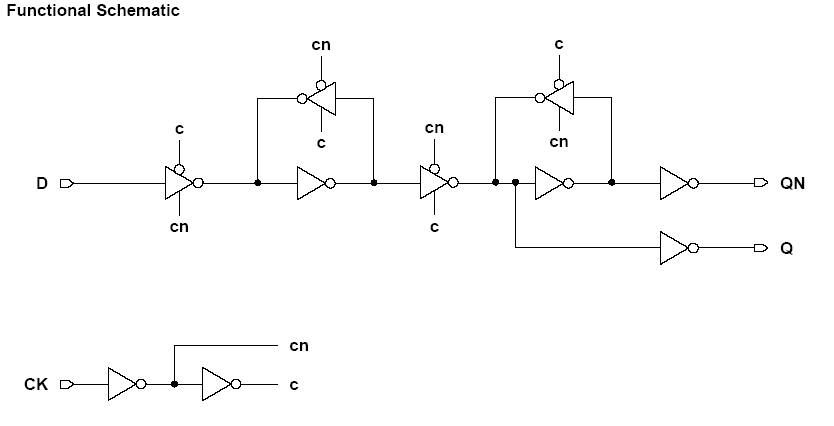

Master-Slave Based Edge Triggered Register

![]()

-

Non-ideal clock signals

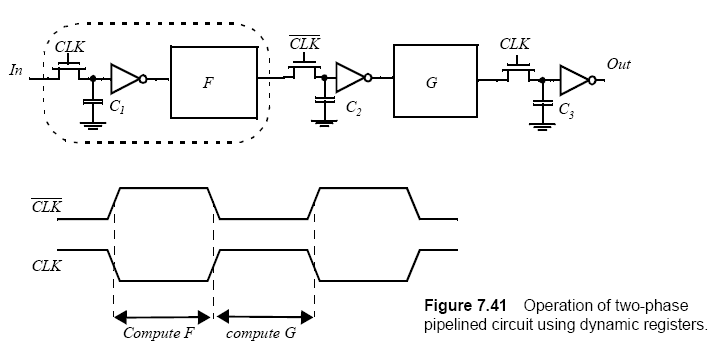

Dynamic Latches and Registers

-

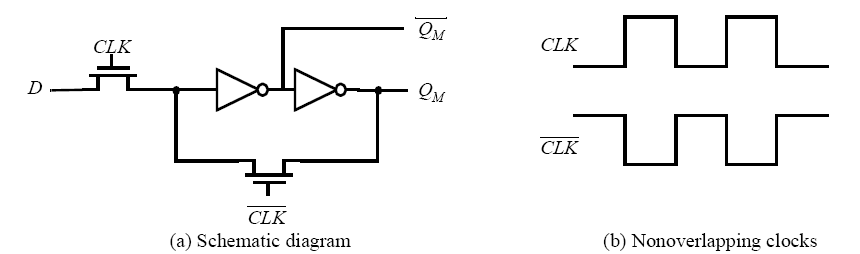

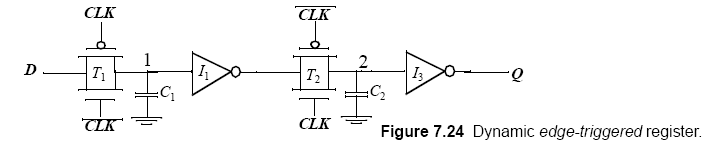

Dynamic Transmission-Gate Based Edge-triggered Registers

-

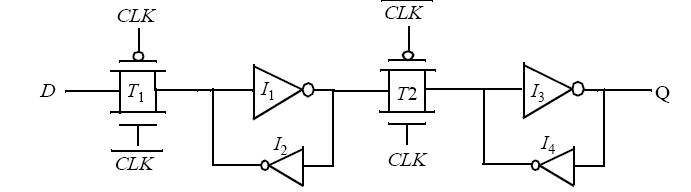

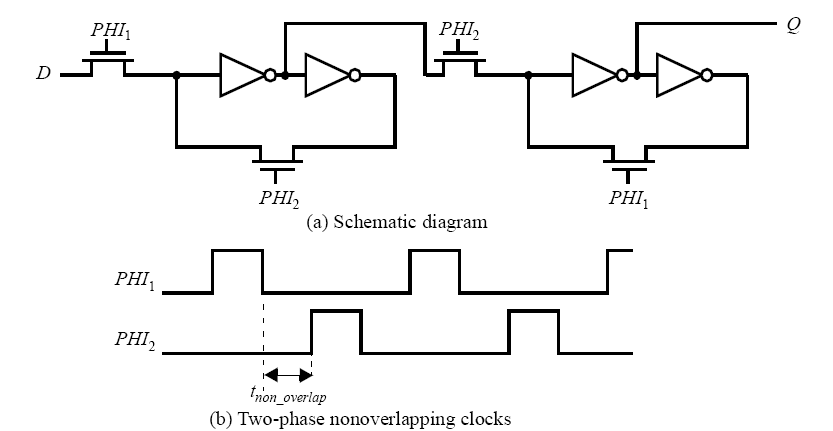

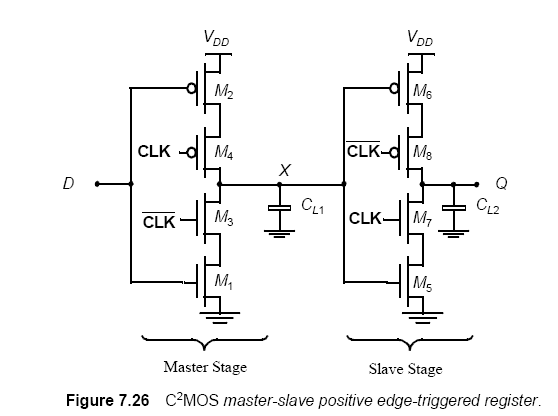

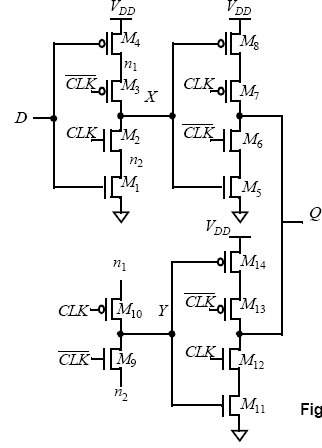

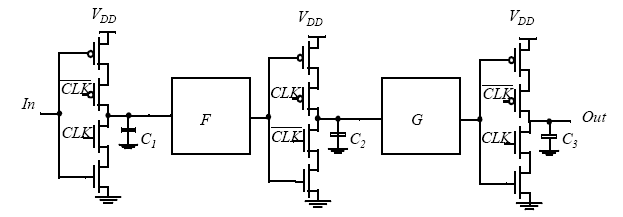

C2MOS Dynamic Register:

-

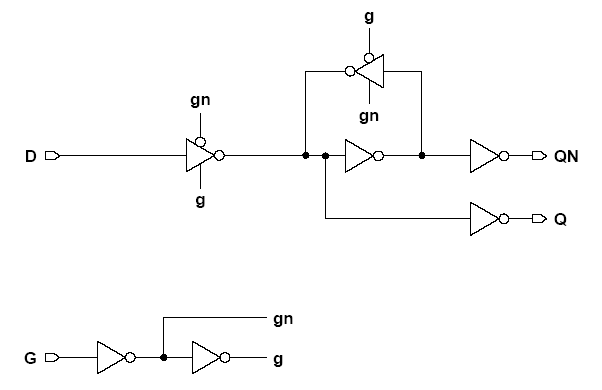

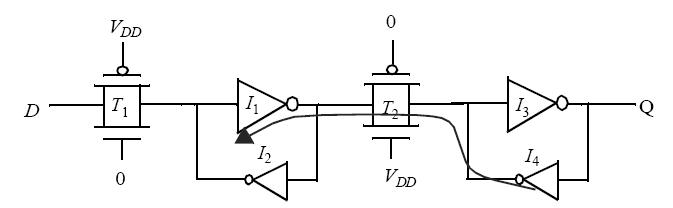

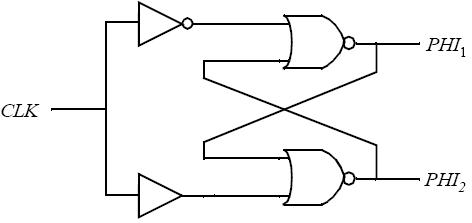

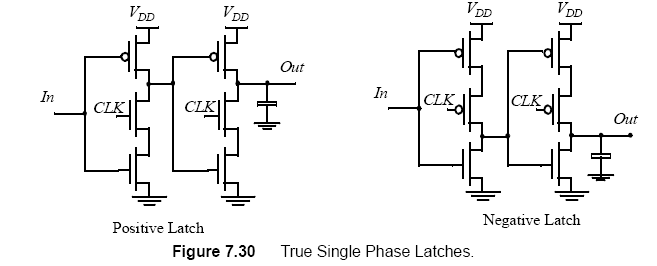

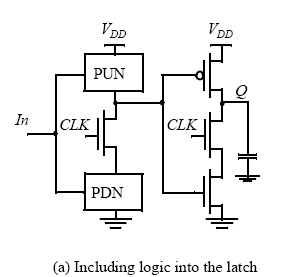

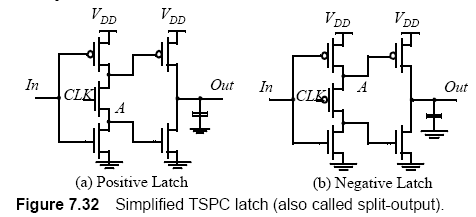

True Single-Phase Clocked Register (TSPCR)

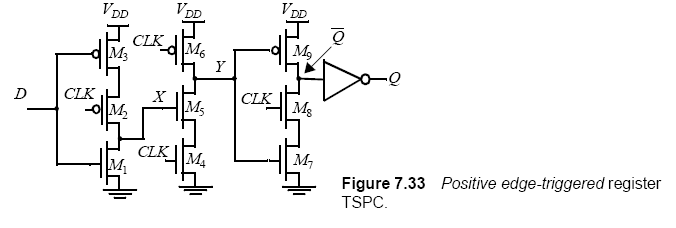

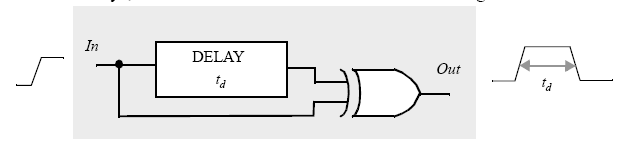

Pulse Registers

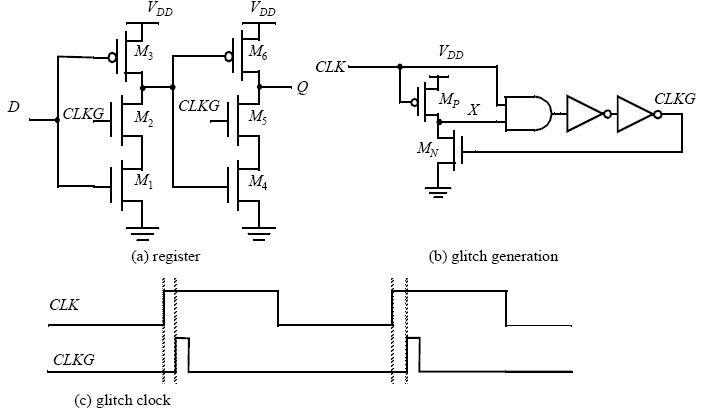

Sense-Amplifier Based Registers

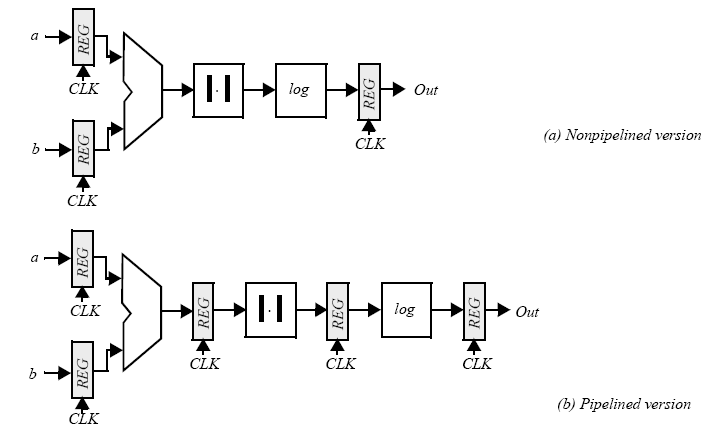

Pipelining: An approach to optimize sequential circuits

![]()

-

Latch- vs. Register-Based Pipelines

-

NORA-CMOS—A Logic Style for Pipelined Structures

Non-Bistable Sequential Circuits

-

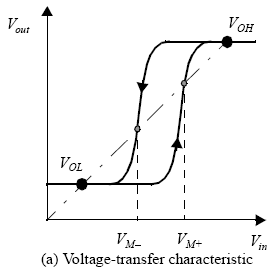

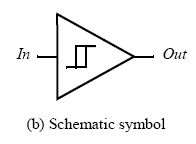

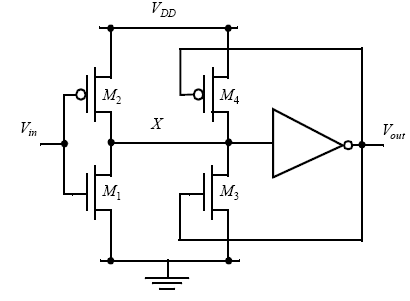

The Schmitt Trigger

-

Monostable Sequential Circuits

-

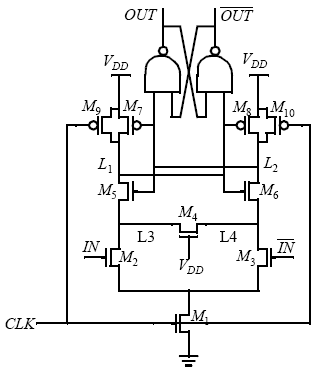

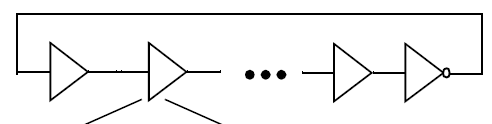

Astable Circuits

![]()

Summary

• The cross-coupling of two inverters creates a bistable circuit, called a flip-flop. A third potential operation point turns out to be metastable; that is, any diversion from this bias point causes the flip-flop to converge to one of the stable states.

• A latch is a level-sensitive memory element that samples data on one phase and holds data on the other phase. A register (sometime also called a flip-flop) on the other hand samples the data on the rising or falling edge. A register has three important parameter the set-up time, the hold time, and the propagation delay.

• Registers can be static or dynamic. A static register holds state as long as the power supply is turned on. Dynamic memory is based on temporary charge store on capacitors. The primary advantage is the reduced complexity and higher performance/lower power. Charge on a dynamic node leaks away with time, and hence dynamic circuits have a minimum clock frequency.

• There are several fundamentally different approaches towards building a register. The most common and widely used approach is the master-slave configuration which involves cascading a positive latch and negative latch (or vice-versa).

• Registers can also be constructed using the pulse or glitch concept. An intentional pulse is used to sample the input around an edge. Generally, the design of such circuits requires careful timing analysis across all process corners. Sense-amplifier based schemes are also used to construct registers and are to be used when high performance or low signal swing signalling is required.

• Choice of clocking style is an important consideration. Two phase design can result in race problems. Circuit techniques such as C2MOS can be used to eliminate race conditions in two-phase clocking. Another option is to use true single phase clocking. However, the rise time of clocks must be carefully optimized to eliminate races.

• The combination of dynamic logic with dynamic latches can produce extremely fast computational structures, the NORA logic style, is very effective in pipelined datapaths.

• Monostable structures have only one stable state. They are useful as pulse generators.

• Astable multivibrators, or oscillators, possess no stable state.

• Schmitt triggers display hysteresis in their dc characteristic and fast transitions in their transient response. They are mainly used to suppress noise.