- •Содержание дипломного проекта:

- •Глава 1. Специальная часть. Разработка программного обеспечения управления автоматизированным комплексом многоканальной связи 6

- •1.7.1 Структуры данных 29

- •Введение

- •1.2 Особенности разработки программного обеспечения для микропроцессорных систем

- •1.3 Использование контроллера ат89с51

- •1.3.1 Основные программно-доступные устройства микроконтроллера ат89с51

- •1.3.2 Структурная схема микроЭвм серии мк51

- •1.3.3 Адресные пространства ат89с51

- •1.3.4 Характеристики средств языка ассемблера

- •1.4 Интерфейсы в системах связи

- •1.4.1 Классификация интерфейсов

- •1.4.2 Основы асинхронной последовательной связи

- •1.4.2.1 Контроль по четности и обнаружение ошибок

- •1.4.2.2 Управление потоком с помощью xon/xoff

- •1.5 Общие методы ввода/вывода через коммуникационный порт

- •1.5.1 Последовательный порт с точки зрения программиста

- •1.6 Информационный обмен контроллер - эвм с использованием интерфейса rs-232

- •1.7 Создание программы управления автоматизированным комплексом многоканальной связи

- •1.7.1 Структуры данных

- •1.7.2 Составляющие программы

- •1.7.2.1 Основная программа

- •1.7.2.2 Подпрограмма перезаписи карты памяти

- •1.7.2.3 Подпрограмма связи с внешней пэвм через последовательный порт

- •1.7.3 Тестирование и отладка программы

- •1.7.4 Оформление программы и ее возможная модернизация

- •1.7.5 Надежность программного продукта

- •1.8 Заключение

- •2.2 Этапы решения задачи на эвм

- •1. Постановка задачи.

- •2. Составление проекта.

- •3. Алгоритмизация.

- •4. Программирование.

- •6. Отладка.

- •7. Тестирование.

- •8. Оформление программы.

- •9. Отчет о работе.

- •10. Модернизация.

- •2.3 Проектирование системы

- •2.3.1 Определение основных элементов системы

- •2.3.2 Структурный анализ

- •2.3.3 Структурное проектирование

- •2.3.4 Реализация и испытания

- •2.4 Вспомогательные средства проектирования

- •2.4.1 Графическая схема задания

- •2.4.2 Развернутый план проекта системы

- •2.5 Организация процесса проектирования

- •2.6 Необходимость тестирования программных продуктов

- •2.7 Отладка и общие принципы тестирования программ

- •Алгоритмическое тестирование

- •Функциональное или аналитическое тестирование

- •Содержательное тестирование

- •2.8 Типы тестов

- •2.9 Надежность программного обеспечения

- •2.9.1 Критерии надежности систем

- •2.9.2 Типы программного обеспечения с точки зрения надежности

- •2.9.3 Анализ надежности программного обеспечения

- •2.9.4 Диагностика функционирования комплексов программ

- •2.9.5 Основные факторы, влияющие на надежность функционирования комплексов программ

- •2.10 Разработка программной документации

- •2.11 Заключение

- •Глава 3 Организационно-экономическая часть

- •3.1 Экономическая эффективность программного продукта

- •3.2 Составляющие затрат на создание программного продукта

- •3.2.1 Затраты на непосредственную разработку пп

- •3.2.2 Сложность разработки программного продукта

- •3.2.3 Затраты на изготовление опытного образца как продукции производственно-технического назначения

- •3.2.4 Затраты на создание комплекта документации

- •3.2.5 Затраты на технологию и программные средства автоматизации разработки пп

- •3.3 Составляющие затрат на эксплуатацию программ, влияющих на процесс разработки пп

- •3.4 Составляющие затрат на сопровождение программ

- •3.5 Расчет затрат на программный продукт Исходные данные:

- •Затраты на эксплуатацию программ

- •Затраты на эксплуатацию реализующей эвм

- •Затраты на эксплуатацию

- •4.3 Вредные факторы, присутствующие на

- •4.4 Общие требования к помещению машинного зала

- •4.5 Основные требования к освещению

- •4.6 Расчет общего освещения

- •4.7 Меры защиты от поражения электрическим током

- •4.8 Меры по снижению уровня шума

- •4.9 Защита от излучений

- •Нормирование метеорологических условий в машинном зале

- •4.11 Требования по пожарной безопасности

- •4.12 Психофизиологические опасные и вредные производственные факторы

- •4.13 Планировка рабочего места программиста и организация работы с компьютером

- •4.14 Выводы

- •Используемая литература:

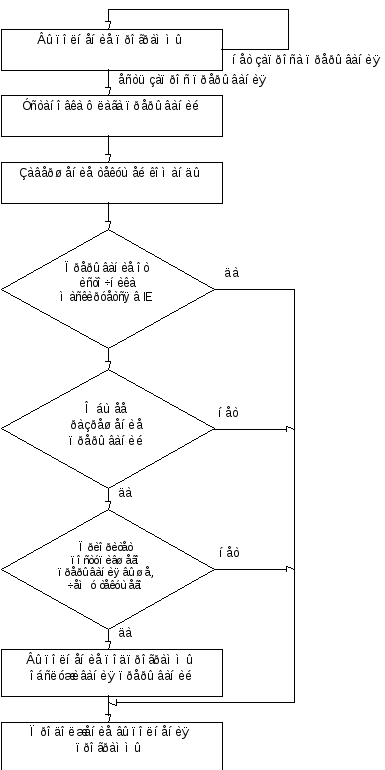

1.7.2.1 Основная программа

В начале основной программы происходит назначение векторов прерываний от линейных интерфейсов и последовательного порта. Далее идут два блока инициализации: области памяти ОЗУ данных с 40Н по 7FН и самих линейных интерфейсов. Команды инициализации последних CR2.RESET формируются в соответствии с таблицей адресов линейных интерфейсов (рис. 1.9) и таблицей адресов внутренних регистров линейных интерфейсов (рис. 1.10).

Рис. 1.8. Реализация системы прерываний для микроконтроллера АТ89С51.

-

Регистр

Bit

7

6

5

4

3

2

1

0

LI1

0

0

0

0

0

0

0

0

00Н

LI2

0

0

0

1

0

0

0

0

10H

LI3

0

0

1

0

0

0

0

0

20Н

LI4

0

0

1

1

0

0

0

0

30H

LI5

0

1

0

0

0

0

0

0

40Н

LI6

0

1

0

1

0

0

0

0

50H

LI7

0

1

1

0

0

0

0

0

60H

LI8

0

1

1

1

0

0

0

0

70H

LI9

1

0

0

0

0

0

0

0

80H

LI10

1

0

0

1

0

0

0

0

90H

LI11

1

0

1

0

0

0

0

0

A0H

LI12

1

0

1

1

0

0

0

0

В0Н

LI13

1

1

0

0

0

0

0

0

C0H

LI14

1

1

0

1

0

0

0

0

D0Н

LI15

1

1

1

0

0

0

0

0

E0H

LI16

1

1

1

1

0

0

0

0

F0H

Рис. 1.9. Адреса линейных интерфейсов.

|

Регистр |

Bit |

| |||||||

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

CR1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

00H |

|

CR2 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

02H |

|

CR3 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

04H |

|

CR4 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0EH |

|

ICR |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

06H |

|

TSR |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

08H |

|

PSR |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0AH |

|

ESR |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0CH |

Рис. 1.10. Адреса внутренних регистров линейных интерфейсов.

Затем производится запись в ОЗУ данных состояний части битов внутренних регистров линейных интерфейсов. Данные располагаются в заранее оговоренной техническим заданием области памяти 40Н – 7FН в заданном порядке. Распределение памяти ОЗУ данных процессора показано на рисунке 1.11. Нужные биты выбираются из внутренних регистров линейных интерфейсов, таблица которых приведены на рисунке 1.12. Например, для занесения бита AIS в 1-й бит ячейки памяти 40Н, его нужно считать из 2-го бита регистра PSR LI1. Порядок сохраняется для всей карты по возрастанию следующий: PSR, TSR, CR2, CR1.

|

Линейный интер- фейс |

Адрес регистра в ОЗУ |

Bit | |||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 | ||

|

L1 1 |

40 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

41 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

42 Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

43 Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 2 |

44 H |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

45 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

46 Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

47 Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 3 |

48 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

49 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

4A Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

4B Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 4 |

4C Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

4D Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

4E Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

4F Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 5 |

50 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

51 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

52 Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

53 Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 6 |

54 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

55 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

56 Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

57 Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 7 |

58 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

59 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

5A Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

5B Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 8 |

5C Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

5D Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

5E Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

5F Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 9 |

60 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

61 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

62 Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

63 Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 10 |

64 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

65 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

66 Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

67 Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 11 |

68 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

69 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

6A Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

6B Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 12 |

6C Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

6D Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

6E Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

6F Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 13 |

70 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

71 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

72 Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

73 Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 14 |

74 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

75 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

76 Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

77 Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 15 |

78 Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

79 Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

7A Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

7B Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

|

L1 16 |

7C Н |

|

|

|

|

|

DFMO |

AIS |

LOS |

|

|

7D Н |

FL |

|

TQRSS |

ESOVR |

ESUNF |

TDFMO |

TAIS |

TLOS |

|

|

7E Н |

ЕРАТ1 |

EPAT0 |

ETAOS |

EQZMON |

ERLOOP |

ELLOOP |

|

EALOOP |

|

|

7F Н |

|

|

|

|

ES4 |

ES3 |

ES2 |

ES1 |

Рис. 1.11. Распределение памяти ОЗУ данных процессора.

|

Register |

Tуре |

Bit | ||||||||

|

Name |

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 | |

|

Control #1 |

CR1 |

R/W |

JASEL1 |

JASEL0 |

ENCEB |

UNIENB |

EC4 |

ЕС3 |

EC2 |

EC1 |

|

Control #2 |

CR2 |

R/W |

RESET |

ЕРАT1 |

EPAT0 |

ETAOS |

ENLOOP |

EALOOP |

ELLOOP |

ERLOOP |

|

Control #3 |

CR3 |

R/W |

JA6HZ |

PCLKE1 |

SBIST |

EQZMON |

reserved2 |

ES64 |

ESCEN |

ESJAM |

|

Interrupt Clear |

ICR |

R/W |

CESU |

CESO |

CDFMO |

reserved3 |

CQRSS |

CAIS |

CNLOOP |

CLOS |

|

Transition Status |

TSR |

R |

ESUNF |

ESOVR |

TDFMO |

reserved2 |

TQRSS |

TAIS |

TNLOOP |

TLOS |

|

Performance Status |

PSR |

R |

reserved2 |

BIST |

DFMO |

reserved2 |

QRSS |

AIS |

NLOOP |

LOS |

|

Equalizer Status |

ESR |

R |

LATN7 |

LATN6 |

LATN5 |

LATN4 |

reserved2 |

Reserved2 |

reserved2 |

reserved2 |

|

Control #4 |

CR4 |

R/W |

reserved2 |

reserved2 |

Reserved2 |

reserved2 |

COL32CM |

LOS2048 |

ZEROV |

CODEV |

| ||||||||||

Рис. 1.12. Таблица бит внутренних регистров линейных интерфейсов для заполнения карты памяти.

Потом инициализируется последовательный порт Р3 на прием. Инициализируется таймер, выбор 1-го таймера, перевод его в третий режим работы, загрузка константы скорости в таймер для 9600 Бод, разрешение работы таймера. Инициализация последовательного порта проходит следующим образом: порт устанавливается в режим 9-бит с программируемой скоростью, устанавливается адрес для записи принятых значений, выбирается номера канала, идет разрешение приёма сообщений с взведённым 9-м битом, разрешение работы приёмопередатчика, разрешение прерываний от приёмопередатчика, общее разрешение прерываний, сброс бита разрешения приёма. После этого выполняется основной цикл программы: ожидание прерывания либо от любого из линейных интерфейсов с переходом на подпрограмму перезаписи карты памяти части битов внутренних регистров линейных интерфейсов, либо от последовательного порта с переходом на подпрограмму связи с внешней ПЭВМ через последовательный порт.