- •М.А. Амелина

- •Список сокращений

- •Логические основы цифровых устройств

- •Общие сведения о цифровых устройствах

- •Алгебра логики

- •Коды и системы счисления

- •Компьютерные форматы данных

- •Элементы цифровых устройств

- •Комбинационные и последовательностные устройства

- •Шифраторы, дешифраторы, преобразователи кодов

- •Мультиплексоры и демультиплексоры

- •Компараторы кодов

- •Двоичные полусумматор и сумматор

- •Арифметико-логические устройства

- •Триггеры

- •Взаимные преобразования триггеров

- •Счетчики

- •Основные параметры и классификация счетчиков

- •Двоичные счетчики

- •Двоично-кодированные счетчики

- •Счетчики с недвоичным кодированием состояний

- •Регистры и регистровые файлы

- •Параллельные регистры

- •Регистровые файлы

- •Сдвигающие регистры

- •Универсальные регистры

- •Аббревиатуры цифровых сигналов, используемые в моделях последовательностных цифровых устройств программы Micro-cap

- •Запоминающие устройства

- •Синтез цифровых автоматов

- •Синтез асинхронных автоматов на rs-триггерах

- •Пример 1

- •Пример 2

- •Пример 3 — Автомат Мили

- •Пример 4 — автомат Мура

- •Синтез асинхронных автоматов на мультиплексорах

- •Пример 1. Асинхронный автомат Мили

- •Пример 2. Асинхронный автомат Мура

- •Синтез синхронных автоматов

- •Пример 3. Синтез счетчика с изменяемым коэффициентом пересчёта

- •Литература

Регистры и регистровые файлы

Регистры — самые распространенные узлы цифровых устройств. Они оперируют с множеством связанных переменных, составляющих слово. Над словами выполняется ряд операций: прием, выдача, хранение, сдвиг в разрядной сетке, поразрядные логические операции.

Регистры состоят из разрядных схем, в которых имеются триггеры и, чаще всего, также и логические элементы.

По количеству

линий передачи переменных регистры

делятся на однофазные и парафазные, по

системе синхронизации — на однотактные,

двухтактные и многотактные. Впарафазныхрегистрах информация записывается и

считывается и в прямом (Q),

и в обратном (![]() )

кодах. Воднофазныхрегистрах

информация записывается и считывается

либо в прямом (Q), либо в

обратном (

)

кодах. Воднофазныхрегистрах

информация записывается и считывается

либо в прямом (Q), либо в

обратном (![]() )

коде.

)

коде.

Однако главным классификационным признаком является способ приема и выдачи данных. По этому признаку различают параллельные (статические) регистры, последовательные (сдвигающие) и параллельно-последовательные.

В параллельныхрегистрах прием и выдача слов производятся по всем разрядам одновременно. В них хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям.

В последовательныхрегистрах слова принимаются и выдаются разряд за разрядом. Их называют сдвигающими, т. к. тактирующие сигналы при вводе и выводе слов перемещают их в разрядной сетке. Сдвигающий регистр может быть нереверсивным (с однонаправленным сдвигом) или реверсивным (с возможностью сдвига в обоих направлениях).

Последовательно-параллельныерегистры имеют входы-выходы одновременно последовательного и параллельного типа. Имеются варианты с последовательным входом и параллельным выходом (SIPO, Serial Input — Parallel Output), параллельным входом и последовательным выходом (PISO), а также варианты с возможностью любого сочетания способов приема и выдачи слов.

Параллельные регистры

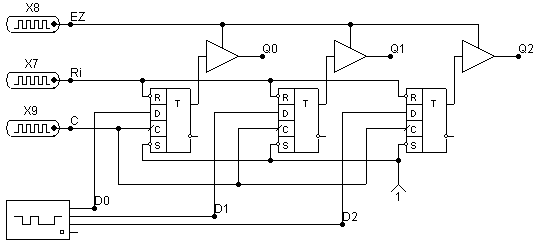

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения вывода или приема, т. е. цепи управления. Пример схемы статического регистра, построенного на триггерах типа Dс прямыми динамическими входами, имеющего входы сброса R и выходы с третьим состоянием, управляемые сигналом EZ, показан на рис. 2.64.

Для современной схемотехники характерно построение регистров именно на D-триггерах, преимущественно с динамическим управлением. Многие имеют выходы с третьим состоянием, некоторые регистры относятся к числу буферных, т. е. рассчитаны на работу с большими емкостными и/или низ-коомными активными нагрузками. Это обеспечивает их работу непосредственно на магистраль (без дополнительных схем интерфейса).

а

б

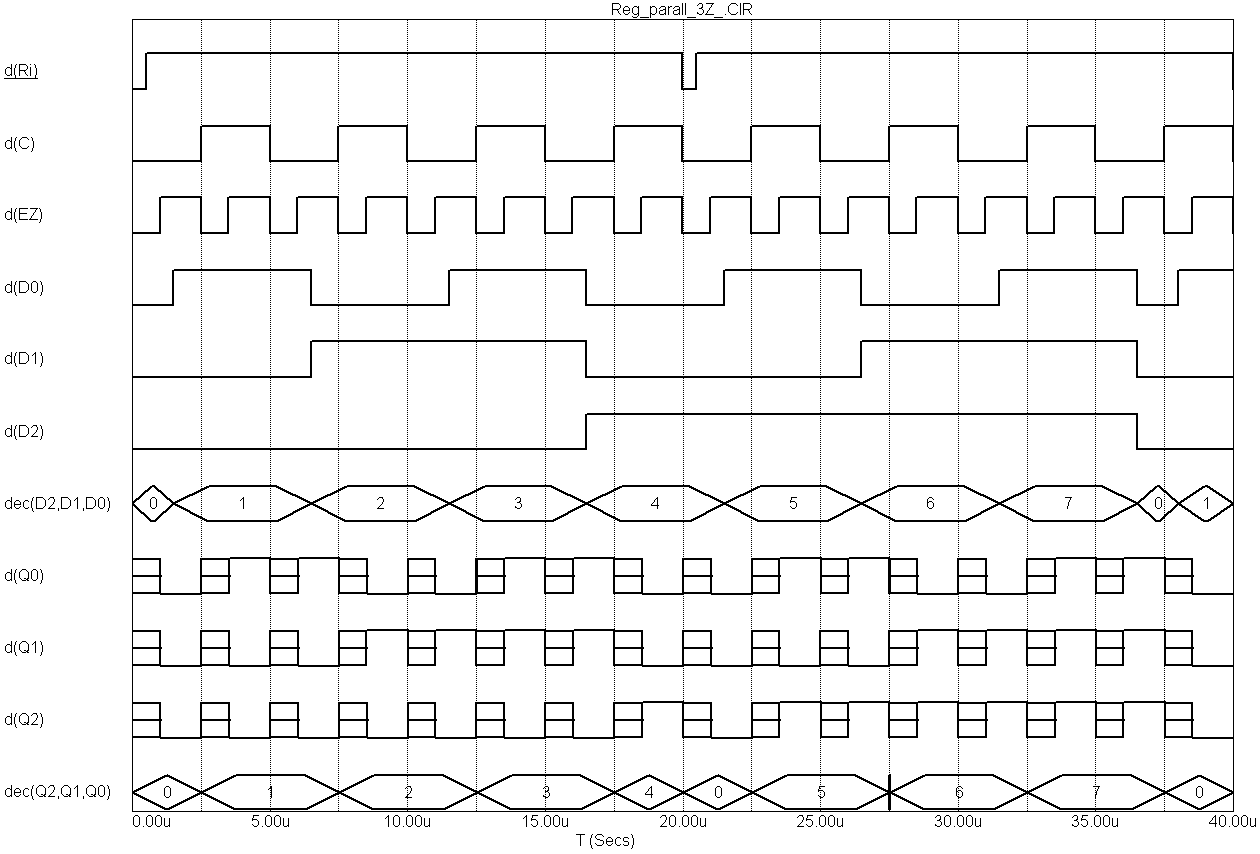

Рисунок 2.64 — Параллельный регистр с 3-мя состояниями выходов, тактируемый фронтом: а — схема; б — временные диаграммы

Подобную структуру (см. рис. 2.64) имеет параллельный регистр с 3-мя состояниями выхода КР1533ИР38 (74ALS874B), за исключением того, что выходы разрешаются низким уровнем (а не высоким как на рис. 2.64).

Регистровые файлы

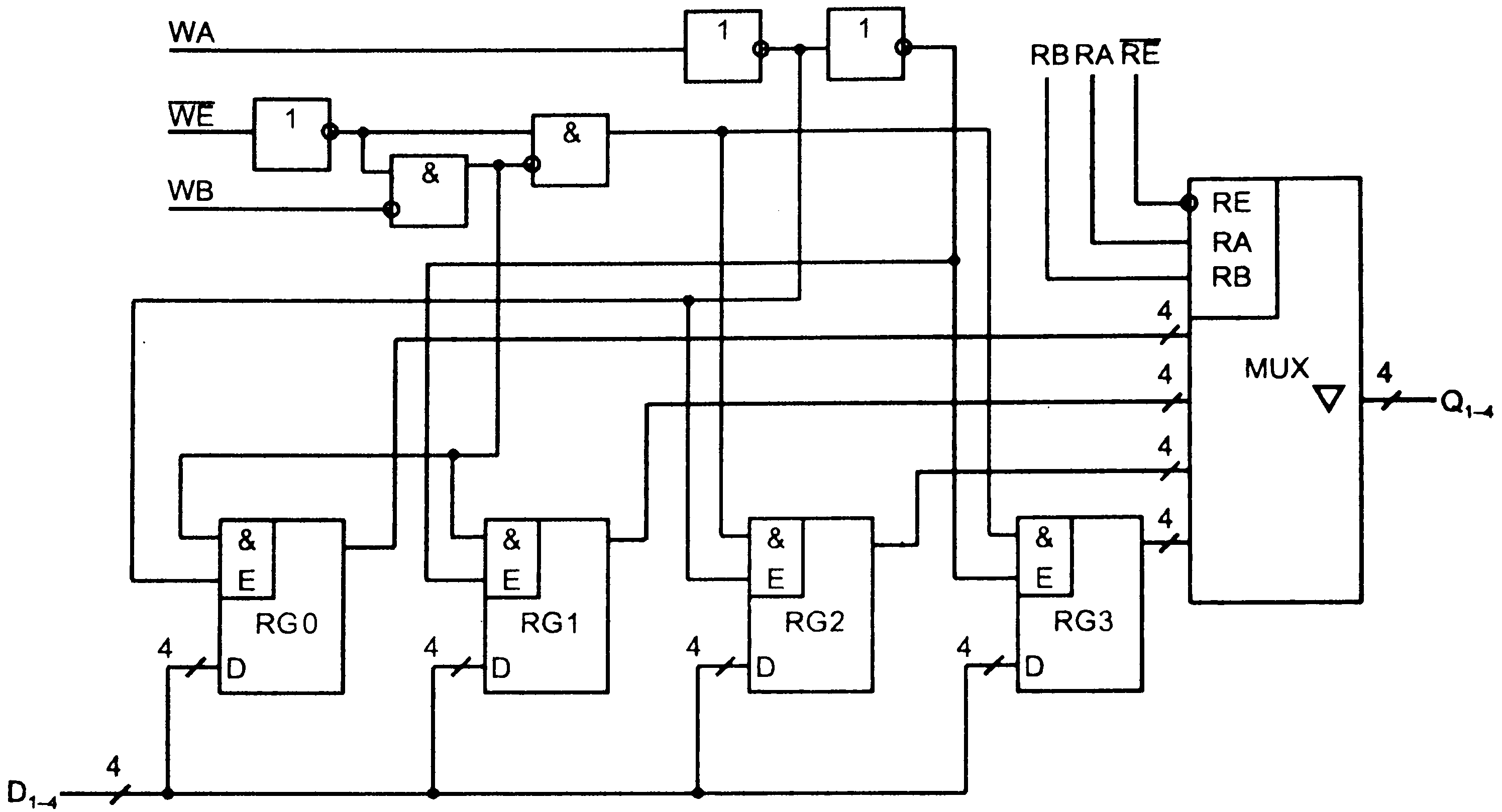

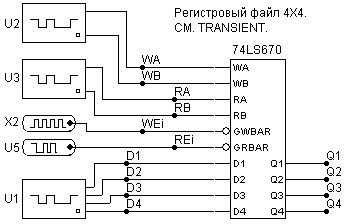

Из статических регистров составляются блоки регистровой памяти — регистровые файлы. В микросхеме типа ИР26 (серии КР1533, К555 и др., зарубежный аналог 74LS670) можно хранить 4 четырехразрядных слова с возможностью независимой и одновременной записи одного слова и чтения другого. Информационные входы регистров соединены параллельно (рис. 2.65, а). Входы адресов записи WA и WB (от Write) дают четыре комбинации, каждая из которых разрешает «защелкнуть» данные, присутствующие в настоящее время на выводахD1…D4. Содержимое файла (регистра) вызывается на выходы блока Q1…Q4 с помощью дешифратора считывания (адресных входов мультиплексора) адресами RA и RB (от английского Read). Таких адресов также четыре.

а б

в

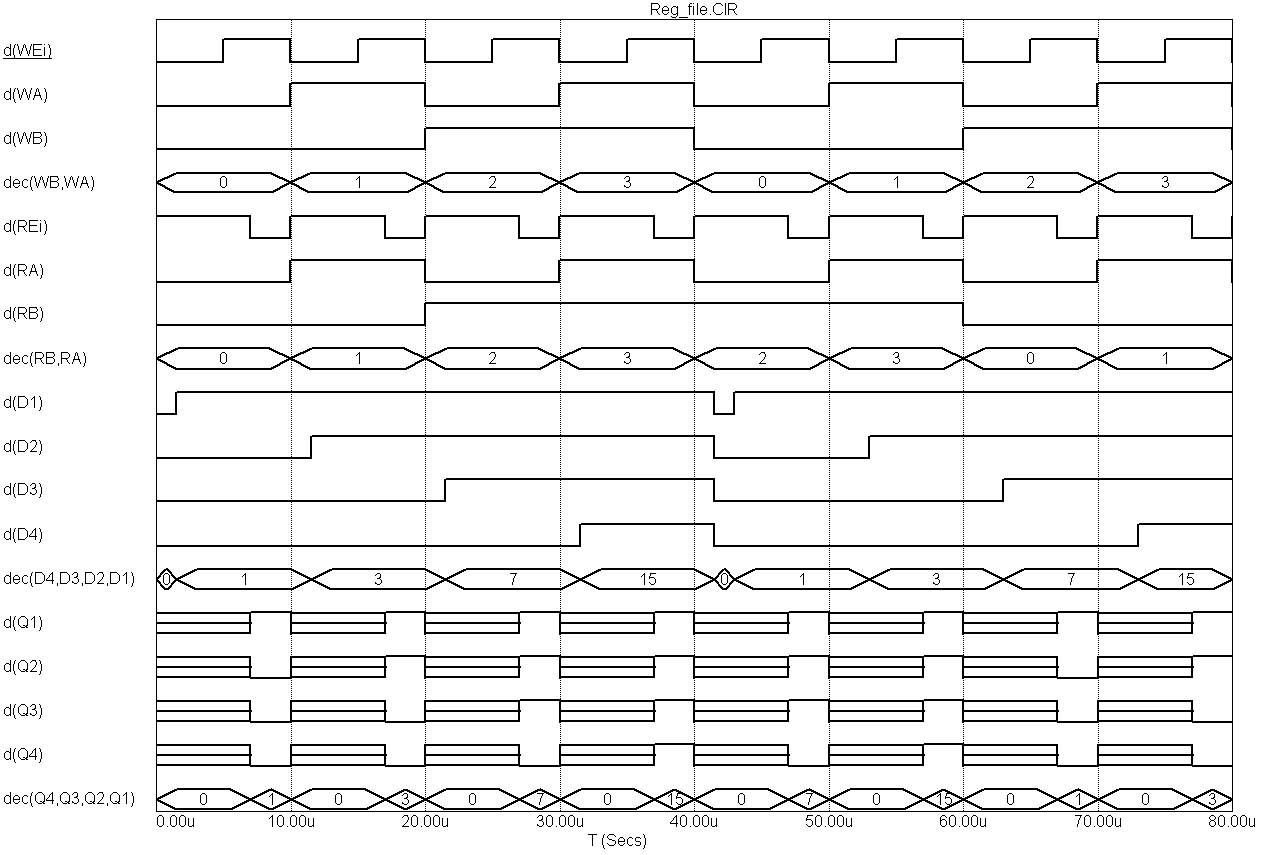

Рисунок 2.65 — Регистровый файл КР1533ИР26: а — внутренняя структура; б — схема для моделирования в среде Micro-CAP; в — временные диаграммы моделирования

Если на входе разрешения записи WE (Write Enable) действует активный низкий уровень, то данные поступают в соответствующий регистр, при высоком уровне WE входы для данных и адресов запрещены. Выходные данные выдаются в прямом коде. Внутренние D-триггеры регистрового файла представляют собой защелкиLatch(т.е. информация записывается в них по высокому уровню синхросигнала, а по отрицательному фронту синхроимпульса — защелкивается).

Размерность регистровой памяти можно наращивать, составляя из нескольких ИС блок памяти. При наращивании числа хранимых слов выходы отдельных ИС с тремя состояниями соединяются в одной точке. Допускается соединять непосредственно до 128 выходов, что дает 512 хранимых слов. Ограничение на число соединяемых в одной точке выходов вызвано токовым режимом выхода, оно может быть преодолено при подключении к выходной точке специальных внешних резисторов. При наращивании разрядности слова соединяют параллельно входы разрешения и адресации нескольких ИС, выходы которых в совокупности дают единое информационное слово.