- •М.А. Амелина

- •Список сокращений

- •Логические основы цифровых устройств

- •Общие сведения о цифровых устройствах

- •Алгебра логики

- •Коды и системы счисления

- •Компьютерные форматы данных

- •Элементы цифровых устройств

- •Комбинационные и последовательностные устройства

- •Шифраторы, дешифраторы, преобразователи кодов

- •Мультиплексоры и демультиплексоры

- •Компараторы кодов

- •Двоичные полусумматор и сумматор

- •Арифметико-логические устройства

- •Триггеры

- •Взаимные преобразования триггеров

- •Счетчики

- •Основные параметры и классификация счетчиков

- •Двоичные счетчики

- •Двоично-кодированные счетчики

- •Счетчики с недвоичным кодированием состояний

- •Регистры и регистровые файлы

- •Параллельные регистры

- •Регистровые файлы

- •Сдвигающие регистры

- •Универсальные регистры

- •Аббревиатуры цифровых сигналов, используемые в моделях последовательностных цифровых устройств программы Micro-cap

- •Запоминающие устройства

- •Синтез цифровых автоматов

- •Синтез асинхронных автоматов на rs-триггерах

- •Пример 1

- •Пример 2

- •Пример 3 — Автомат Мили

- •Пример 4 — автомат Мура

- •Синтез асинхронных автоматов на мультиплексорах

- •Пример 1. Асинхронный автомат Мили

- •Пример 2. Асинхронный автомат Мура

- •Синтез синхронных автоматов

- •Пример 3. Синтез счетчика с изменяемым коэффициентом пересчёта

- •Литература

Арифметико-логические устройства

Арифметико-логическое устройство (АЛУ) — часть центрального процессора, которая в общем случае формирует функции двух входных переменных и порождает одну выходную переменную. Эти функции обычно состоят из простых арифметических операций, простых логических операций и операций сдвига.

Вне зависимости от того, насколько широк круг операций, реализуемых современными АЛУ, главными среди них остаются операции арифметического сложения и умножения, продолжительность выполнения которых указывается в качестве основных характеристик вычислительного устройства. Простейшие операции: арифметическое сложение (вычитание), логическое умножение, логическое сложение, сумма по модулю два, инверсия, сдвиг влево, сдвиг вправо, инкремент (положительное приращение), декремент (отрицательное приращение) выполняются в АЛУ с помощью только аппаратных средств (схем на логических элементах). Операция умножения (деления), как правило, выполняется программным способом (с применением последовательного исполнения нескольких операций сложения и сдвига, выполненных аппаратным способом). Однако, как будет показано далее, существуют и аппаратные умножители.

АЛУ классифицируют по различным признакам.

По способу действиянад операндами АЛУ подразделяют на

АЛУ параллельного действия

АЛУ последовательного действия.

По способу представления чиселразличают:

АЛУ для чисел с фиксированной запятой

АЛУ для чисел с плавающей запятой

АЛУ для десятичных чисел.

По способу организации работы:

синхронные АЛУ

асинхронные АЛУ

По характеру используемых элементови узлов:

Универсальные, в которых операции для всех форм представления чисел выполняются одними и теми же схемами,

Функциональные, в которых операции над операндами с фиксированной и плавающей запятой, с десятичными переменными и логическими переменными осуществляются в отдельных операционных блоках.

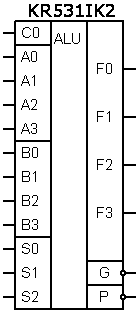

В настоящее время практически все АЛУ выполняются в интегральном исполнении и выпускаются различные серии соответствующих ИС. Проиллюстрируем функциональные возможности таких схем на примере ИС К531ИК2 (74LS381). Ее условное обозначение приведено на рис. 2.21.

Данная схема оперирует с двумя 4-разрядными входными кодами и способна выполнять 3 логических (поразрядные И, ИЛИ, исключающее ИЛИ) и 3 арифметических (сложение, вычитания (A-B), (B-A)) операций. Тип выполняемой операции определяется кодовой комбинацией на входахS2,S1,S0 (Табл. 2.5). ВходC0 представляет собой перенос из предыдущего разряда при сложении, инверсный заем из следующего разряда при вычитании. ВыходыP,Gпредставляют собой инверсные биты переноса для каскадирования и переполнения соответственно (схемаMicro-CAP381.cir).

Т

Рисунок 2.21

-

S2

S1

S0

Операция

0

0

1

B – A

0

1

0

A – B

0

1

1

A + B

1

0

0

A XOR B

1

0

1

A OR B

1

1

0

A AND B

1

1

1

PRESET

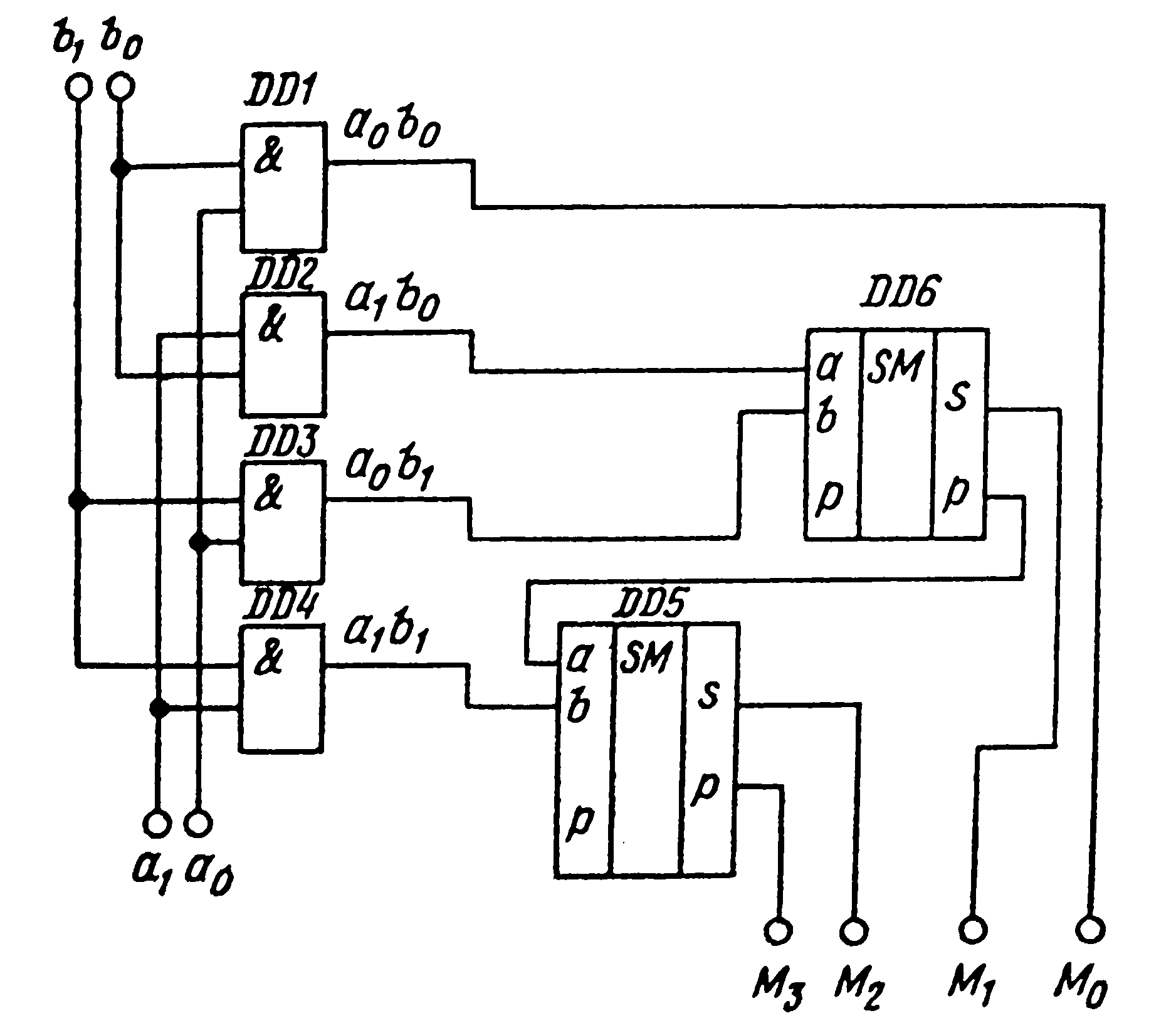

Логика построения аппаратных умножителейнеразрывно связана с традиционным алгоритмом выполнения операции умножения, базирующемся на суммировании частных произведений разрядов сомножителей. Проиллюстрируем сказанное на примере умножения 2-разрядных двоичных кодов:

a1 a0

X b1 b0

__________________________

b0a1 b0a0

+ b1a1 b1a0

__________________________

M3 M2 M1 M0

Структурная схема устройств показана на рис. 2.22. Частные произведения разрядов сомножителей формируются ЛЭ 2И — DD1…DD4. Суммируя эти произведения сумматорами DD5 и DD6 находят значение кода результата. Приведенная структура носит название матричного множительного блока.

Рисунок 2.22 — Основная ячейка матричного множительного блока

Используя аналогичный подход, можно синтезировать матричный множительный блок, работающий с входными кодами произвольной разрядности.

При разработке ИС желательно использовать структуру, позволяющую увеличивать разрядность входных кодов путем использования нескольких однотипных схем. Устройство, приведенное на рис. 20.22, этому требованию не удовлетворяет. Для нахождения структурной схемы умножителя, удовлетворяющей указанному требованию, рассмотрим алгоритм умножения двух 4-разрядных кодов:

|

|

|

|

|

a3 |

a2 |

a1 |

a0 | |

|

|

|

|

|

X |

b3 |

b2 |

b1 |

b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b0a3 |

b0a2 |

b0a1 |

b0a0 |

|

|

|

|

|

b1a3 |

b1a2 |

b1a1 |

b1a0 |

|

|

+ |

|

|

b2a3 |

b2a2 |

b2a1 |

b2a0 |

|

|

|

|

|

b3a3 |

b3a2 |

b3a1 |

b3a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M7 |

M6 |

M5 |

M4 |

M3 |

M2 |

M1 |

M0 |

Очевидно, что приведенный алгоритм можно представить в виде комбинации четырех однотипных блоков (выделены линией), соответствующих рассмотренному выше умножению 2-разрядных кодов. Однако для такого представления, кроме получения частного произведения, каждый из выделенных блоков должен выполнять дополнительные операции сложения.

Реализация умножения многоразрядных чисел на основе однотипных блоков требует введения в схему основной ячейки рис. 2.22 двух дополнительных сумматоров [11].