- •М.А. Амелина

- •Список сокращений

- •Логические основы цифровых устройств

- •Общие сведения о цифровых устройствах

- •Алгебра логики

- •Коды и системы счисления

- •Компьютерные форматы данных

- •Элементы цифровых устройств

- •Комбинационные и последовательностные устройства

- •Шифраторы, дешифраторы, преобразователи кодов

- •Мультиплексоры и демультиплексоры

- •Компараторы кодов

- •Двоичные полусумматор и сумматор

- •Арифметико-логические устройства

- •Триггеры

- •Взаимные преобразования триггеров

- •Счетчики

- •Основные параметры и классификация счетчиков

- •Двоичные счетчики

- •Двоично-кодированные счетчики

- •Счетчики с недвоичным кодированием состояний

- •Регистры и регистровые файлы

- •Параллельные регистры

- •Регистровые файлы

- •Сдвигающие регистры

- •Универсальные регистры

- •Аббревиатуры цифровых сигналов, используемые в моделях последовательностных цифровых устройств программы Micro-cap

- •Запоминающие устройства

- •Синтез цифровых автоматов

- •Синтез асинхронных автоматов на rs-триггерах

- •Пример 1

- •Пример 2

- •Пример 3 — Автомат Мили

- •Пример 4 — автомат Мура

- •Синтез асинхронных автоматов на мультиплексорах

- •Пример 1. Асинхронный автомат Мили

- •Пример 2. Асинхронный автомат Мура

- •Синтез синхронных автоматов

- •Пример 3. Синтез счетчика с изменяемым коэффициентом пересчёта

- •Литература

Компараторы кодов

<Цифровой ><компаратор><предназначен><для><определения><равенства><двоичных><чисел.><Опе><рация><поразрядного><сравнения><заключается><в><выработке><признака><равенства><(равно><значности)><или><неравенства><(неравнозначности)><двух><сравниваемых><двоичных><чисел.><Два><числа><равны><при><равенстве><цифр><в><одноименных><разрядах:><ai><=><bi,><><><где><аi><—><цифра><в><i-ом><разряде><одного><числа;><b><i><><—><цифра><в><i-ом><разряде><другого><числа.><Равенство><ai><=b><i,><имеет><место><при><аi><=><1,><bi><=><1><или><при><аi><=><0,><bi><=><0.><Поэтому><логическая><функция,><выражающая><это><равенство,><равна><единице,><если><единице><равно><произведение><этих><цифр><или><произведение><их><инверсных><значений,><т.><е.:>

![]() ,<><>

,<><>

<а><логическая><функция,><описывающая><компаратор равенства,><имеет><вид:>

![]() <><>

<><>

<Для><построения><компаратора равенства><только><на><элементах><И-НЕ,><запишем><её><в><другой><форме,><воспользовавшись><формулами><де><Моргана:>

![]()

<><><><><><Схема,><реализующая><это><выражение,><приведена><на><рис.>2.13.

Рисунок 2.13 — Схема компаратора 2-х n-разрядных кодов на совпадение в базисе И-НЕ

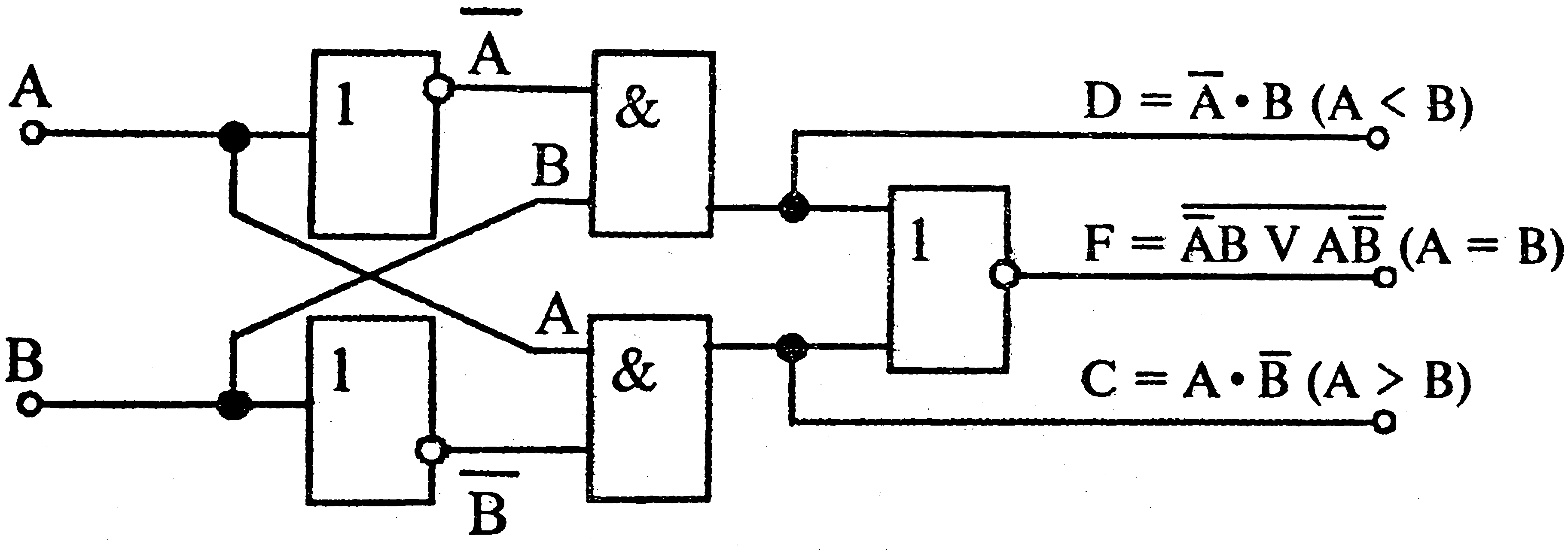

Помимо совпадения кодов реальные ИМС цифровых компараторов <><могут ><определять и ><><><><><><><><><><><><><><вид их ><неравенства ><А>В ><или ><А<В. Т.е. реальные ИС ><><компараторов ><имеют ><три >выхода. Схема такого одноразрядного компаратора приведена на рис. 2.14.

Рисунок 2.14 — Одноразрядный компаратор с определением равенства и вида неравенства

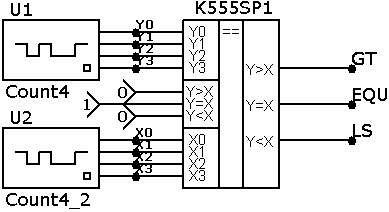

<Цифровые><компараторы><выпускают,><как><правило,><в><виде><самостоятельных><микросхем.><Так, например, имеется ТТЛШ><микросхема К555СП1<(рис.>2.15) и КМОП><К564ИП2, которые являются 4-хразрядными компараторами с определением типа неравенства и возможностью наращивания разрядности.>

Рисунок 2.15 — Включение микросхемы компаратора 4-хразрядных кодов К555СП1

<Если><используется><одна><микросхема,><то><на><ее><вход><Y=X><следует ><подать ><логическую ><1><><><><><><><><><><.>

Двоичные полусумматор и сумматор

<Сумматор><—><это устройство><,><в><котором><выполняется><арифметическая><операция><суммирования><цифровых><кодов><двух><двоичных><чисел.><Известно,><что><числа><в><любой><позиционной><си><стеме><счисления><складываются><поразрядно.><Поэтому><для><сложения><двух><чисел><нужно><иметь><типовые><узлы,><реализующие><суммирование><цифр><одного><разряда><слагаемых><с><учетом><возможного><переноса><единицы><из><соседнего><младшего><разряда.><К><таким><узлам><относят><одноразрядные><комбинационные><полусумматоры><и><сумматоры.>

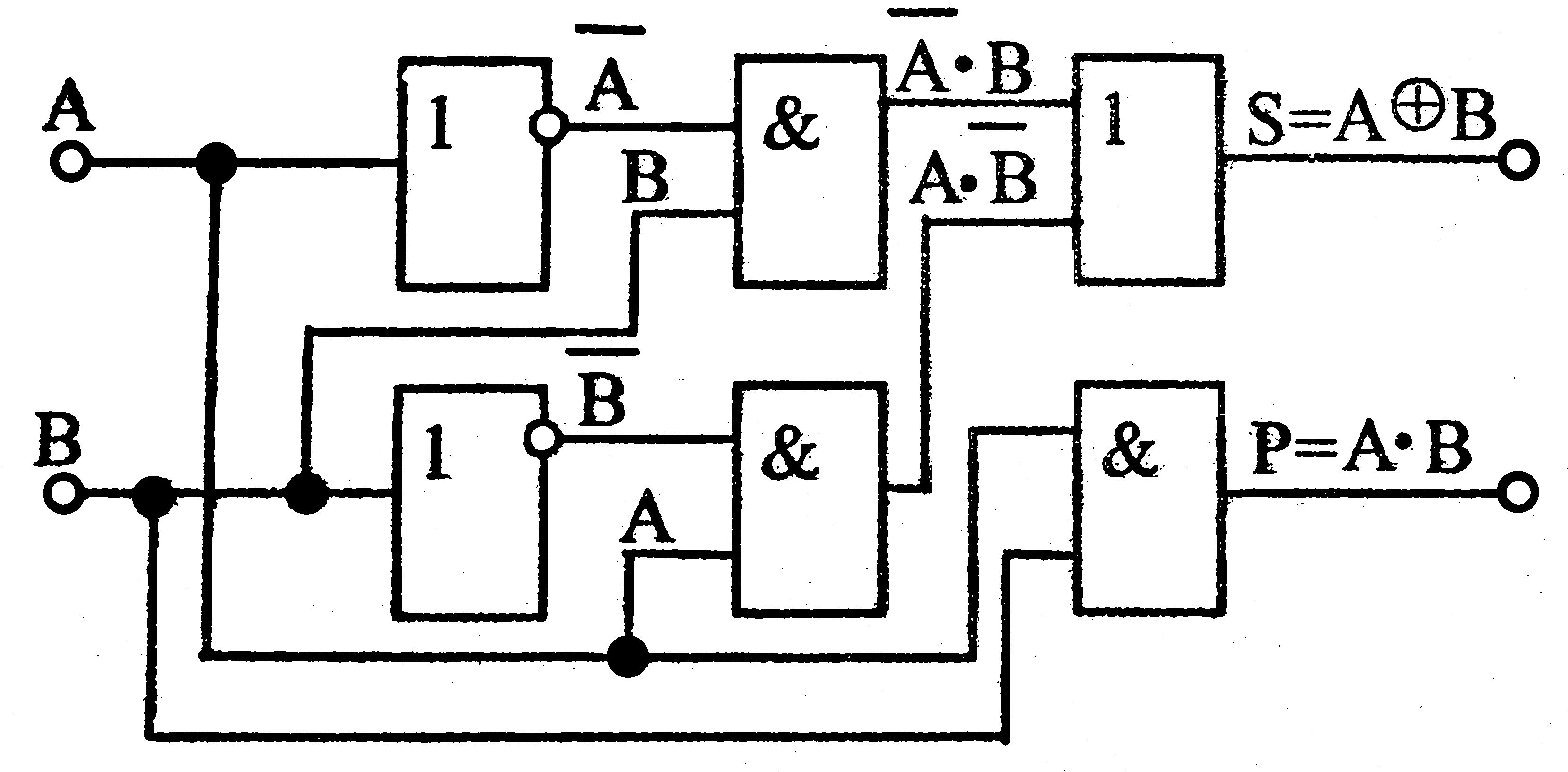

<Полусумматор><предназначен><для><суммирования><двух><одноразрядных><двоичных><чисел.><Он><имеет><два><входа><—><аi><и><bi><и><два><выхода><—><S><i><><иPi+1,><где><S><i><><—><выход><суммы,><а><Pi+1

><является><выходом><переноса><(табл.><2.><3).><Логические><функции><для![]() ><><и

><><и![]() ><><и><функциональную><схему><(рис.><2.16><)><этого><узла><легко><построить><на><ос><нове><таблицы><истинности><(таблица><2.3),><используя><элементы><И,><ИЛИ><и><НЕ.>

><><и><функциональную><схему><(рис.><2.16><)><этого><узла><легко><построить><на><ос><нове><таблицы><истинности><(таблица><2.3),><используя><элементы><И,><ИЛИ><и><НЕ.>

Таблица 2.3 — Таблица истинности одноразрядного полусумматора

|

аi |

bi |

Pi+1 |

<S>i<> |

|

<0> |

<0> |

<0> |

<0> |

|

<0> |

<1> |

<0> |

<1> |

|

<1> |

<0> |

<0> |

<1> |

|

<1> |

<1> |

<1> |

<0> |

Рисунок 2.16 — Схема одноразрядного полусумматора

<При><построении><сумматоров><на><интегральных><микросхемах><для><обеспечения><быс><тродействия><и><минимального><количества><однотипных><логических><элементов><необхо><димо><уменьшить><число><последовательно><включенных><элементов.><Анализ><показал,><что><более><экономичной><по><количеству><элементов><и><быстродействующей><является><функ><циональная><схема><полусумматора,><реализующая><переключательную><функцию:>

![]() ,

,

![]()

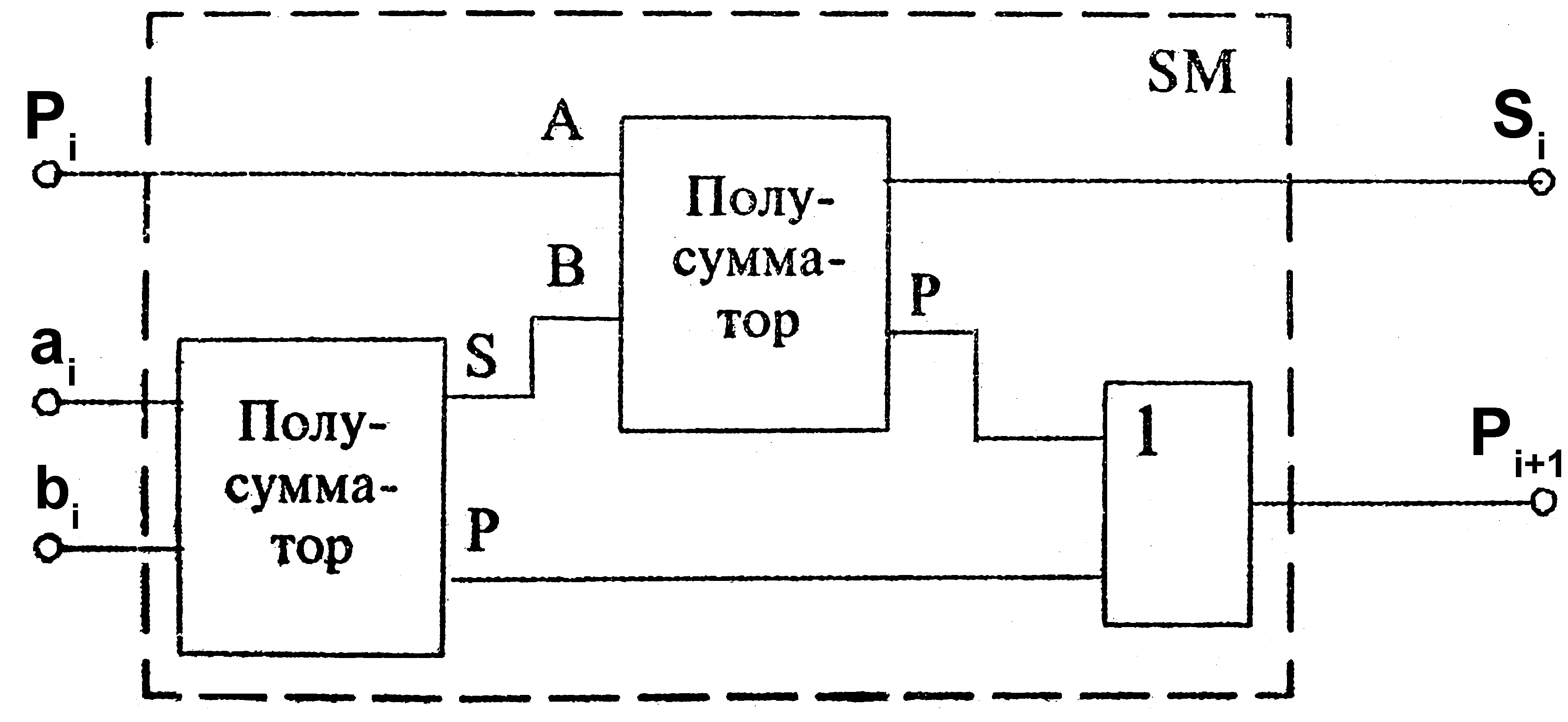

<При><суммировании><двух><многоразрядных><чисел><для><каждого><разряда><(кроме><младшего)><необходимо><использо><вать><устройство,><имеющее><дополнительный><вход><перено><са (из предыдущего более младшего разряда, вспомните правило сложения в столбик).><Такое><устройство><(рис.><2.17)><называют><полным ><сумма><тором><и><его><можно><представить><как><объединение>двух<полусумматоров><(Р><вх><><—><дополнительный><вход><переноса).><Сумматор><обозначают><через>SM.

<В><универсальных><АЛУ,><входящих><в><состав><цифровых><устройств,><одноразрядные><сумматоры><проектируют><из><двух><полусумматоров,><объединенных><в><один><выход><><><S(рис. 2.17).>

Рисунок 2.17 — Одноразрядный полный сумматор на основе двух полусумматоров

<Мно><горазрядные><комбинационные><сумматоры><последовательного><или><параллельного><дей><ствия><строятся><на><основе><одноразрядных><комбинационных><сумматоров,><реализующих><функции для каждого разряда:>

![]() ,

,

![]()

<По><этим><функциям можно построить><><сумматор и><на><элементах><И-НЕ><или>ИЛИ-НЕ.

<Соединяя><определенным><образом><полусумматоры><и><полные><сумматоры><друг><с><другом,><получают><устройство><для><выполнения><сложения><нескольких><разрядов><двоичных><чи><сел.><В><качестве><примера><рассмотрим><устройство><для><сложе><ния><двух><трехразрядных><двоичных><чисел><А><2>< ><А1, ><А0><и><В><2>< ><В1, ><В0><><,><где><A0 ><и><В><0><><—><младшие><разряды><двоичных><чисел><(рис.><2.18).>

<На ><выходах <S>2…><S0 ><>< ><формируется ><код ><суммы ><чисел ><А><2>< ><А><1>< ><A0 ><и ><В><2>< ><В1 ><В><0><, ><а ><на ><выходе ><Р><3>< ><— ><сигнал ><переноса ><в ><следующую ><микросхему, ><так ><как ><при ><сложении ><двух ><трехразрядных ><дво><ичных ><чисел ><может ><получиться ><четырехразрядное ><число.>

<Следует><отметить,><что><в><рассмотренной структуре><><><для><суммирования><в><каждом><разряде><исполь><зуется><отдельный><сумматор,><но><перенос><из><разряда><в><раз><ряд><осуществляется><последовательно,><что><и><определяет><время><выполнения><суммирования><><><><><><>.<Рассмотренный><сумматор><называется><параллельным ><сумматором c последовательным переносом(К155ИМ3).>

Рисунок 2.18 — Параллельный 3-хразрядный сумматор с последовательным переносом

<Для><повышения><быстродействия><сумматоров><необходи><мо><уменьшить><время><переноса,><что><достигается><использо><ванием><вместо><последовательного><параллельного><переноса. В этом случае в каждом разряде как сигнал суммы, так и сигнал переноса непосредственно формируются из входных переменных.><Так><микросхема><К555ИМ6 (74LS283)><представляет><собой><четырех><разрядный><сумматор><с><параллельным><переносом.>

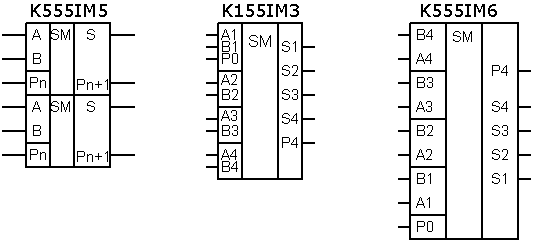

<В><виде><интегральных><микросхем><выпускаются><однораз><рядные,><двухразрядные><и><четырехразрядные><двоичные><сумматоры (рис. 2.19).>

Рисунок 2.19 — Двоичные сумматоры

<Рассмотренные><сумматоры><могут><использоваться><для><вычитания><двоичных><чисел.><В><этом><случае><операция><вы><читания><заменяется><сложением><уменьшаемого><с><вычита><емым,><представленным><в><дополнительном><коде,><т.><е.><опе><рацией:>

<Апр– Впр = Апр+ Bдоп = Апр+Bобр+1.><><><><><><><><><><><><><><><><><><><><><><><><><>

<где><А={A3A2A1A0}<><><><><><><><><><><,>< >><и><В={B3B2B1B0}><—><многоразрядные><двоичные><числа, здесь для примера><,><четырехразрядные.>

![]() ,

,

![]() <>

<>

<Рассмотрим 2 примера вычитания (10-5) и (5-10).>

<Двоичный><эквивалент+><1010=0><><10102, ><а +><510><=0><01012.>

Числа в дополнительных кодах:

–1010=10доп=10110B, –510=5доп=11011B

<Для><реализации><описанного><алгоритма><вычитаемое><нужно><преобразовать><в дополнительный код (см. выше) и сложить с уменьшаемым:><><><><><><><><><><><><><><><><><><><>

0<><><><1010 00101>

1<1011 10110>

< 00101=510 11011=–510>

<><Четыре><младших><разряда><результата><представляют><со><бой><результат в дополнительном коде><,><т.><е. десятичное число><5 (в первом случае положительное, а во втором — отрицательное)><.>

<Следует><подчеркнуть,><что><если><А><>><В,><т.><е.><результат><—><положительное><число,><то><ответ><формируется><в><прямом><коде>(знаковый разряд равен 0),<при><этом><формируется><1><переноса><в><более><старший><разряд.><При><А><<><В><ответ><формируется><в дополнительном коде><(знаковый разряд равен 1)><><и><1><переноса><в><более><старший><разряд><не><образуется.>

<Принципиально ><возможно ><построение ><функциональных ><схем ><сумматоров, ><рабо><тающих><в><любой><системе><счисления,><отличающейся><от><двоичной.>

Кроме двоичных, в микропроцессорной технике часто используются так называемые двоично-десятичные коды. Они отображают выраженные в виде последовательности двоичных разрядов десятичные числа. Очевидно, что для представления десятичных цифр необходим, как минимум 4-разрядный двоичный код. При этом из 16 возможных его комбинаций используется только 10. Это предполагает разработку большого числа различных двоично-десятичных кодов (см. табл. 1.5).

На практике большое распространение получил класс так называемых взвешенных кодов. В этих кодах каждому разряду двоичного числа присваивается вполне определенный весовой коэффициент (см. табл. 1.5). В табл. 2.4 приведено соответствие десятичных чисел и их двоичных и двоично-десятичных эквивалентов в коде 8-4-2-1. Весовые коэффициенты его двоичных разрядов соответственно равны 8, 4, 2, 1.

Таблица 2.4. Двоичные и двоично-десятичные коды чисел от 0 до 15

|

<<Двоичный >< ><код > x3x2x1x0 |

<Двоично-десятичный код> |

<Десятичное число> |

|

<0><><><><><><><0><><><><><><><0><><><><><><><0> |

<0><0><0><0> |

<0> |

|

<0><><><><><><><0><><><><><><><0><><><><><><><1> |

<0><0><0><1> |

1 |

|

<0><><0><><10> |

<0><0><10> |

2 |

|

<0><><011><><> |

<0><0><11> |

3 |

|

<0><><10><><0> |

<0><10><0> |

4 |

|

<0><><10><><1> |

<0><1><0><1> |

5 |

|

<0><><1><><1><><><><><><><0> |

<0><110> |

6 |

|

<0><><><><><><><111> |

<0><111> |

7 |

|

<10><><0><><0> |

<10><0><0> |

8 |

|

<10><><0><><1> |

<10><0><1> |

9 |

|

<10><><10> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><0><0><0> |

10 |

|

<10><><11> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><0><0><1> |

11 |

|

<110><><0> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><0><10> |

12 |

|

<110><><1> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><0><11> |

13 |

|

<1110> |

<0><0><0><1 ><>< >< >< >< >< >< >< >< ><0><10><0> |

14 |

|

<1><><1><><1><><1> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><10><1> |

<15>> |

Из приведенной таблицы следует, что 4-разрядные двоичные коды с 1010 по 1111 не имеют 4-разрядного двоично-десятичного эквивалента. Так, число 12 в двоично-десятичном коде представляется 8-разрядным упакованным кодом 00010010, а число 16 — кодом 00010110.

Описанная особенность двоично-десятичного кода предполагает использование для суммирования специальных логических схем. Смысл их построения состоит в том, что сначала двоично-десятичные коды суммируются как двоичные. Если результатом суммирования является несуществующий двоично-десятичный код, его необходимо уменьшить на 1010, и дополнительно сформировать сигнал переноса. Уменьшение кода на 1010может выполняться его суммированием с дополнительным кодом числа 10 (в двоичной системе –1010= 101102, т.е. фактически прибавлением 610=1102).

Необходимость выполнения такого суммирования согласно табл. 2.4 после минимизации выражается ФАЛ F=x3(x2 + x1).

Очевидно, что такое же суммирование необходимо выполнять и в случае, если в результате суммирования тетрад (BCD-кодов) получен сигнал переноса в старший разряд. С учетом сказанного, ФАЛ необходимости выполнения дополнительного суммирования имеет вид:

F = x3(x2 + x1)+ P(2.1),

где x3, x2, x1, x0— разряды полученного кода в порядке убывания весов,P— перенос, возникший при сложении текущих тетрадBCD-кодов.

Таким образом, для реализации операции сложения двух двоично-десятичных кодов необходимы два 4-хразрядных сумматора и логическая схема, обеспечивающая формирование выходного сигнала в соответствие с ФАЛ (2.1).

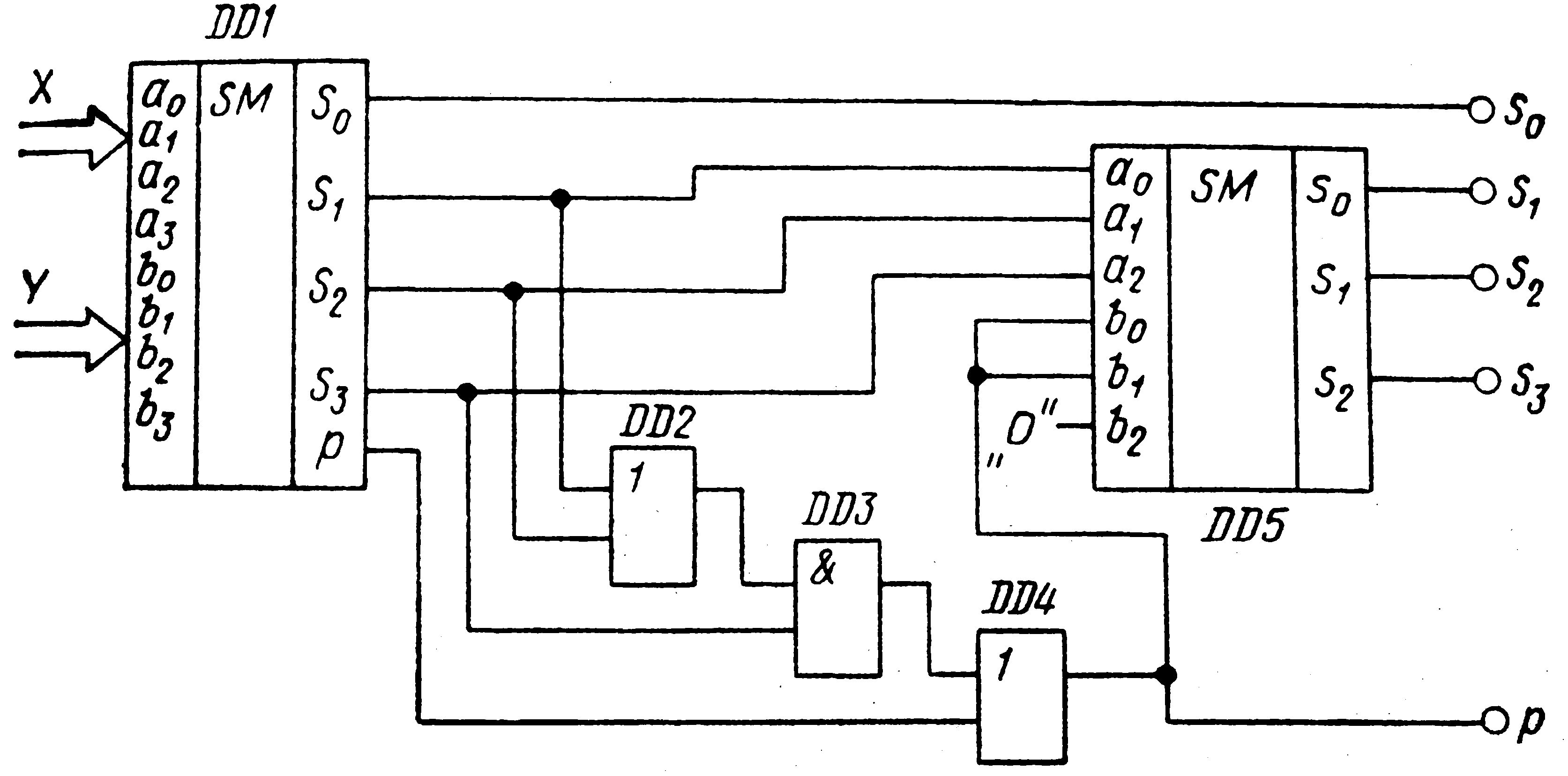

Пример реализации такого устройства показан на рис. 2.20. Четырехразрядный сумматор DD1 выполняет арифметическое сложение исходных двоично-десятичных кодов. Логическая схема на элементахDD2,DD3 иDD4 реализует ФАЛ (2.1), определяя необходимость дополнительного суммирования, выполняемого сумматоромDD5.

<>

Рисунок 2.20 — Сумматор двух BCD-чисел<>