- •1. Встраиваемые системы. Классификация встраиваемых систем.

- •2. Определение Системы на кристалле.

- •3. Процесс разработки SoC.

- •4. Архитектура процессора.

- •5. Простые последовательные процессоры.

- •6. Конвейерный процессор.

- •7. Ilp (параллелизм на уровне инструкций).

- •8. Основные этапы (уровни) проектирования SoC. Системный уровень проектирования.

- •9. Функциональный уровень проектирования SoC.

- •10. Особенности проектирования SoC.

- •11. Классификация средств автоматизированного проектирования

- •12. Этапы проектных процедур с использованием сапр.

- •13. Маршруты проектирования плис.

- •14. Выбор процессора для SoC.

- •15. Структурная схема систем на кристалле. Варианты реализации систем на кристалле.

- •16. Особенности процессоров Soft-Core.

- •17. Основные понятия в процессорной архитектуре. Набор команд. Соглашения о наборе команд.

- •18. Машинный язык.

- •25. Арифметико-логическое устройство (алу).

- •Классификация алу

- •26. Устройство сдвига.

- •27. Двоичные числа с фиксированной точкой.

- •Кодирование отрицательных чисел в эвм

- •28. Двоичные числа с плавающей точкой.

- •Ieee 753-1985 определяет четыре формата представления чисел с плавающей запятой:

- •Формальное представление нормализованных чисел в формате ieee 754.

- •29. Проблема подсистемы памяти. Иерархия памяти. Локальность.

- •30. Матрицы памяти.

- •31. Типы памяти.

- •32. Логические функции и пзу (rom). Многопортовая память.

- •33. Матрицы логических элементов. Программируемые логические матрицы.

- •34. Матрицы логических элементов. Программируемая пользователем матрица логических элементов.

- •36. Ввод-вывод, отображённый в память. Аппаратная реализация ввода-вывода, отображённого в память.

- •37. Архитектура микропроцессорного ядра MicroBlaze.

- •38. Конвейерный регистр команд микропроцессорного ядра MicroBlaze.

- •39. Прерывания микропроцессорного ядра MicroBlaze.

- •40. Кэш память микропроцессорного ядра MicroBlaze.

- •41. Назначение и структура регистра статуса.

- •Структура регистра статуса msr микропроцессорного ядра MicroBlaze

- •42. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 1

- •Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •43. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 2 Небольшое введение: Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •Периферийные компоненты для микропроцессорного ядра MicroBlaze

- •44. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 3

- •45. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 4

- •46. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 5

- •47. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 6

- •Эволюция axi

- •52. Axi Interconnect. Прямое соединение. Только преобразование.

- •53. Axi Interconnect. Межсоединение n-к-1. Межсоединение 1-к-n.

- •54. Axi Interconnect. Межсоединение n-к -m.

6. Конвейерный процессор.

Конвейер – это простой подход к использованию параллелизма, основанный на одновременном выполнении различных фаз (выборки инструкции, декодирование, выполнение и т.д.) обработки инструкции. Конвейерная передача предполагает, что эти фазы независимы между различными операциями и могут быть перекрыты – когда это условие не выполняется, процессор останавливает последующие фазы для обеспечения зависимости. Таким образом, несколько операций могут обрабатываться одновременно с каждой операцией на разных этапах её разработки.

Instruction 1

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Instruction 2

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Instruction 3

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Instruction 4

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Time →

Примеры SoC с использованием конвейерных Soft процессоров – процессор реализован с помощью ПЛИС или аналогичной реконфигурируемой технологии.

Процессор |

Длина слова (бит) |

Уровень конвейера |

Всего И/Д-кеш (КБ) |

Floating-Point Unit (FPU) |

Реализация |

|

Xilinx MicroBlaze |

32 |

3 |

0-64 |

Опционально |

FPGA |

|

Altera Nios II fast |

32 |

6 |

0-64 |

- |

FPGA |

|

ARC 600 |

16/32 |

5 |

0-32 |

Опционально |

ASIC |

|

Tensilica Xtensa LX |

16/32 |

5-7 |

0-32 |

Опционально |

ASIC |

|

Cambridge XAP3a |

16/32 |

2 |

- |

- |

ASIC |

|

7. Ilp (параллелизм на уровне инструкций).

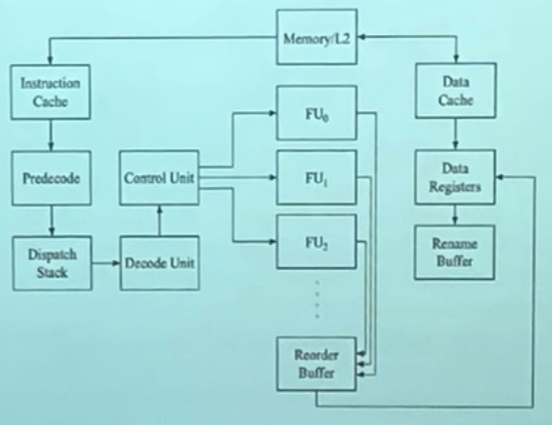

Хотя конвейер не обязательно приводит к выполнению нескольких инструкций одновременно, есть и другие методы. Эти технологии могут использовать некоторую комбинацию статического планирования и динамического анализа для одновременного выполнения фактической фазы оценки нескольких различных операций, потенциально обеспечивая скорость выполнения более одной операции за каждый цикл. Поскольку исторически большинство инструкций состоят только из одной операции, этот вид параллелизма был назван ILP (параллелизм на уровне инструкций).

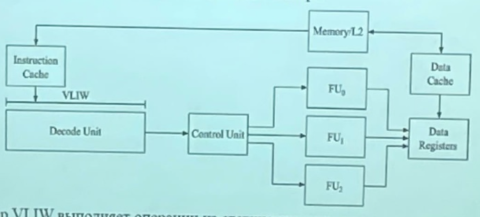

Две архитектуры, которые используются в ILP – это суперскалярные процессоры и процессоры VLIW. Они используют различные методы для достижения скорости выполнения, превышающей одну операцию за цикл.

Суперскалярный процессор динамически исследует поток инструкции, чтобы определить, какие операции являются независимыми и могут быть вырезаны.

Процессор VLIW (very long instruction word – «очень длинная машинная команда») полагается на компилятор, для анализа доступных операций (OP) и планирования независимых операций в длинные слова инструкции, которые затем выполняют эти операции параллельно без дальнейшего анализа.

Instruction 1

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Instruction 2

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Instruction 3

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Instruction 4

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Instruction 5

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Instruction 5

-

IF

→

ID

→

AG

→

DF

→

EX

→

WB

Time →

Суперскалярные процессоры. Динамические конвейерные процессоры по-прежнему ограничены выполнение одной операции за цикл в силу своего скалярного характера. Этого ограничения можно избежать, добавив несколько функциональных блоков и динамического планировщика для обработки более одной инструкции за цикл.

Наиболее значительным преимуществом суперскалярного процессора является то, что обработка нескольких команд за цикл выполняется прозрачно для пользователя.

Процессоры VLIW. В отличие от динамического анализа в аппаратном обеспечении для определения того, какие операции могут выполняться параллельно, процессоры VLIW полагаются на статический анализ в компиляторе.

Процессор VLIW выполняет операции из статически запланированных инструкций, которые содержат несколько независимых оераций.

Для приложений, которые могут быть запланированы статически для эфеективного использования ресурсов процессора, простая реализация VLIW приводит к высокой производительности. К сожалению, не все приложения могут быть эффективно запланированы статически. Во многих приложениях выполнение не проходит точно по определённому пути.