- •1. Встраиваемые системы. Классификация встраиваемых систем.

- •2. Определение Системы на кристалле.

- •3. Процесс разработки SoC.

- •4. Архитектура процессора.

- •5. Простые последовательные процессоры.

- •6. Конвейерный процессор.

- •7. Ilp (параллелизм на уровне инструкций).

- •8. Основные этапы (уровни) проектирования SoC. Системный уровень проектирования.

- •9. Функциональный уровень проектирования SoC.

- •10. Особенности проектирования SoC.

- •11. Классификация средств автоматизированного проектирования

- •12. Этапы проектных процедур с использованием сапр.

- •13. Маршруты проектирования плис.

- •14. Выбор процессора для SoC.

- •15. Структурная схема систем на кристалле. Варианты реализации систем на кристалле.

- •16. Особенности процессоров Soft-Core.

- •17. Основные понятия в процессорной архитектуре. Набор команд. Соглашения о наборе команд.

- •18. Машинный язык.

- •25. Арифметико-логическое устройство (алу).

- •Классификация алу

- •26. Устройство сдвига.

- •27. Двоичные числа с фиксированной точкой.

- •Кодирование отрицательных чисел в эвм

- •28. Двоичные числа с плавающей точкой.

- •Ieee 753-1985 определяет четыре формата представления чисел с плавающей запятой:

- •Формальное представление нормализованных чисел в формате ieee 754.

- •29. Проблема подсистемы памяти. Иерархия памяти. Локальность.

- •30. Матрицы памяти.

- •31. Типы памяти.

- •32. Логические функции и пзу (rom). Многопортовая память.

- •33. Матрицы логических элементов. Программируемые логические матрицы.

- •34. Матрицы логических элементов. Программируемая пользователем матрица логических элементов.

- •36. Ввод-вывод, отображённый в память. Аппаратная реализация ввода-вывода, отображённого в память.

- •37. Архитектура микропроцессорного ядра MicroBlaze.

- •38. Конвейерный регистр команд микропроцессорного ядра MicroBlaze.

- •39. Прерывания микропроцессорного ядра MicroBlaze.

- •40. Кэш память микропроцессорного ядра MicroBlaze.

- •41. Назначение и структура регистра статуса.

- •Структура регистра статуса msr микропроцессорного ядра MicroBlaze

- •42. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 1

- •Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •43. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 2 Небольшое введение: Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •Периферийные компоненты для микропроцессорного ядра MicroBlaze

- •44. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 3

- •45. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 4

- •46. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 5

- •47. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 6

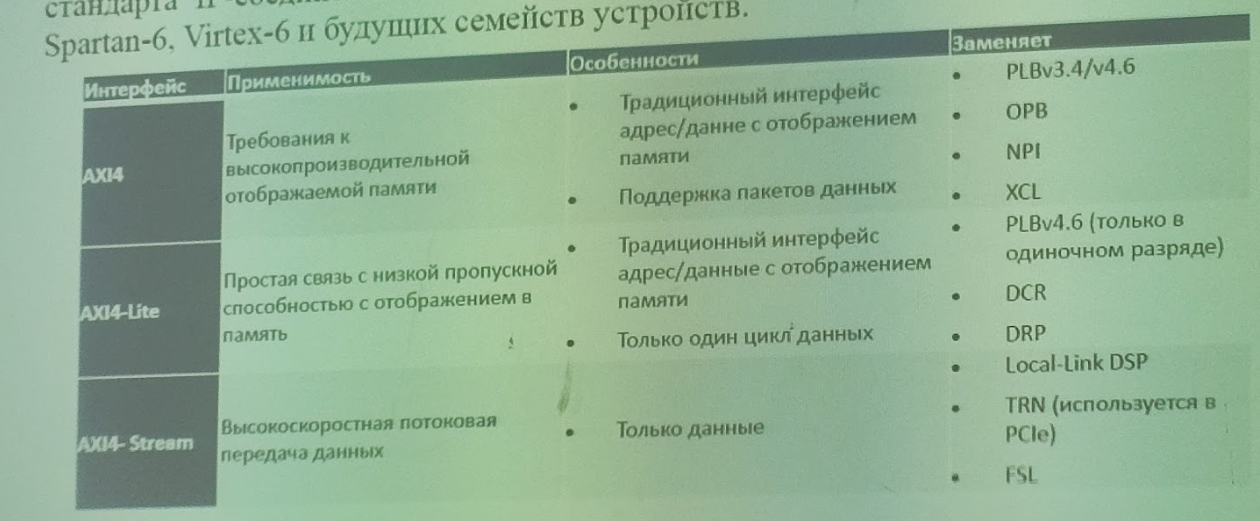

- •Эволюция axi

- •52. Axi Interconnect. Прямое соединение. Только преобразование.

- •53. Axi Interconnect. Межсоединение n-к-1. Межсоединение 1-к-n.

- •54. Axi Interconnect. Межсоединение n-к -m.

Эволюция axi

52. Axi Interconnect. Прямое соединение. Только преобразование.

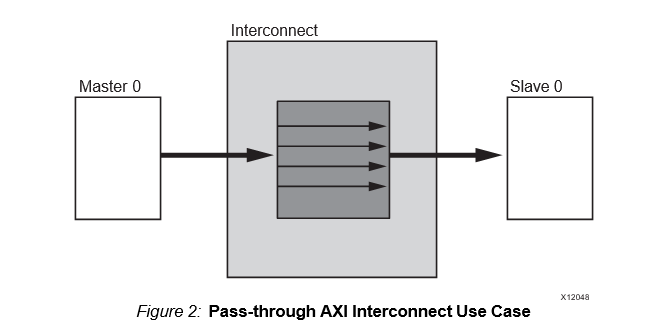

Прямое соединение

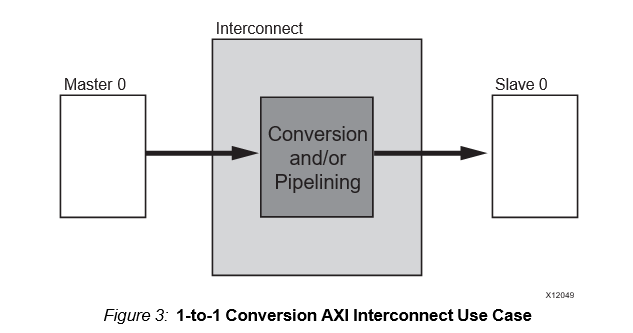

Только преобразование

Из ДАТА.ЧИТА

(Общая инфа)

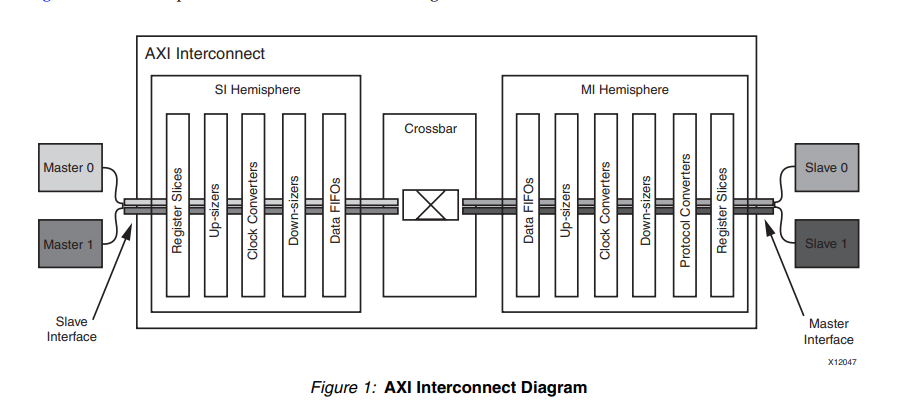

Межсоединение AXI состоит из SI (Slave interface), MI (master) и функциональных блоков, которые составляют пути каналов AXI между ними. SI получает запросы на запись и чтение транзакций от подключенных ведущих устройств. Ми подключается к ведомым устройствам. В центре находится перекладина, которая направляет трафик по всем каналам AXI между различными устройства, подключенные к Si и Mi. AXI Interconnect также включает в себя другие функциональные блоки, расположенные между перекладины и каждый из интерфейсов, выполняющих различные функции преобразования и хранения. Перекладина эффективно разделяет AXI Interconnect посередине между функциональными блоками, связанными с SI (полушарие SI) и единицы, связанные с ИМ (полушарие ИМ). В следующем подразделе описаны модели использования AXI Interconnect.

Прямое соединение

Когда к AXI Interconnect подключено только одно ведущее устройство и только одно подчиненное устройство, а AXI Interconnect не выполняет никаких дополнительных функций преобразования или конвейеризации, AXI Interconnect вырождается в прямые проводные соединения без задержки и без логики ресурсы. На рисунке 2 показана сквозная диаграмма.

Только преобразование

AXI Interconnect может выполнять различные функции преобразования и конвейеризации при подключении одного ведущего устройства к одному подчиненному устройству. Этими функциями преобразования и конвейеризации являются:

Преобразование ширины данных (Data width conversion)

Преобразование тактового коэффициента (Clock rate conversion)

Адаптация ведомого устройства AXI4-Lite (AXI4-Lite slave adaptation)

Адаптация ведомого устройства AXI-3 (AXI-3 slave adaptation)

Конвейеризация, например срез регистра или канал данных FIFO (Pipelining, such as a register slice or data channel FIFO)

В этих случаях AXI Interconnect не содержит логики арбитража, декодирования или маршрутизации. В зависимости от выполняемого преобразования может возникнуть задержка. На рисунке 3 показан пример варианта использования преобразования один к одному.

53. Axi Interconnect. Межсоединение n-к-1. Межсоединение 1-к-n.

Из ДАТА.ЧИТА

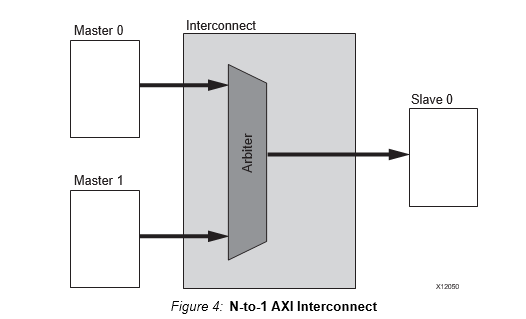

Межсоединение N-к-1

Распространенная вырожденная конфигурация AXI Interconnect возникает, когда несколько ведущих устройств арбитражируют доступ к одному подчиненному устройству, обычно контроллеру памяти.

В этих случаях логика декодирования адресов может быть ненужной и исключена из AXI Interconnect (если не требуется проверка диапазона адресов). Функции преобразования, такие как ширина данных и преобразование тактовой частоты, также могут быть выполнены в этой конфигурации, как показано на рисунке 4.

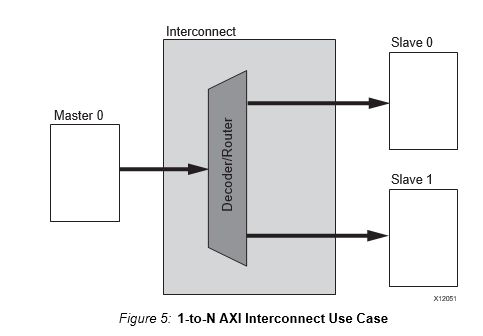

Межсоединение 1-к-N

Другая дегенеративная конфигурация AXI Interconnect возникает, когда одно ведущее устройство, обычно процессор, обращается к нескольким подчиненным периферийным устройствам с отображением памяти. В этих случаях арбитраж (в путях адреса и записи данных) не выполняется, как показано на рисунке 5.