- •1. Встраиваемые системы. Классификация встраиваемых систем.

- •2. Определение Системы на кристалле.

- •3. Процесс разработки SoC.

- •4. Архитектура процессора.

- •5. Простые последовательные процессоры.

- •6. Конвейерный процессор.

- •7. Ilp (параллелизм на уровне инструкций).

- •8. Основные этапы (уровни) проектирования SoC. Системный уровень проектирования.

- •9. Функциональный уровень проектирования SoC.

- •10. Особенности проектирования SoC.

- •11. Классификация средств автоматизированного проектирования

- •12. Этапы проектных процедур с использованием сапр.

- •13. Маршруты проектирования плис.

- •14. Выбор процессора для SoC.

- •15. Структурная схема систем на кристалле. Варианты реализации систем на кристалле.

- •16. Особенности процессоров Soft-Core.

- •17. Основные понятия в процессорной архитектуре. Набор команд. Соглашения о наборе команд.

- •18. Машинный язык.

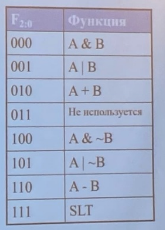

- •25. Арифметико-логическое устройство (алу).

- •Классификация алу

- •26. Устройство сдвига.

- •27. Двоичные числа с фиксированной точкой.

- •Кодирование отрицательных чисел в эвм

- •28. Двоичные числа с плавающей точкой.

- •Ieee 753-1985 определяет четыре формата представления чисел с плавающей запятой:

- •Формальное представление нормализованных чисел в формате ieee 754.

- •29. Проблема подсистемы памяти. Иерархия памяти. Локальность.

- •30. Матрицы памяти.

- •31. Типы памяти.

- •32. Логические функции и пзу (rom). Многопортовая память.

- •33. Матрицы логических элементов. Программируемые логические матрицы.

- •34. Матрицы логических элементов. Программируемая пользователем матрица логических элементов.

- •36. Ввод-вывод, отображённый в память. Аппаратная реализация ввода-вывода, отображённого в память.

- •37. Архитектура микропроцессорного ядра MicroBlaze.

- •38. Конвейерный регистр команд микропроцессорного ядра MicroBlaze.

- •39. Прерывания микропроцессорного ядра MicroBlaze.

- •40. Кэш память микропроцессорного ядра MicroBlaze.

- •41. Назначение и структура регистра статуса.

- •Структура регистра статуса msr микропроцессорного ядра MicroBlaze

- •42. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 1

- •Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •43. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 2 Небольшое введение: Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •Периферийные компоненты для микропроцессорного ядра MicroBlaze

- •44. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 3

- •45. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 4

- •46. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 5

- •47. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 6

- •Эволюция axi

- •52. Axi Interconnect. Прямое соединение. Только преобразование.

- •53. Axi Interconnect. Межсоединение n-к-1. Межсоединение 1-к-n.

- •54. Axi Interconnect. Межсоединение n-к -m.

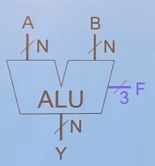

25. Арифметико-логическое устройство (алу).

Арифметико-логическое устройство (АЛУ) является узлом ЭВМ, который выполняет арифметические и логические операции над данными, обрабатываемыми ЭВМ.

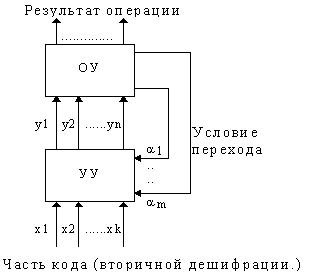

В общем случае многофункциональное АЛУ включает операционную часть (ОУ) и устройство управления (УУ), которое осуществляет вторичную дешифрацию кода команды и определяет выполняемую в АЛУ операцию.

Рисунок. Структура АЛУ

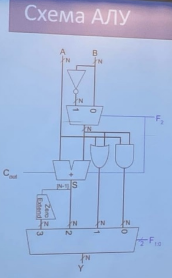

Подробная структура АЛУ представлена на рисунке.

Исходные данные (операнды) по командам УУ считываются из ОЗУ в регистры первого и второго операндов (связь 1).

Из УУ в блок управления АЛУ поступает команда на выполнение той или иной операции (связь 2), которая передается им в операционную часть (связь 3).

В соответствии с этой командой операционная часть выполняет нужное действие с данными, которые выбираются из регистров первого и второго операндов (связь 6). Результат заносится в регистр результата (связь 4), откуда – в ОЗУ (связь 5).

Структура регистров АЛУ, куда помещаются исходные и результирующие данные, а также размер регистров (число двоичных разрядов) формируют понятие разрядной сетки.

Набор выполняемых в АЛУ операций должен обладать функциональной полнотой. Чтобы обеспечить функциональную полноту достаточно четырех операций:

обращение к памяти для записи/чтения данных;

инкремент/декремент;

сравнение (реализует возможность условного перехода);

останов работы устройства.

В первых процессорах количество операций ограничивалось шестнадцатью, теперь достигает нескольких сотен.

Количество выполняемых операций является важной характеристикой АЛУ.

Классификация алу

АЛУ можно классифицировать по ряду признаков, приведенных ниже.

1. Классификация по способу представления данных:

с фиксированной запятой;

с плавающей запятой.

2. Классификация по способу действия над операндами:

последовательные АЛУ, где каждая операция выполняется последовательно над каждым разрядом;

параллельные АЛУ, операция выполняется над всеми разрядами данных одновременно;

последовательно - параллельные АЛУ, где слово данных делится на слоги, обработка данных ведется параллельно над разрядами слога и последовательно над слогами.

3. Классификация по использованию систем счисления:

двоичная;

двоично- десятичная;

восьмеричная;

шестнадцатеричная;

и т.д.

4. Классификация по характеру использования элементов и узлов:

блочные- для выполнения отдельных арифметических операций в структуру АЛУ вводят специальные блоки, что позволяет процесс обработки информации вести параллельно;

конвейерные- в конвейерных АЛУ операция разбивается на последовательность микроопераций, выполняемых за одинаковые промежутки времени (такты) на разных ступенях конвейера, что позволяет выполнять операцию над потоком операндов каждый такт;

многофункциональные- это универсальные АЛУ, выполняющие множество операций в одном устройстве. В таких АЛУ требуется настройка на выполнение данной операции при помощи кода операции.

Слайды с лекций: