- •1. Встраиваемые системы. Классификация встраиваемых систем.

- •2. Определение Системы на кристалле.

- •3. Процесс разработки SoC.

- •4. Архитектура процессора.

- •5. Простые последовательные процессоры.

- •6. Конвейерный процессор.

- •7. Ilp (параллелизм на уровне инструкций).

- •8. Основные этапы (уровни) проектирования SoC. Системный уровень проектирования.

- •9. Функциональный уровень проектирования SoC.

- •10. Особенности проектирования SoC.

- •11. Классификация средств автоматизированного проектирования

- •12. Этапы проектных процедур с использованием сапр.

- •13. Маршруты проектирования плис.

- •14. Выбор процессора для SoC.

- •15. Структурная схема систем на кристалле. Варианты реализации систем на кристалле.

- •16. Особенности процессоров Soft-Core.

- •17. Основные понятия в процессорной архитектуре. Набор команд. Соглашения о наборе команд.

- •18. Машинный язык.

- •25. Арифметико-логическое устройство (алу).

- •Классификация алу

- •26. Устройство сдвига.

- •27. Двоичные числа с фиксированной точкой.

- •Кодирование отрицательных чисел в эвм

- •28. Двоичные числа с плавающей точкой.

- •Ieee 753-1985 определяет четыре формата представления чисел с плавающей запятой:

- •Формальное представление нормализованных чисел в формате ieee 754.

- •29. Проблема подсистемы памяти. Иерархия памяти. Локальность.

- •30. Матрицы памяти.

- •31. Типы памяти.

- •32. Логические функции и пзу (rom). Многопортовая память.

- •33. Матрицы логических элементов. Программируемые логические матрицы.

- •34. Матрицы логических элементов. Программируемая пользователем матрица логических элементов.

- •36. Ввод-вывод, отображённый в память. Аппаратная реализация ввода-вывода, отображённого в память.

- •37. Архитектура микропроцессорного ядра MicroBlaze.

- •38. Конвейерный регистр команд микропроцессорного ядра MicroBlaze.

- •39. Прерывания микропроцессорного ядра MicroBlaze.

- •40. Кэш память микропроцессорного ядра MicroBlaze.

- •41. Назначение и структура регистра статуса.

- •Структура регистра статуса msr микропроцессорного ядра MicroBlaze

- •42. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 1

- •Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •43. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 2 Небольшое введение: Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •Периферийные компоненты для микропроцессорного ядра MicroBlaze

- •44. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 3

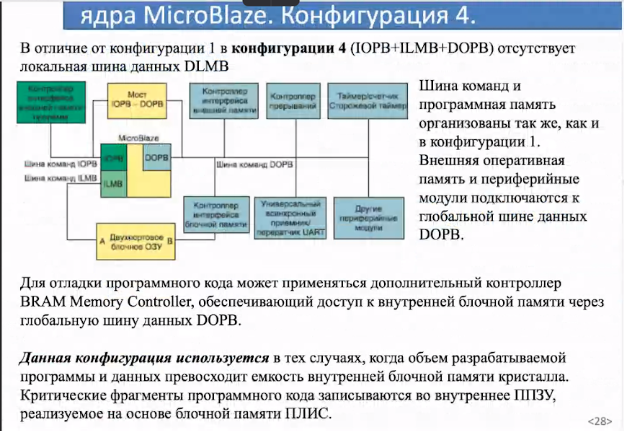

- •45. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 4

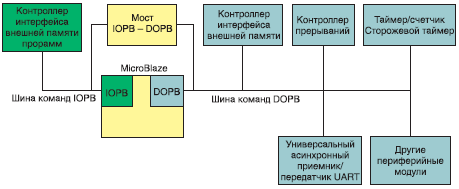

- •46. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 5

- •47. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 6

- •Эволюция axi

- •52. Axi Interconnect. Прямое соединение. Только преобразование.

- •53. Axi Interconnect. Межсоединение n-к-1. Межсоединение 1-к-n.

- •54. Axi Interconnect. Межсоединение n-к -m.

Периферийные компоненты для микропроцессорного ядра MicroBlaze

Пакет программных средств разработки встраиваемых микропроцессорных систем EDK помимо ядра MicroBlaze содержит набор компонентов периферийных модулей, которые представлены в форме IP-ядер (Intellectual Property). При проектировании «систем на кристалле» на основе микропроцессорного ядра MicroBlaze, разработчик может использовать следующие IP-модули:

таймер-счетчик;

сторожевой таймер;

универсальный асинхронный приемник-передатчик UART;

контроллер прерываний Interrupt Controller;

контроллер стандартного интерфейса ввода-вывода;

контроллер интерфейса памяти SDRAM;

контроллер интерфейса памяти DDR SDRAM;

контроллер интерфейса памяти Flash Memory;

контроллер интерфейса блочной памяти BlockRAM;

контроллер интерфейса Serial Peripheral Interface, соответствующего спецификации фирмы Motorola;

универсальный асинхронный приемник-передатчик UART, использующий для коммуникации JTAG-порт

44. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 3

45. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 4

46. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 5

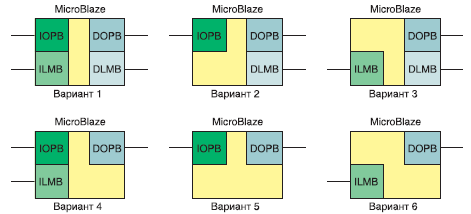

Каждая из шин микропроцессорного ядра MicroBlaze (шина данных и шина команд) фактически разделяется на две независимые магистрали: * глобальную шину, соответствующую спецификации OPB; * локальную шину, соответствующую спецификации LMB. В микропроцессорной системе, разрабатываемой на основе ядра MicroBlaze, шины данных и команд могут быть реализованы как в полном составе, так и в виде только локальной LMB или только глобальной магистрали OPB. На показаны шесть возможных вариантов конфигурации шинных интерфейсов микропроцессорного ядра MicroBlaze.

Здесь и далее используется следующая система обозначений: DOPB — шина данных, соответствующая спецификации OPB; DLMB — локальная шина данных, соответствующая спецификации LMB; IOPB — шина команд, соответствующая спецификации OPB; ILMB — локальная шина команд, соответствующая спецификации LMB.

В конфигурации 5 (IOPB+DOPB) шины данных и команд представлены только глобальными магистралями, соответствующими спецификации OPB Для хранения кода программ и данных используется внешняя память. Сопряжение памяти данных и периферийных модулей с микропроцессорным ядром осуществляется теми же способами, что и в конфигурации 1. Конфигурации 5 применяется, как правило, при больших объемах программного кода и данных, которые не содержат критических секций.

47. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 6

Наиболее компактной является конфигурация 6 (ILMB+DOPB), в которой задействованы только локальная шина команд ILMB и глобальная шина данных DOPB. Программная память в данной конфигурации формируется на базе блочной памяти кристалла FPGA, доступ к которой производится по быстрой локальной шине ILMB, что обеспечивает минимальное время выборки команд. Конфигурацию 6 целесообразно использовать при небольшом объеме программного кода, не превосходящем емкости блочной памяти ПЛИС.

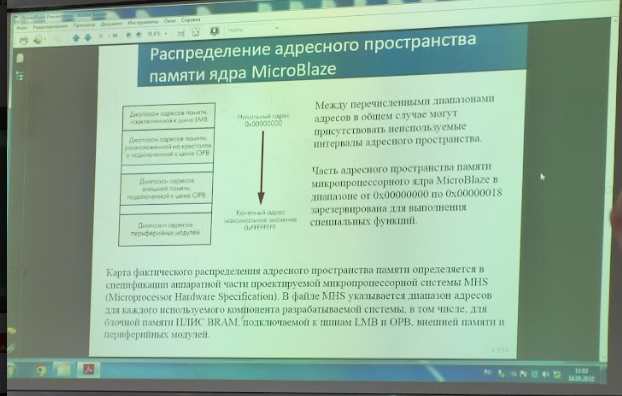

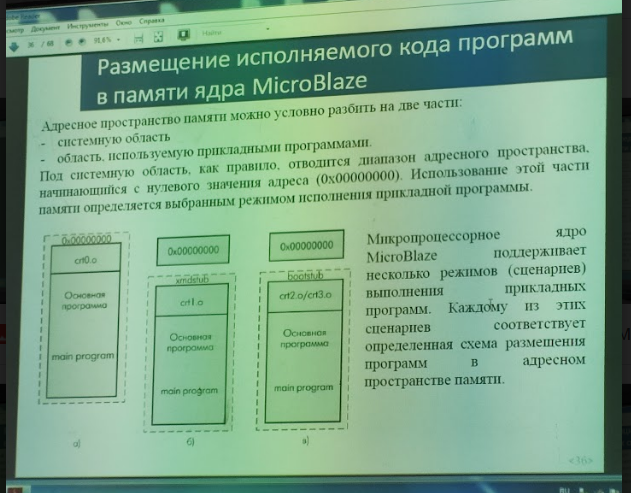

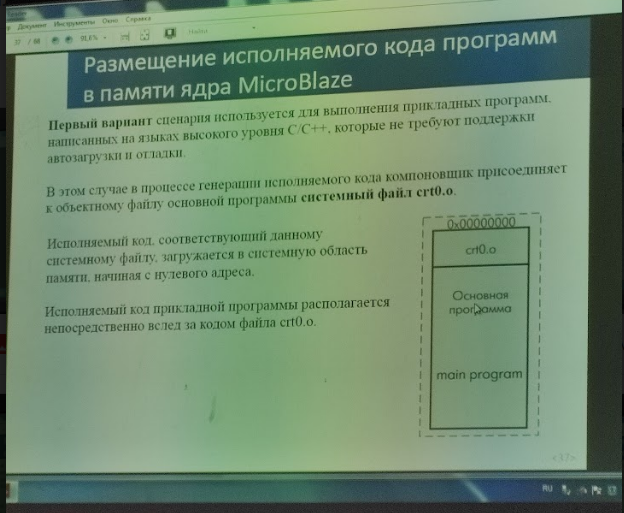

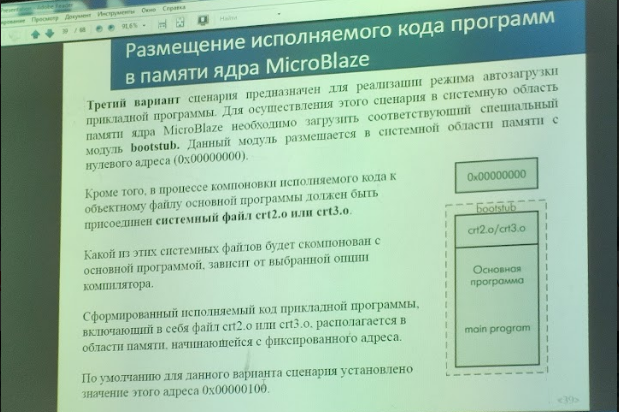

48. Распределение адресного пространства памяти ядра MicroBlaze.

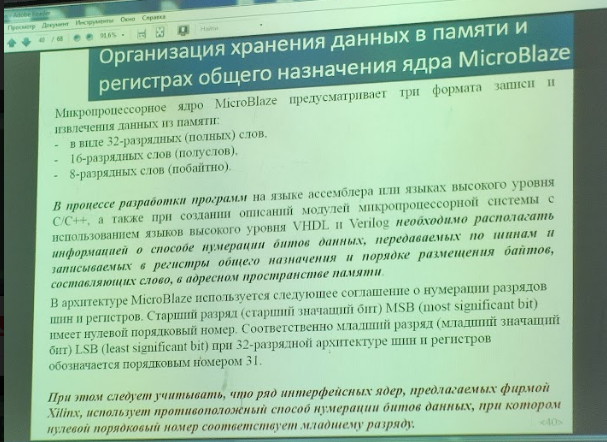

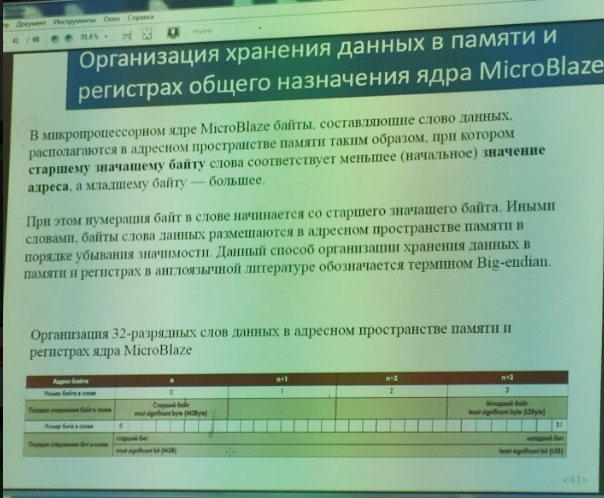

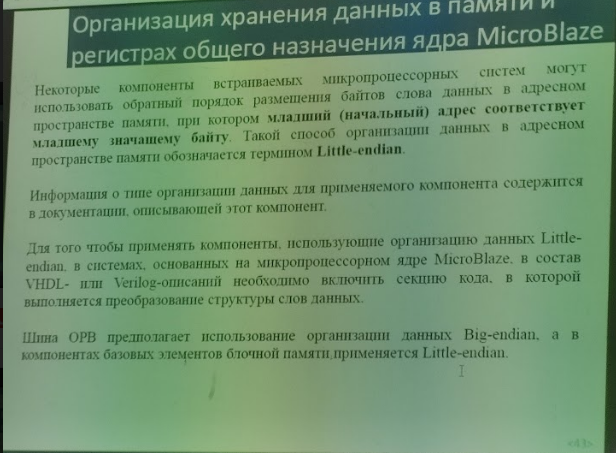

49. Организация хранения данных в памяти и регистрах общего назначения ядра MicroBlaze.

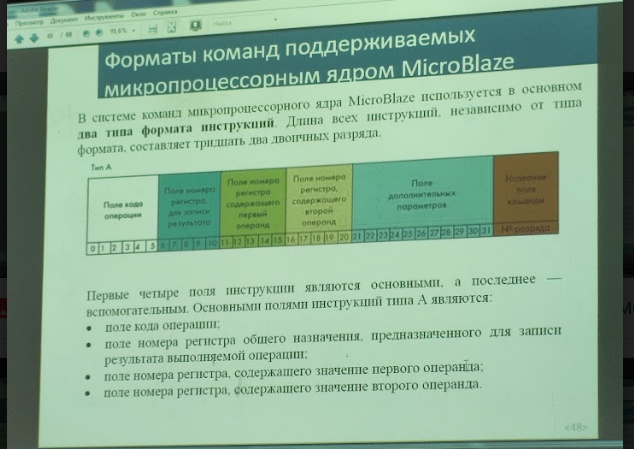

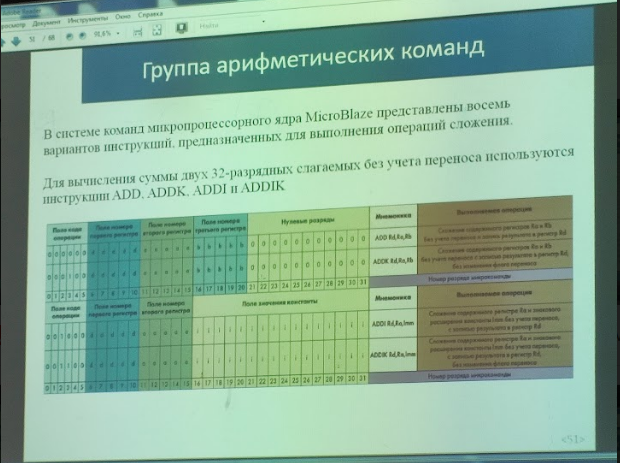

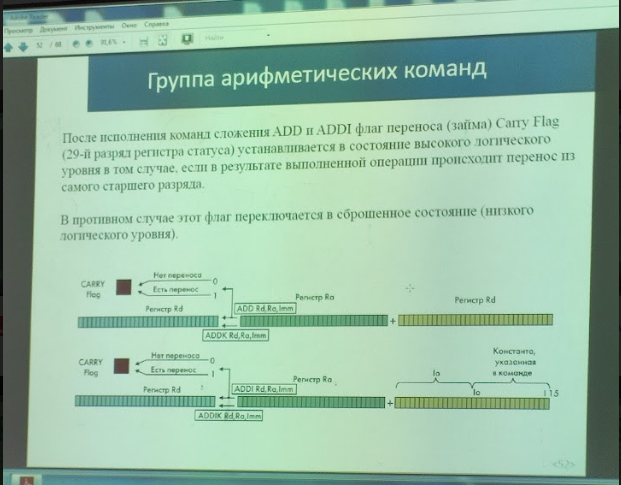

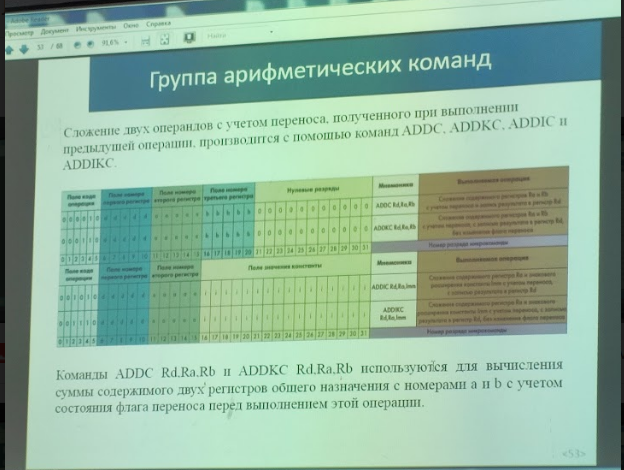

50. Общая характеристика команд MicroBlaze. Форматы команд, поддерживаемых микропроцессорным ядром MicroBlaze.

51. Протокол AXI.

Протокол AXI (Advanced eXtensible Inretface) – обеспечивает интерфейс передачи между системой обработки и программируемой логикой (используется в устройствах Zynq от Xilinx).

Спецификация AXI предоставляет структуру, которая определяет протоколы для перемещения данных между IP-блоками с использованием определенного стандарта сигнализации.

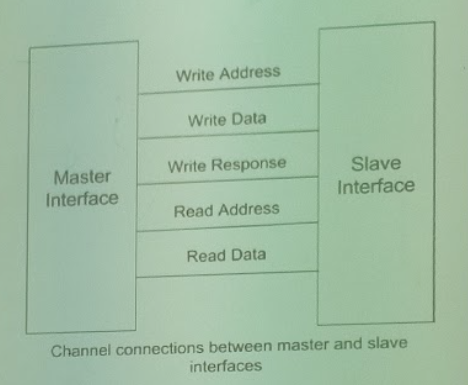

Между

этими двумя устройствами (или более

при использовании IP-ядра

AXI

Interconnect)

существует 5

каналов (каждый из них имеет как свои

уникальные сигналы, так и похожие среди

всех пяти):

Адрес

чтения;

Адрес

записи;

Чтение

данных;

Запись

данных;

Ответ

на запись.

Спецификации протокола:

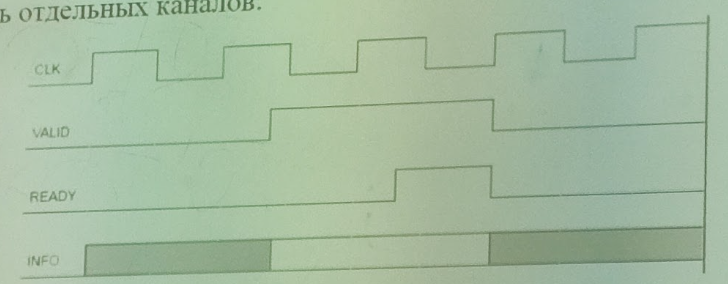

Перед передачей любого управляющего сигнала адреса/данных ведущий и ведомый должны сконнектиться с помощью сигналов готовности (READY) и валидности (VALID).

Сигналы READY и VALID есть для каждого из пяти каналов, т.к. они позволяют установить связь для каждого из 5 каналов.

Для передачи любого сигнала (адрес/данные/ответ и т.д.) соответствующий источник канала устанавливает сигнал VALID в активное состояние, а адресат того же канала должен сделать активным сигнал READY. После этого начинается передача по этому каналу.

Существуют отдельные фазы и каналы для передачи управляющего сигнала/адреса и данных;

Связь пакетного типа обеспечивает непрерывную передачу данных.