- •1. Встраиваемые системы. Классификация встраиваемых систем.

- •2. Определение Системы на кристалле.

- •3. Процесс разработки SoC.

- •4. Архитектура процессора.

- •5. Простые последовательные процессоры.

- •6. Конвейерный процессор.

- •7. Ilp (параллелизм на уровне инструкций).

- •8. Основные этапы (уровни) проектирования SoC. Системный уровень проектирования.

- •9. Функциональный уровень проектирования SoC.

- •10. Особенности проектирования SoC.

- •11. Классификация средств автоматизированного проектирования

- •12. Этапы проектных процедур с использованием сапр.

- •13. Маршруты проектирования плис.

- •14. Выбор процессора для SoC.

- •15. Структурная схема систем на кристалле. Варианты реализации систем на кристалле.

- •16. Особенности процессоров Soft-Core.

- •17. Основные понятия в процессорной архитектуре. Набор команд. Соглашения о наборе команд.

- •18. Машинный язык.

- •25. Арифметико-логическое устройство (алу).

- •Классификация алу

- •26. Устройство сдвига.

- •27. Двоичные числа с фиксированной точкой.

- •Кодирование отрицательных чисел в эвм

- •28. Двоичные числа с плавающей точкой.

- •Ieee 753-1985 определяет четыре формата представления чисел с плавающей запятой:

- •Формальное представление нормализованных чисел в формате ieee 754.

- •29. Проблема подсистемы памяти. Иерархия памяти. Локальность.

- •30. Матрицы памяти.

- •31. Типы памяти.

- •32. Логические функции и пзу (rom). Многопортовая память.

- •33. Матрицы логических элементов. Программируемые логические матрицы.

- •34. Матрицы логических элементов. Программируемая пользователем матрица логических элементов.

- •36. Ввод-вывод, отображённый в память. Аппаратная реализация ввода-вывода, отображённого в память.

- •37. Архитектура микропроцессорного ядра MicroBlaze.

- •38. Конвейерный регистр команд микропроцессорного ядра MicroBlaze.

- •39. Прерывания микропроцессорного ядра MicroBlaze.

- •40. Кэш память микропроцессорного ядра MicroBlaze.

- •41. Назначение и структура регистра статуса.

- •Структура регистра статуса msr микропроцессорного ядра MicroBlaze

- •42. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 1

- •Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •43. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 2 Небольшое введение: Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •Периферийные компоненты для микропроцессорного ядра MicroBlaze

- •44. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 3

- •45. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 4

- •46. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 5

- •47. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 6

- •Эволюция axi

- •52. Axi Interconnect. Прямое соединение. Только преобразование.

- •53. Axi Interconnect. Межсоединение n-к-1. Межсоединение 1-к-n.

- •54. Axi Interconnect. Межсоединение n-к -m.

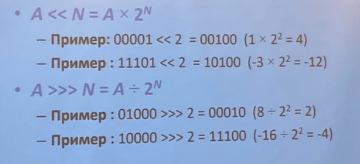

26. Устройство сдвига.

Операционное устройство сдвига обеспечивает полный набор сдвигов для 16-битных аргументов, результатом которых является 32-битное слово. Операции включают логические и арифметические сдвиги и нормализацию. Устройство также производит нахождение порядка и общего порядка для блока их нескольких чисел. Базовые примитивы могут быть эффективно скомбинированы для вычислений повышенной точности и реализации вычислений с плавающей точкой.

Сдвигатель обрабатывает непосредственные значения из очереди команд (I-Unit). А так же может двусторонне взаимодействовать с памятью, пространством ввода-вывода, регистрами устройства адресации (A-unit), устройства управления (P-unit) и регистрами, находящимися непосредственно в операционном устройстве(D-unit). Более того, сдвигатель может передавать значения в АЛУ операционного устройства (Как входное значение для дальнейших вычислений) и АЛУ устройства адресации (В качестве значений для сохранения в регистрах устройства адресации.)

Сдвигатель может выполнять следующие действия:

· Сдвиг 40-битных значений аккумулятора влево (на значение до 31) и вправо (на значение до 32). Размер сдвига может быть задан в одном из временных регистров T0 – T3 или константой в коде команды.

· Сдвиг 16-битных значений регистров, ячеек памяти или регистров в пространстве ввода – вывода (I/O space) влево (на значение до 31) и вправо (на значение до 32). Размер сдвига может быть задан в одном из временных регистров T0 – T3 или константой в качестве одного из операндов в команды.

· Сдвиг 16-битных непосредственных значений влево (на значение до 15 бит). Размер сдвига задается константой в одном из операндов команды.

· Циклический сдвиг значений в регистрах.

· Округление значений в аккумуляторе перед их записью в память.

· Выполнение сложений и умножений для некоторых команд, включающих сдвиг (Т.е. для команд, осуществляющих помимо сдвига дополнительные действия, например перемещение из одного регистра в другой значения со сдвигом)

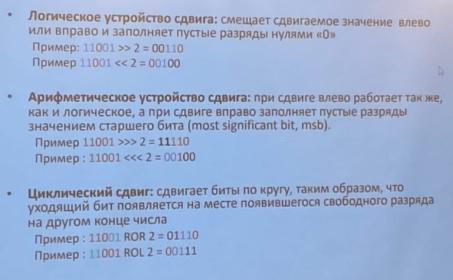

Существует несколько типов сдвига:

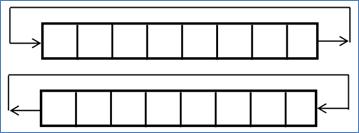

· Циклический сдвиг вправо – ror (rotate right) и влево – rol (rotate left)

При этом сдвиге уходящий бит записывается на место освободившегося бита.

Рис. 6 – Циклические сдвиги вправо и влево

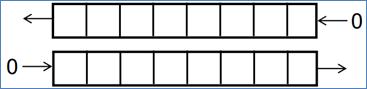

· Логический сдвиг – shtl (shift logically)

Это сдвиг, при котором уходящий бит уходит, не влияя на оставшееся биты, а на место появившегося бита записывается бит 0. Уходящий бит сохраняется во флаге переноса. Эта функция широко используется при работе с многобайтовыми числами.

Рис. 7 – Логические сдвиги влево и вправо

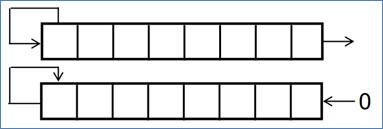

· Арифметический сдвиг – shts (shift signed)

При этом сдвиге слово рассматривается не просто как группа битов, а как целое число в дополнительном коде. При сдвиге влево на место освободившегося правого бита записывается 0, а знаковый бит сохраняется. При сдвиге вправо: уходящий бит уходит, не влияя на оставшиеся биты, а на освободившееся место знакового бита устанавливается бит, соответствующий знаку.

Рис. 8 – Арифметические сдвиги вправо и влево.

Слайды с лекций:

Как умножитель и делитель: