- •1. Встраиваемые системы. Классификация встраиваемых систем.

- •2. Определение Системы на кристалле.

- •3. Процесс разработки SoC.

- •4. Архитектура процессора.

- •5. Простые последовательные процессоры.

- •6. Конвейерный процессор.

- •7. Ilp (параллелизм на уровне инструкций).

- •8. Основные этапы (уровни) проектирования SoC. Системный уровень проектирования.

- •9. Функциональный уровень проектирования SoC.

- •10. Особенности проектирования SoC.

- •11. Классификация средств автоматизированного проектирования

- •12. Этапы проектных процедур с использованием сапр.

- •13. Маршруты проектирования плис.

- •14. Выбор процессора для SoC.

- •15. Структурная схема систем на кристалле. Варианты реализации систем на кристалле.

- •16. Особенности процессоров Soft-Core.

- •17. Основные понятия в процессорной архитектуре. Набор команд. Соглашения о наборе команд.

- •18. Машинный язык.

- •25. Арифметико-логическое устройство (алу).

- •Классификация алу

- •26. Устройство сдвига.

- •27. Двоичные числа с фиксированной точкой.

- •Кодирование отрицательных чисел в эвм

- •28. Двоичные числа с плавающей точкой.

- •Ieee 753-1985 определяет четыре формата представления чисел с плавающей запятой:

- •Формальное представление нормализованных чисел в формате ieee 754.

- •29. Проблема подсистемы памяти. Иерархия памяти. Локальность.

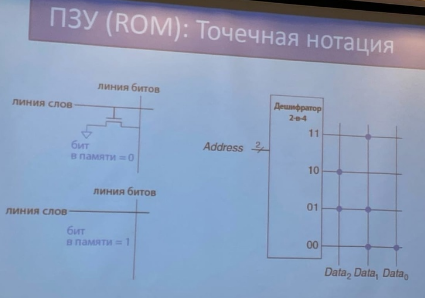

- •30. Матрицы памяти.

- •31. Типы памяти.

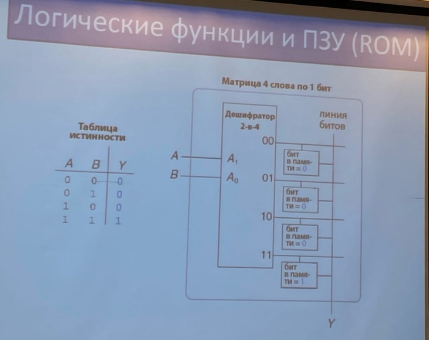

- •32. Логические функции и пзу (rom). Многопортовая память.

- •33. Матрицы логических элементов. Программируемые логические матрицы.

- •34. Матрицы логических элементов. Программируемая пользователем матрица логических элементов.

- •36. Ввод-вывод, отображённый в память. Аппаратная реализация ввода-вывода, отображённого в память.

- •37. Архитектура микропроцессорного ядра MicroBlaze.

- •38. Конвейерный регистр команд микропроцессорного ядра MicroBlaze.

- •39. Прерывания микропроцессорного ядра MicroBlaze.

- •40. Кэш память микропроцессорного ядра MicroBlaze.

- •41. Назначение и структура регистра статуса.

- •Структура регистра статуса msr микропроцессорного ядра MicroBlaze

- •42. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 1

- •Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •43. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 2 Небольшое введение: Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •Периферийные компоненты для микропроцессорного ядра MicroBlaze

- •44. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 3

- •45. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 4

- •46. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 5

- •47. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 6

- •Эволюция axi

- •52. Axi Interconnect. Прямое соединение. Только преобразование.

- •53. Axi Interconnect. Межсоединение n-к-1. Межсоединение 1-к-n.

- •54. Axi Interconnect. Межсоединение n-к -m.

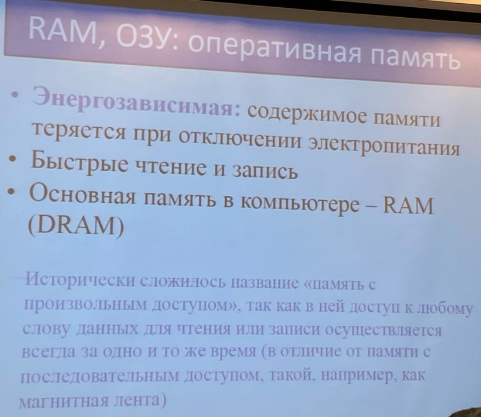

31. Типы памяти.

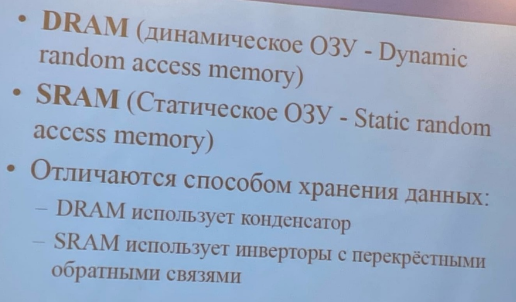

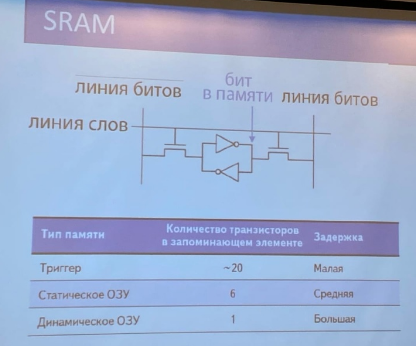

ТИПЫ RAM:

32. Логические функции и пзу (rom). Многопортовая память.

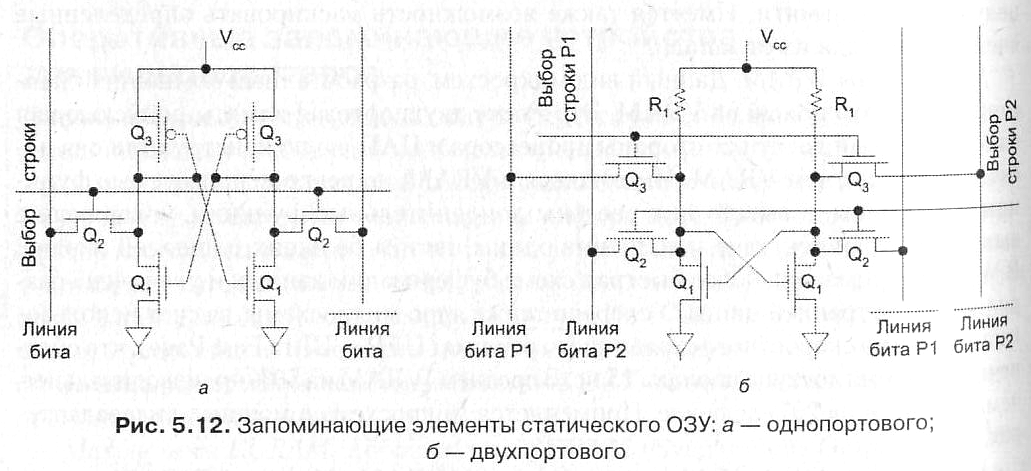

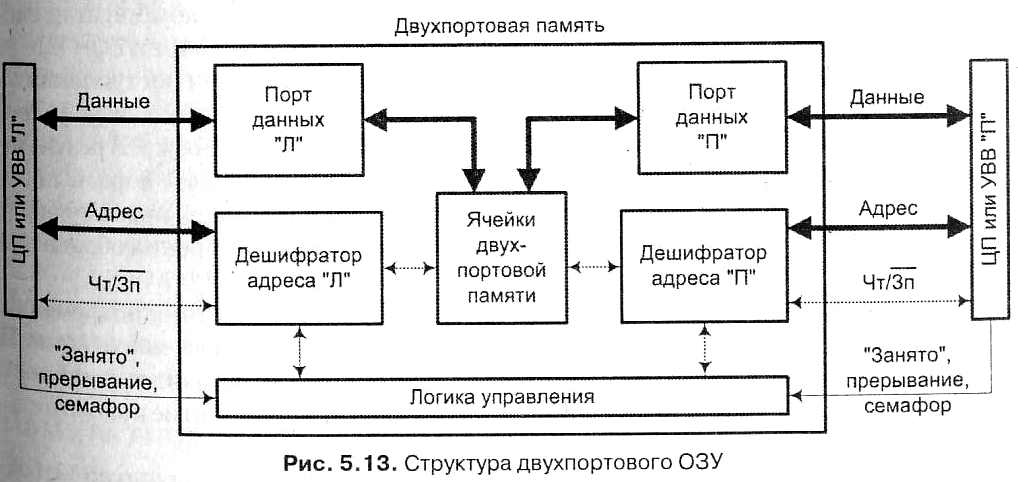

МНОГОПОРТОВЫЕ ОЗУ:

Стандартное однопортовое ОЗУ имеет по одной шине адреса, данных и управления и в каждый момент времени обеспечивает доступ к ячейке памяти только одному устройству. Структура запоминающего элемента (ЗЭ) такого ОЗУ приведена на рис. 5.12, а.

В отличие от стандартного в п-портовом ОЗУ имеется п независимых наборов шин адреса, данных и управления, гарантирующих одновременный и независимый доступ к ОЗУ п устройствам. Данное свойство позволяет существенно упростить создание многопроцессорных и многомашинных вычислительных систем, где многопортовое ОЗУ выступает в роли общей или совместно используемой памяти. В рамках одной ВМ подобное ОЗУ может обеспечивать обмен информацией между ЦП и УВВ (например, контроллером магнитного диска) намного эффективней, чем прямой доступ к памяти. В настоящее время серийно выпускаютсядвух- и четырехпортовые микросхемы, среди которых наиболее распространены первые. Поскольку архитектурные решения в обоих случаях схожи, дальнейшее изложение будет вестись применительно к двухпортовым ОЗУ.

ЗЭ двухпортового ОЗУ (см. рис.5.12,б) также содержит шесть транзисторов, но в отличие от стандартного ЗЭ (см. рис.5.12,а) транзисторы Q3 служат не в качестве резисторов, a предоставляют доступ к элементу с двух направлений.

В двухпортовой памяти имеются два набора адресных, информационных, управляющих сигнальных шин, каждый из которых обеспечивает доступ к общему массиву ЗЭ (рис. 5.13). Поскольку двухпортовому ОЗУ свойственна симметричная структура, в дальнейшем наборы шин будем называть «левым» (Л) и «правым» (П). В целом организация матрицы ЗЭ остается традиционной.

Доступ к ячейкам возможен как через левую, так и через правую группу шин, причем если Л- и П-адреса различны, никаких конфликтов не возникает. Проблемы потенциально возможны, когда Л- и П-устройства одновременно обращаются по одному и тому же адресу и хотя бы одно из этих устройств пытается выполнить операцию записи. В этом случае, если один из портов читает информацию, а другой производит запись в ту же ячейку, вероятно считывание недостоверной информации. При попытке единовременного ввода в ячейку с двух направлений в нее может быть занесена неопределенная комбинация из записываемых слов. Несмотря на то что вероятность подобных ситуаций по оценкам не превышает 0,1% такой вариант необходимо учитывать, для чего в двухпортовой памяти имеется схема арбитража с использованием сигналов «Занято».

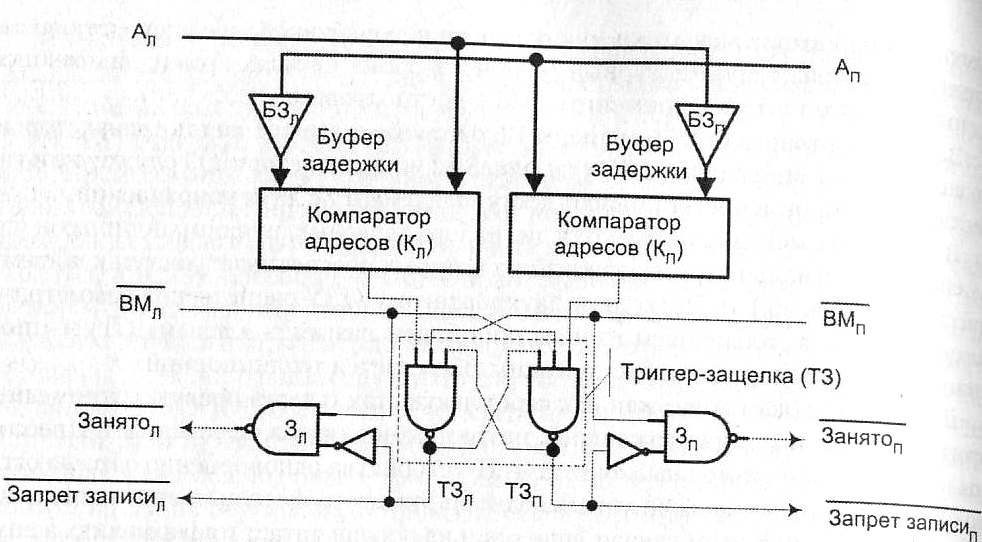

Рис.5.14. Логика арбитража в микросхеме реализована аппаратными средствами.

Схема обеспечивает формирование сигнала «Занято», запрещающего запись в ячейку для той половины, на которой адрес появится позже, а также принятие решения в пользу одного из входных портов при одновременном поступлении адресов. Арбитр содержит два компаратора адресов (КЛ и КП), два буфера задержки (БЗЛ и БЗП), триггер-защелку (ТЗ), образованный перекрестно связанными схемами «И-НЕ», и формирователи сигналов «Занято» (ЗЛ и ЗП)

Рис. 5.14. Логика арбитража с использованием сигнала «Занято»

Выявление адреса, поступившего первым, производится за счет буферов задержки и компараторов адресов. Так, если информация на адресной шине Ал уже стабилизировалась, а на шине Ап имеет тенденцию совпасть с Ал, то на выходе Кп сигнал «1» появится немедленно, как только адреса совпадут, в то время как на выходе К„ он сформируется с некоторой задержкой, определяемой БЗЛ. Эта ситуация фиксируется триггером-защелкой, на выходе которого возможны три комбинации сигналов: ТЗЛ = ТЗП = 1, ТЗЛ = 0 и ТЗП = 1, ТЗЛ =1 и ТЗП = 0. В исходном состоянии ТЗЛ = ТЗП = 1, поскольку на выходах обоих компараторов 0. В нашем случае при поступлении от Кп сигнала 1 на выходе ТЗП установится значение 0, в то время как выход ТЗЛ по-прежнему останется в состоянии 1, так как с Кл единица придет позже. В результате будет сформирован сигнал, запрещающий запись через правый порт, а также сигнал Занятоп, который поступает на устройство, подключенное к правому порту микросхемы, и может быть использован для задержки или повторения обращения к ячейке.

Если обращения к одной и той же ячейке происходят строго одновременно, сигналы с выходов Кл и Кп поступят на входы ТЗ также одновременно. Схема ТЗ реализована таким образом, что триггер и в этом случае установится в какое-то одно из двух своих нормальных состояний, что гарантирует принятие положительного решения на доступ к ячейке в пользу только одного из портов.

Сигналы выбора микросхемы ВМЛ и ВМ„ поступают непосредственно на ТЗ, благодаря чему при наличии обращения только от одного из портов арбитраж не производится.

Помимо возможности доступа к ячейкам с двух направлений, двухпортовая память снабжается средствами для обмена сообщениями между подключенными к ней устройствами: системой прерывания и системой семафоров. Первую из них называют аппаратной, а вторую — программной.

В системе прерываний двухпортовой памяти две последних ячейки микросхемы (с наибольшими адресами) используются в качестве «почтовых ящиков» для обмена сообщениями между устройствами, подключенными к Л- и П-портам. Сообщению от левого устройства выделена ячейка с четным адресом (если емкость памяти равна 1К, то это будет адрес 3FF16), а от правого — с нечетным (3FE16). Когда устройство записывает информацию в свой «почтовый ящик», формируется запрос прерывания к устройству, подключенному к противоположному порту. Этот сигнал автоматически сбрасывается, когда адресат считывает информацию из своего «почтового ящика».

Система семафоров — это имеющийся в двухпортовой памяти набор из восьми триггеров, состояние которых может быть прочитано и изменено со стороны любого из портов. Триггеры играют роль программных семафоров или флагов, с помощью которых Л- и П-устройства могут извещать друг друга о каких-то событиях. Сущность этих событий не зафиксирована и определяется реализуемыми программами. Обычно семафоры нужны для предоставления одному из процессоров монопольного права работы с определенным блоком данных до завершения всех необходимых операций с этим блоком. В этом случае процессор, монополизирующий блок данных, устанавливает один из семафоров в состояние 1, а по завершении — в 0. Второй процессор, прежде чем обратиться к данному блоку, считывает семафор и при единичном состоянии последнего повторяет считывание и анализ семафора до тех пор, пока первый процессор не установит его в состояние 0. Естественно, что в программном обеспечении Л- и П-процессоров распределение и правила использования семафоров должны быть согласованы.

Зачастую одной микросхемы многопортовой памяти не хватает из-за недостаточной емкости одной ИМС или ввиду малой разрядности ячеек. В обоих случаях необходимо соединить несколько микросхем, соответственно параллельно или последовательно. Если несколько микросхем объединяются в цепочку для достижения нужной разрядности слова, возникает проблема с арбитражем при одновременном обращении к одной и той же ячейке. В этих случаях в разных ИМС цепочки, в силу разброса их параметров, предпочтение может быть отдано разным портам, в то время как решение должно быть единым. Для исключения подобной ситуации микросхемы многопортовой памяти выпускаются в двух вариантах: ведущие (master) и ведомые (slave). Принятие решения производится только в ведущих микросхемах, а ведомые функционируют в соответствии с инструкцией, полученной от ведущего. Таким образом, в цепочке используется только одна микросхема типа «ведущий», а все прочие ИМС должны иметь тип «ведомый».