- •1. Встраиваемые системы. Классификация встраиваемых систем.

- •2. Определение Системы на кристалле.

- •3. Процесс разработки SoC.

- •4. Архитектура процессора.

- •5. Простые последовательные процессоры.

- •6. Конвейерный процессор.

- •7. Ilp (параллелизм на уровне инструкций).

- •8. Основные этапы (уровни) проектирования SoC. Системный уровень проектирования.

- •9. Функциональный уровень проектирования SoC.

- •10. Особенности проектирования SoC.

- •11. Классификация средств автоматизированного проектирования

- •12. Этапы проектных процедур с использованием сапр.

- •13. Маршруты проектирования плис.

- •14. Выбор процессора для SoC.

- •15. Структурная схема систем на кристалле. Варианты реализации систем на кристалле.

- •16. Особенности процессоров Soft-Core.

- •17. Основные понятия в процессорной архитектуре. Набор команд. Соглашения о наборе команд.

- •18. Машинный язык.

- •25. Арифметико-логическое устройство (алу).

- •Классификация алу

- •26. Устройство сдвига.

- •27. Двоичные числа с фиксированной точкой.

- •Кодирование отрицательных чисел в эвм

- •28. Двоичные числа с плавающей точкой.

- •Ieee 753-1985 определяет четыре формата представления чисел с плавающей запятой:

- •Формальное представление нормализованных чисел в формате ieee 754.

- •29. Проблема подсистемы памяти. Иерархия памяти. Локальность.

- •30. Матрицы памяти.

- •31. Типы памяти.

- •32. Логические функции и пзу (rom). Многопортовая память.

- •33. Матрицы логических элементов. Программируемые логические матрицы.

- •34. Матрицы логических элементов. Программируемая пользователем матрица логических элементов.

- •36. Ввод-вывод, отображённый в память. Аппаратная реализация ввода-вывода, отображённого в память.

- •37. Архитектура микропроцессорного ядра MicroBlaze.

- •38. Конвейерный регистр команд микропроцессорного ядра MicroBlaze.

- •39. Прерывания микропроцессорного ядра MicroBlaze.

- •40. Кэш память микропроцессорного ядра MicroBlaze.

- •41. Назначение и структура регистра статуса.

- •Структура регистра статуса msr микропроцессорного ядра MicroBlaze

- •42. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 1

- •Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •43. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 2 Небольшое введение: Шинные интерфейсы микропроцессорного ядра MicroBlaze

- •Периферийные компоненты для микропроцессорного ядра MicroBlaze

- •44. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 3

- •45. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 4

- •46. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 5

- •47. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 6

- •Эволюция axi

- •52. Axi Interconnect. Прямое соединение. Только преобразование.

- •53. Axi Interconnect. Межсоединение n-к-1. Межсоединение 1-к-n.

- •54. Axi Interconnect. Межсоединение n-к -m.

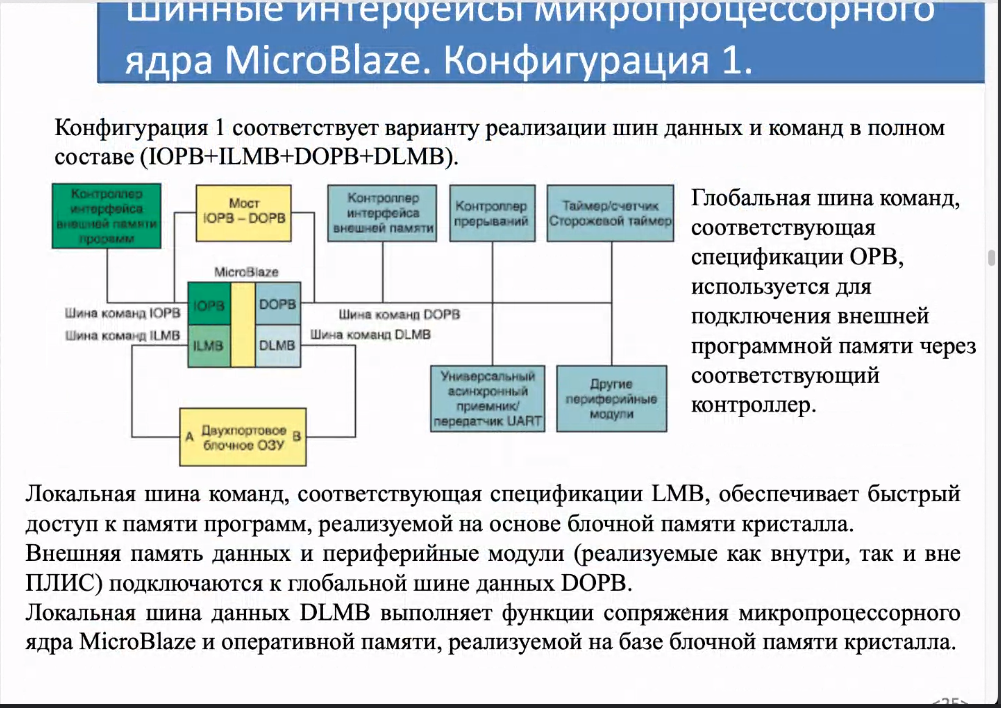

42. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 1

Шинные интерфейсы микропроцессорного ядра MicroBlaze

Каждая из шин микропроцессорного ядра MicroBlaze (шина данных и шина команд) фактически разделяется на две независимые магистрали:

глобальную шину, соответствующую спецификации OPB;

локальную шину, соответствующую спецификации LMB.

В микропроцессорной системе, разрабатываемой на основе ядра MicroBlaze, шины данных и команд могут быть реализованы как в полном составе, так и в виде только локальной LMB или только глобальной магистрали OPB. На рис. 3 показаны шесть возможных вариантов конфигурации шинных интерфейсов микропроцессорного ядра MicroBlaze.

Здесь и далее используется следующая система обозначений: DOPB — шина данных, соответствующая спецификации OPB; DLMB — локальная шина данных, соответствующая спецификации LMB; IOPB — шина команд, соответствующая спецификации OPB; ILMB — локальная шина команд, соответствующая спецификации LMB.

Конфигурация 1 соответствует варианту реализации шин данных и команд в полном составе (IOPB+ILMB+DOPB+DLMB). На рис. 4 показана типовая схема подключения стандартных периферийных модулей и памяти, соответствующая этой конфигурации. Глобальная шина команд, соответствующая спецификации OPB, используется для подключения внешней программной памяти через соответствующий контроллер. Локальнаяшина команд, соответствующая спецификации LMB, обеспечивает быстрый доступ к памяти программ, реализуемой на основе блочной памяти кристалла. Внешняя память данных и периферийные модули (реализуемые как внутри, так и вне ПЛИС) подключаются к глобальной шине данных DOPB. Локальная шина данных DLMB выполняет функции сопряжения микропроцессорного ядра MicroBlaze и оперативной памяти, реализуемой на базе блочной памяти кристалла.

Данную конфигурацию целесообразно использовать в случае, когда необходим большой объем программной и оперативной памяти, превосходящей ресурсы блочной памяти ПЛИС. При этом для хранения критических сегментов программного кода и данных используется блочная память кристалла.

43. Шинные интерфейсы микропроцессорного ядра MicroBlaze. Конфигурация 2 Небольшое введение: Шинные интерфейсы микропроцессорного ядра MicroBlaze

Каждая из шин микропроцессорного ядра MicroBlaze (шина данных и шина команд) фактически разделяется на две независимые магистрали:

глобальную шину, соответствующую спецификации OPB;

локальную шину, соответствующую спецификации LMB.

В микропроцессорной системе, разрабатываемой на основе ядра MicroBlaze, шины данных и команд могут быть реализованы как в полном составе, так и в виде только локальной LMB или только глобальной магистрали OPB. На рис. 3 показаны шесть возможных вариантов конфигурации шинных интерфейсов микропроцессорного ядра MicroBlaze.

Здесь и далее используется следующая система обозначений: DOPB — шина данных, соответствующая спецификации OPB; DLMB — локальная шина данных, соответствующая спецификации LMB; IOPB — шина команд, соответствующая спецификации OPB; ILMB — локальная шина команд, соответствующая спецификации LMB.

Основное:

Конфигурация 2 (IOPB+DOPB+DLMB) оличается от предыдущей отсутствием локальной шины команд ILMB (рис. 5).

При этом программная память полностью выполняется в виде внешнего ППЗУ, взаимодействие с которым осуществляется по глобальной шине команд IOPB через соответствующий контроллер. Сопряжение оперативной памяти и периферийных модулей с микропроцессорным ядром выполняется по той же схеме, что и в конфигурации 1. Конфигурация 2 применяется при больших объемах программного кода и данных, выходящих за пределы ресурсов блочной памяти кристалла FPGA, и реализации памяти программ вне ПЛИС. При использовании данной конфигурации разработчик может задействовать максимальный объем блочной памяти кристалла для организации оперативной памяти с высокой скоростью доступа по шине DLMB.

Дополонительное: