- •Московский государственный институт

- •2 Разработка алгоритма выполнения арифметических операций сложения и вычитания многоразрядных чисел в заданном двоично-десятичном коде

- •2.1 Разработка алгоритма для одноразрядных десятичных чисел, получение величины коррекции и критерия его ввода

- •2.3.7 Примеры сложения

- •3 Разработки функциональной схемы одноразрядного десятичного сумматора комбинационного типа

- •3.1 Разработка оптимальной схемы одноразрядного двоичного сумматора

- •3.2 Разработка схемы коррекции

- •3.3 Разработка схемы одноразрядного десятичного сумматора

- •4. Проектирование дополнительных схем

- •5. Построение функциональной схемы 3-х разрядного десятичного сумматора

- •6. Разработка устройства управления для многоразрядного десятичного сумматора

- •6.1. Разработка входных и выходных регистров хранения числовой информации, участвующей в операции сложения.

- •6.2. Разработка регистра признаков результата.

- •6.3. Проектирование распределителя сигналов

- •6.4 Логическая схема распределителя сигналов

- •7. Получение общей схемы сумматора

- •8. Выводы по работе

5. Построение функциональной схемы 3-х разрядного десятичного сумматора

Обозначим слагаемые, поступающие на вход сумматора:

A = a0 a1 a2 a3 , где a0 — знак числа, ai — десятичная цифра, которая представляется в двоично-десятичном коде следующим образом: ai = αi8 αi4 αi2 αi1 ;

B = b0 b1 b2 b3 , где b0 — знак числа, bi = βi8 βi4 βi2 βi1 .

Результат от сложения обозначим:

C = c0 c1 c2 c3 , где c0 — знак числа, ci = γi8 γi4 γi2 γi1 .

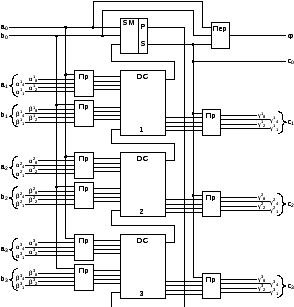

Используя все полученные результаты можно построить структурную схему 3-х разрядного десятичного сумматора (рис. 2.3.15).

Рис. 2.3.15. Логическая схема 3-х разрядного десятичного сумматора

На вход сумматора поступают два трехразрядных десятичных числа. Каждая тетрада этих чисел по отдельности проходит через преобразователь, и каждые две соответствующие тетрады обоих чисел поступают на входы одноразрядных десятичных сумматоров. Эти сумматоры соединены последовательно, аналогично соединению двоичных сумматоров. Кроме того, выход Пi первого сумматора подводится на вход схемы, учитывающей знак суммы. Сигнал с входа P этой схемы подводится на вход первого одноразрядного десятичного сумматора Пi-1. Этим достигается прибавление "1" к младшему разряду при сложении в обратном коде.

Получившиеся на выходах одноразрядных десятичных сумматоров значения пропускаются через преобразователи, и на их выходах получаются значащие разряды искомого числа (суммы). Знак суммы вырабатывается «схемой, учитывающей знак суммы» (SM).

Знак суммы, а также знаки входных чисел, поступают на «схему, фиксирующую переполнение» (Пер).

6. Разработка устройства управления для многоразрядного десятичного сумматора

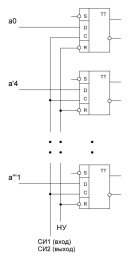

Это устройство вырабатывает 4 синхроимпульса с различными временными задержками между ними (СИ1, СИ2, СИ3 и СИ4). Первый импульс позволяет записать два операнда во входные регистры. Как только эта информация будет записана, величины появляются на входах сумматора, и сумматор начинает производить обработку информации. Второй импульс позволяет записать информацию в выходной регистр, когда результат получен. Третий импульс позволяет получить в регистре признаков все признаки результатов. И четвертый импульс останавливает процесс вычислений. Между импульсами существуют временные интервалы, во время которых обрабатывается информация.

6.1. Разработка входных и выходных регистров хранения числовой информации, участвующей в операции сложения.

Регистры входов и выхода имеют одинаковую структуру и строятся на синхронных двухтактных D триггерах с асинхронными установочными входами RиS. Каждый регистр содержит по 13 триггеров (12 для 3-х тетрад и один знаковый).

6.2. Разработка регистра признаков результата.

Регистр признаков хранит информацию о результате работы устройства. Регистр состоит из 4 триггеров. Первый содержит 1, если результат отрицательный, второй – положительный, третий – результат равен нулю. Четвертый триггер переходит в единичное состояние при возникновении переполнения разрядной сетки (при этом остальные триггеры переводятся в 0-е состояния).