Курсовая по организации ЭВМ

.docМосковский институт электроники и математики

(Технический университет)

Каф.ВСиС

КУРСОВАЯ РАБОТА

По дисциплине «Организация ЭВМ и периферийные устройства»

На тему

МОДЕЛИРОВАНИЕ цикла ВЫПОЛНЕНИЯ КОМАНДЫ

32-РАЗРЯДНЫМ ПРОЦЕССОРОМ

Выполнил студент группы С-43 Голенок Е.А.

Руководитель доцент каф. ВСиС, доц., к.т.н. Иванова Е.М.

Оценка__________ дата «___»__________________2012г.

|

Вариант № 8 |

|||||||

|

Команда |

CALL |

||||||

|

Режим адресации операнда |

- |

||||||

|

Режим страничной переадресации |

Базовый |

||||||

|

Тип АЛУ |

Магистральная |

||||||

|

Тип TLB (КЭШ) |

Полностью ассоциативный |

||||||

|

оценки |

|||||||

|

Техническое задание |

А1 Обобщённый алгоритм |

А2 Алгоритм вычисл. линейного адреса |

А3 Алгоритм вычисл. физ. адреса |

А4 Алгоритм выполн. операции |

Итоговая |

Защита

|

|

|

|

|

|

|

|

|

|

|

Москва 2012

Содержание

|

Техническое задание…………………………………………………………… |

3 |

|

1 Обобщенный алгоритм……………………………………………………… |

5 |

|

2 Алгоритм вычисления Линейного адреса……………………………………………………………… |

6 |

|

3 Алгоритм вычисления Физического адреса…………………………………………………………… |

7 |

|

4 Алгоритм выполнения Операции………………………………………………………………………… |

8 |

-

Техническое задание

-

Задание на курсовую работу

Разработать схемы блоков процессора (АЛУ и TLB) и алгоритмы цикла выполнения команды CALL PROC1 с относительной адресацией [EIP+адрес Proc1], для 32-разрядного процессора Intel в защищенном режиме работы с базовым механизмом страничной переадресации и с полностью ассоциативным распределением строк в КЭШ, с использованием магистрального АЛУ.

-

Постановка задачи

-

Дано:

-

Режим работы процессора - защищенный

Режим страничной переадресации – базовый

Системные адреса – с адресом CR3

Команда CALL – вызов процедуры или переключение задачи

Установленные биты служебных регистров – PE=1, VM=0

Тип команды – передача управления внутри сегмента кода

Количество операндов – 2 (1 явный + 1 неявный)

Местоположение, размер и режим адресации операнда:

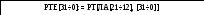

операнд_1 – два байта, const в команде

операнд_2 – четыре байта, в регистре EIP[31÷0]

Количество обращений в ОП-1(за командой)

Тип распределения данных в КЭШ (буфере TLB) –полностью ассоциативное,

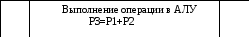

Тип структуры АЛУ – Магистральная.

|

0 7 |

16 31 |

|

КОП CALL |

смещение |

|

1 байт

|

2 |

0

7 0 15

7 0 15

Итого: 3 байта

Загружается в регистр команды IR[7÷0]

З агружается

в регистр адреса ADR[15÷0]

агружается

в регистр адреса ADR[15÷0]

2.1 Требуется:

Составить:

-

схему структуры АЛУ для выполнения заданной в команде операции,

-

схему размещения строк в TLB (КЭШ),

-

схему режима страничной переадресации (использовать готовую),

алгоритмы цикла выполнения команды в процессоре:

-

Обобщённый алгоритм

-

Алгоритм вычисления линейного адреса

-

Алгоритм вычисления физического адреса (с приложенной схемой механизма страничной переадресацией и схемой распределения строк в TLB)

-

Алгоритм выполнения операции в АЛУ (с приложенной схемой структуры АЛУ)

2.2 Ограничения

#GP - General Protection, общее исключение защиты.

-

Эффективный адрес команды с учётом ее размера должен находиться в пределах сегмента CS,

#PF - Page Fault, исключение по отказу страницы.

-

Наличие страницы в ОП, к которой происходит обращение

Алгоритм №1. Обобщённый алгоритм.

A2

A3

Фаза 1:

выборка

команды

-

Преобразование

LA

в ФА

Преобразование

LA

в ФАПроверка ФA

(

наличие

страницы в ОП)

наличие

страницы в ОП)

-

ША[31

0]=

ФА[31

0]=

ФА[31 0]

0]

Фаза 2:

выборка

операндов

|

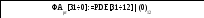

P1[15 |

Фаза 3:

выполнение

операции

A4

|

P2[31 |

EIP[31![]() 0]=Р3[31

0]=Р3[31![]() 0]

0]

AR – регистр адреса основной памяти

IR – регистр команды

СОЗУ – внутренняя память процессора

УУП – устройство управления памятью

ЛА – логический адрес

LA – линейный адрес

ФА – физический адрес

Алгоритм №2. Вычисление линейного адреса команды

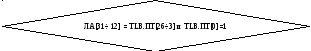

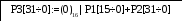

Алгоритм №3. Алгоритм вычисления физического адреса

TLB

Кэш-промах

TLB

Кэш-попадание

ЛА[31÷12]=BAстраницы

Нет

Да

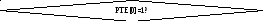

Алгоритм №4. Алгоритм выполнения операции

байт

байт