- •Московский государственный институт

- •2 Разработка алгоритма выполнения арифметических операций сложения и вычитания многоразрядных чисел в заданном двоично-десятичном коде

- •2.1 Разработка алгоритма для одноразрядных десятичных чисел, получение величины коррекции и критерия его ввода

- •2.3.7 Примеры сложения

- •3 Разработки функциональной схемы одноразрядного десятичного сумматора комбинационного типа

- •3.1 Разработка оптимальной схемы одноразрядного двоичного сумматора

- •3.2 Разработка схемы коррекции

- •3.3 Разработка схемы одноразрядного десятичного сумматора

- •4. Проектирование дополнительных схем

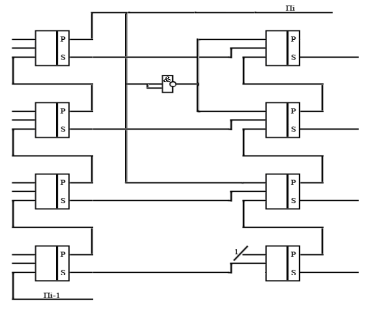

- •5. Построение функциональной схемы 3-х разрядного десятичного сумматора

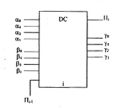

- •6. Разработка устройства управления для многоразрядного десятичного сумматора

- •6.1. Разработка входных и выходных регистров хранения числовой информации, участвующей в операции сложения.

- •6.2. Разработка регистра признаков результата.

- •6.3. Проектирование распределителя сигналов

- •6.4 Логическая схема распределителя сигналов

- •7. Получение общей схемы сумматора

- •8. Выводы по работе

3.2 Разработка схемы коррекции

Схема коррекции вырабатывает сигнал введения корректирующей величины. Корректирующая величина должна вводится всегда. Если Пi=0, то она будет равна 1101. Если же Пi=1, то 0011. Таким образом:

|

Пi |

K8 |

K4 |

K2 |

K1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

K8

=

K4

= Пi

K2 = Пi

К1 = 1

3.3 Разработка схемы одноразрядного десятичного сумматора

4. Проектирование дополнительных схем

Все числа, которые приходят на входы сумматоры, представлены в прямом коде. Для выполнения операции сложения (вычитания) с этими величинами необходимо представить их в обратном коде. Для этого необходимо разработать преобразователь чисел из прямого кода в обратный. Причем нетрудно заметить, что преобразователь из обратного кода в прямой будет иметь ту же схему.

Пусть на вход преобразователя приходят одноразрядные десятичные числа, закодированные с помощью двоичных символов и имеющие условные обозначения a0 — знак числа, α8 α4 α2 α1 — само число.

На выходе будет a0 — знак числа (он не изменяется), a8’ a4’ a2’ a1’

Зная правила записи числа в обратном коде, составим таблицу истинности преобразователя.

Таблица истинности преобразователя

|

a0 |

a8 |

a4 |

a2 |

a1 |

a8’ |

a4’ |

a2’ |

a1’ | |

|

0 |

0 |

0 |

0 |

0 |

н |

н |

н |

н | |

|

0 |

0 |

0 |

0 |

1 |

н |

н |

н |

н | |

|

0 |

0 |

0 |

1 |

0 |

н |

н |

н |

н | |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 | |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 | |

|

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 | |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 | |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 | |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 | |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 | |

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 | |

|

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 | |

|

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 | |

|

0 |

1 |

1 |

0 |

1 |

н |

н |

н |

н | |

|

0 |

1 |

1 |

1 |

0 |

н |

н |

н |

н | |

|

0 |

1 |

1 |

1 |

1 |

н |

н |

н |

н | |

|

1 |

0 |

0 |

0 |

0 |

н |

н |

н |

н | |

|

1 |

0 |

0 |

0 |

1 |

н |

н |

н |

н | |

|

1 |

0 |

0 |

1 |

0 |

н |

н |

н |

н | |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 | |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 | |

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 | |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 | |

|

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 | |

|

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 | |

|

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 | |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 | |

|

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 | |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 | |

|

1 |

1 |

1 |

0 |

1 |

н |

н |

н |

н | |

|

1 |

1 |

1 |

1 |

0 |

н |

н |

н |

н | |

|

1 |

1 |

1 |

1 |

1 |

н |

н |

н |

н | |

|

a8’ |

a4’ |

a2’ |

a1’ |

как переключательные функции, зависящие от 5 аргументов. Эти функции не полностью определенные, так как на 0-2, 13-18 и 29-31 наборах их значения не определены. В коде 8421+3 комбинации двоичных сигналов, которые записаны на данных наборах, не существуют.

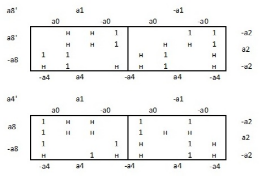

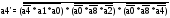

Для построения схемы получим МДНФ всех переключательных функций с помощью диаграмм Вейча:

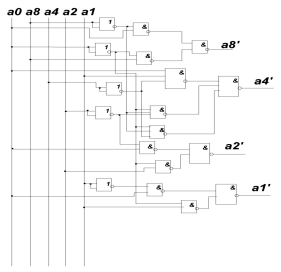

По полученным аналитическим выражениям построим функциональную схему преобразователя (рис. 2.3.12,а).

рис. 2.3.12,а функциональная схема преобразователя

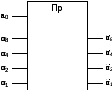

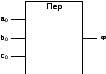

В дальнейшем данную схему будем изображать следующим образом (рис. 2.3.12,б).

Рис. 2.3.12,б. Условное обозначение логической схемы преобразователя.

При наступлении переполнения разрядной сетки результат получается неправильным. Чтобы фиксировать наступление переполнения необходимо спроектировать специальную схему. В основу проектирования этой схемы положено правило наступления переполнения разрядной сетки. Оно гласит: переполнение наступает:

при сложении двух положительных величин результат получается отрицательным;

при сложении двух отрицательных величин результат получается положительным.

Обозначим:

а0 и b0 — знаки слагаемых;

c0 — знак результата;

φ — знак переполнения.

По правилам переполнения составим таблицу истинности для переключательной функции φ.

Таблица 2.3.4.

Таблица истинности для функций φ

|

а0 |

b0 |

c0 |

φ |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

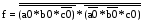

Для построения схемы получим МДНФ переключательной функции с помощью диаграммы Вейча:

Рис. 2.3.13. Диаграммы Вейча для функции φ.

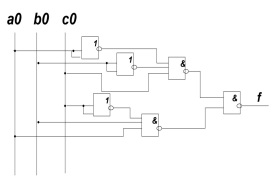

По полученному выражению построим функциональную схему, фиксирующую переполнение (рис. 2.3.14,а).

Рис. 2.3.14,а Логическая схема функции переполнения

Условное изображение этой функциональной схемы будет следующим (рис. 2.3.14,б).

Рис. 2.3.14,б. Условное обозначение логической схемы, фиксирующей переполнение.

Правило сложения чисел в обратном коде гласит, что при выполнении операции знаковые разряды участвуют в сложении на ровне с остальными разрядами. При этом учитывается перенос в знаковый разряд и перенос из знакового разряда. Поэтому для получения знака результата можно использовать одноразрядный двоичный сумматор.