- •Московский государственный институт электроники и математики

- •Расчет топологии n-p-n транзистора

- •1.2. Диоды

- •1.3. Резисторы Тонкопленочные резисторы

- •Диффузионные резисторы

- •1.4. Мдп транзисторы

- •Разновидности мдп – транзисторов

- •Зависимость порогового напряжения от электрофизических характеристик

- •Динамические параметры

- •1.5. Приборы и ис на арсениде галлия

- •2. Логические схемы

- •2.1. Общие сведения

- •Классификация логических схем

- •Основные параметры и характеристики логических элементов

- •I – зона логического нуля по выходу,

- •II – зона логической единицы по выходу,

- •III – зона неопределенности.

- •I – зона логического нуля по выходу,

- •II – зона логической единицы по выходу,

- •III – зона неопределенности.

- •2.2. Транзисторно – транзисторные логические схемы (ттл).

- •2.3. Элементы эмиттерно – связанной логики (эсл).

- •2.4. Кмоп

- •Инвертор

- •2.4. Логические схемы на арсениде галлия.

- •3. Расчет схем в программе pSpice

- •3.1. Краткие сведения

- •Создание входного файла для программы pspice

- •Описание элементов схемы

- •Описания источников напряжения

- •Описание источников тока

- •Описание диода

- •Описание биполярного транзистора

- •Описание мдп транзистора

- •Арсенид-галлиевый полевой транзистор с каналом n-типа

- •Директивы управления заданием

- •3.2. Примеры расчетов Простейшие схемы

- •Расчет ттл схемы со сложным инвертором

- •3.3. Графический процессор probe

- •Литература

Инвертор

Пусть

![]() следовательно n-канальный

следовательно n-канальный![]() тогда

тогда![]() следовательно p-канальный

следовательно p-канальный![]() открыт и работает в крутой области

выходной характеристики, то

открыт и работает в крутой области

выходной характеристики, то![]() .

.

Пусть

![]() растет, когда

растет, когда![]() ,

,![]() открывается и в схеме начинает течь

ток.

открывается и в схеме начинает течь

ток.

Пусть

![]() ,

тогда

,

тогда![]() -

открыт (

-

открыт (![]() ),

),![]() -

закрыт

-

закрыт![]() ,

если

,

если![]() и

и![]() - что то же самое.

- что то же самое.

Когда

![]() достигает

достигает![]() транзистор

транзистор![]() ,

запирается и устанавливается

,

запирается и устанавливается![]()

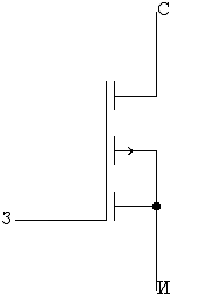

Рис. 37. Принципиальная схема КМОП инвертора

Рис. 38. Передаточная характеристика

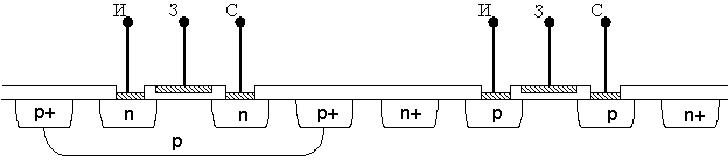

Рис. 39. Структура КМОП инвертора

|

p-канальный |

n-канальный

|

![]() пороговое

напряжение

пороговое

напряжение

![]()

![]()

Рис. 40. Обозначения транзисторов

Как правило, к выходу логической схемы подключается вход такой же логической схемы, поэтому в статике ток в КМОП схеме может течь только через транзисторы (вход следующей схемы – затворы её транзисторов, через них ток не течёт):

когда

на выходе логический 0, заперт

![]()

![]() ,

,

когда

на выходе логическая 1, заперт

![]()

![]() .

.

Требования к транзисторам КМОП схем:

В КМОП схемах должно соблюдаться равенство по модулю пороговых напряжений n- и p-канальных транзисторов

Необходимо равенство удельной крутизны n- и p-канальных транзисторов, из-за чего отношение ширины n- и p-канальных транзисторов пропорционально отношению подвижности электронов и дырок (при равной длине канала).

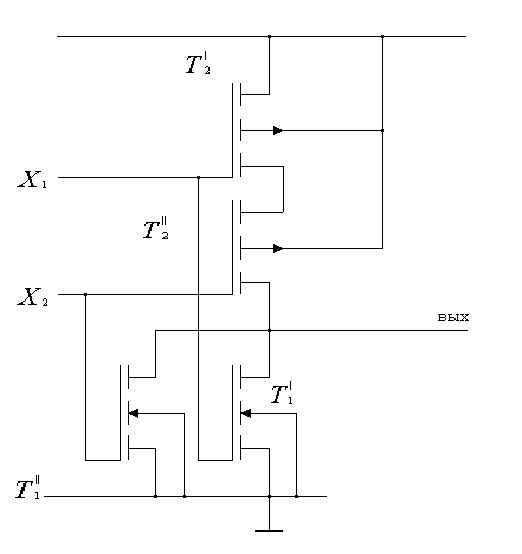

Схема ИЛИ-НЕ

|

|

| |||

|

X1 |

X2 |

Y |

| |

|

0 |

0 |

1 | ||

|

0 |

1 |

0 | ||

|

1 |

0 |

0 | ||

|

1 |

1 |

0 | ||

|

| ||||

|

| ||||

|

| ||||

|

| ||||

|

| ||||

|

| ||||

Рис. 41. Схема ИЛИ-НЕ

Схема И-НЕ

|

|

X1 |

X2 |

Y |

|

|

0 |

0 |

1 |

| |

|

0 |

1 |

1 |

| |

|

1 |

0 |

1 |

| |

|

1 |

1 |

0 |

| |

|

| ||||

|

| ||||

|

| ||||

|

| ||||

|

| ||||

Рис. 42. Схема И-НЕ

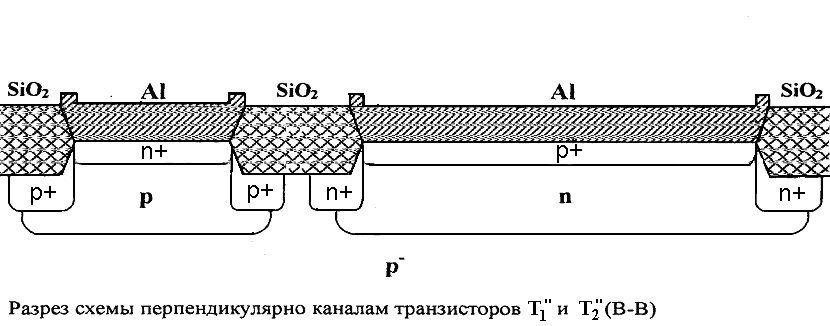

Рис. 43. Сечение структуры

Рис. 44. Сечение структуры

Рис. 45. Сечение структуры

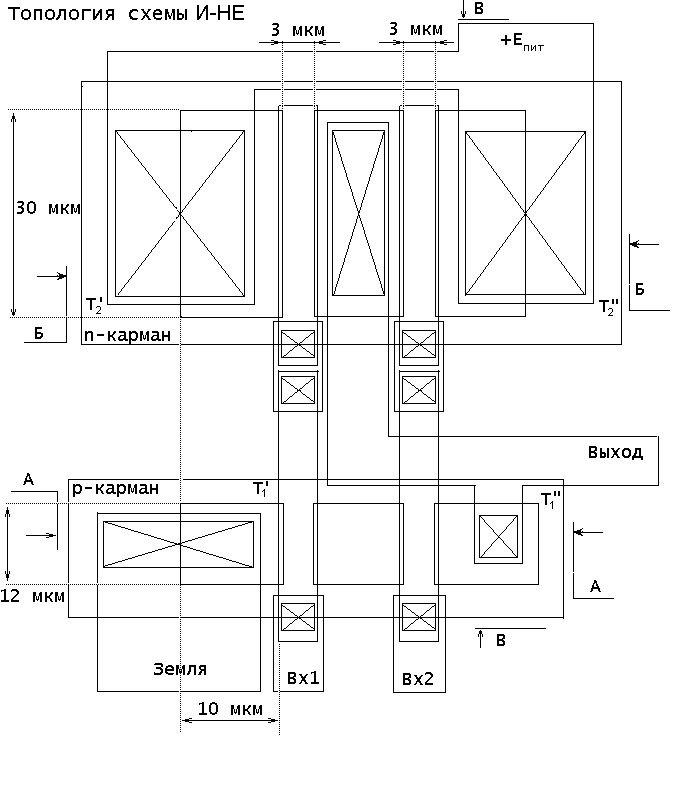

Рис. 46. Топология схемы И-НЕ

Проектирование КМОП схем.Рекомендуется длину канала транзисторов обоих типов выбрать равной двум минимальным размерам, ширину каналаn-канального транзистора выбрать в 3 раза больше длины (6 минимальных размеров), тогда ширина каналаp-канального транзистора будет в 3 раза больше ширины каналаn-канального(18 минимальных размеров). Размеры областей стока и истока определяются шириной канала и условиями размещения контактов: контакт занимает всю площадь стока и истока, отступая от их краев на минимальный размер, ширина контакта не может быть меньше минимального размера. Когда геометрические размеры выбраны, делается расчет параметров транзисторов по формулам, приведенным выше, а после этого – расчет схемы с помощью программыPSPICE. Исходя из анализа результатов расчета схемы делаются изменения в размерах транзисторов.

2.4. Логические схемы на арсениде галлия.

В настоящее время наибольшее распространение получили три типа логических винтелей для быстродействующих ИС на GaAs.

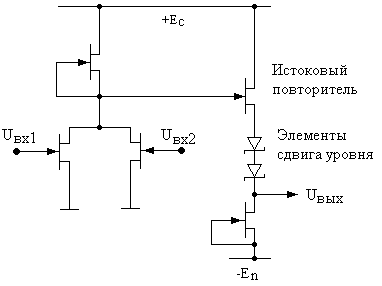

1) Логический вентиль с буферным каскадом (ЛБК), разработанный фирмой Hewlett Packard является наиболее быстродействующим t3=33 пс/вент, однако потребляет достаточно большую мощность S-10 мВт/вент. +EC=+4.5 B, -EП=-3 B, U1=+0.5 B, U0=-2 B.

Рис. 47. Вентиль ЛБК.

В ЛБК применяют нормально открытые полевые транзисторы, поэтому для согласования входных и выходных уровней напряжения требуется введение в схему дополнительных элементов для сдвига уровней. Эти элементы неизбежно вносят дополнительную задержку сигнала и расход мощности. Из-за высокой потребляемой мощности и большого количества элементов на ЛБК возможно создание БИС со степенью интеграции до 103 вент.

Схемные варианты ЛБК.

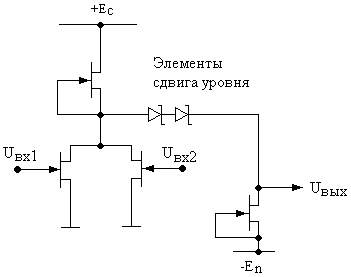

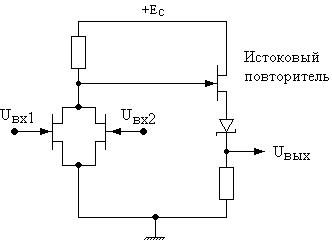

Рис. 48. Вентиль ЛБК без истокового повторителя.

C целью снижения уровня потребляемой мощности исключен истоковый повторитель. Однако, уменьшается коэффициент разветвления по выходу: Kвых=2. Этот вентиль чаще всего применяется для построения триггерных схем.

Для увеличения быстродействия в схему введён диод ДУСК, выполняющий функцию ускоряющего конденсатора. Обратно смещенный диод действует как ёмкость и шунтирует при переключении буферный каскад сдвига уровня, что резко повышает быстродействие. Однако для эффективной работы площадь диода должна быть большой, чтобы получить требуемую величину ёмкости.

Рис. 49. Вентиль ЛБК с ускоряющим диодом.

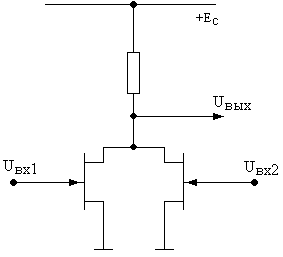

2) Логические вентили на основе ПТШ с диодами Шотки (ЛДШ), созданные фирмой Rockwell. Потребляют в 5 раз меньшую мощность, но имеют в 2 раза худшее быстродействие. Содержит миниатюрные ДШ размером (1*2мкм2) для выполнения логических операций ИЛИ и для сдвига уровней сигнала. Функцию инвертора в ЛДШ выполняет второй каскад на нормально открытые полевые транзисторы с затворами Шотки. Благодаря небольшой потребляемой мощности и малым размерам диодов на этих схемах можно создавать БИС с плотностью интеграции 104 вентилей. +EC=+2 B, -EП=-1.5 B.

Рис. 50. Вентиль ЛДШ.

3) Логические вентили с непосредственными связями (ЛНС), разработанные фирмой McDounell Douglas. Реализованы на НЗ ПТ с р-n переходом. Характеризуется самой низкой величиной потребляемой мощности Pпотр=50 мкВт/вент, t3 в 2-4 раза больше чем у ЛБК. Занимает очень малую площадь на кристалле – 200 мкм2/вент. Для надёжной работы требуется, чтобы Ес не превышало 1В. Очень критичны к значению Uпор. +EC=+1...+2 B.

Рис. 51. Вентиль ЛНС.

Компромиссный вариант вентилей между ЛНС и ЛБК.

Средняя скорость переключения, средняя потребляемая мощность. Uпор=0В, но требования к этому параметру значительно понижены по сравнению с ЛНС. +EC=+2.5 B.

Рис. 52. Вентиль ЛНС с истоковым повторителем.