- •Московский государственный институт электроники и математики

- •Расчет топологии n-p-n транзистора

- •1.2. Диоды

- •1.3. Резисторы Тонкопленочные резисторы

- •Диффузионные резисторы

- •1.4. Мдп транзисторы

- •Разновидности мдп – транзисторов

- •Зависимость порогового напряжения от электрофизических характеристик

- •Динамические параметры

- •1.5. Приборы и ис на арсениде галлия

- •2. Логические схемы

- •2.1. Общие сведения

- •Классификация логических схем

- •Основные параметры и характеристики логических элементов

- •I – зона логического нуля по выходу,

- •II – зона логической единицы по выходу,

- •III – зона неопределенности.

- •I – зона логического нуля по выходу,

- •II – зона логической единицы по выходу,

- •III – зона неопределенности.

- •2.2. Транзисторно – транзисторные логические схемы (ттл).

- •2.3. Элементы эмиттерно – связанной логики (эсл).

- •2.4. Кмоп

- •Инвертор

- •2.4. Логические схемы на арсениде галлия.

- •3. Расчет схем в программе pSpice

- •3.1. Краткие сведения

- •Создание входного файла для программы pspice

- •Описание элементов схемы

- •Описания источников напряжения

- •Описание источников тока

- •Описание диода

- •Описание биполярного транзистора

- •Описание мдп транзистора

- •Арсенид-галлиевый полевой транзистор с каналом n-типа

- •Директивы управления заданием

- •3.2. Примеры расчетов Простейшие схемы

- •Расчет ттл схемы со сложным инвертором

- •3.3. Графический процессор probe

- •Литература

1.4. Мдп транзисторы

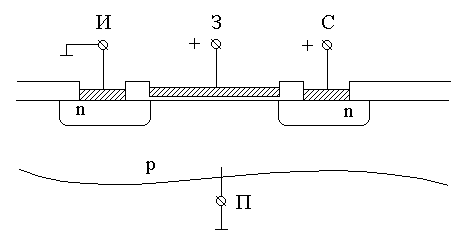

Рис. 14. Структура МДП транзистора

Пороговое напряжение UЗИ ПОР – при котором концентрация электронов в канале около поверхности Si - SiO2 равна концентрации дырок в подложке p-типа, т.е. канал образуется, если UЗ > UПОР.

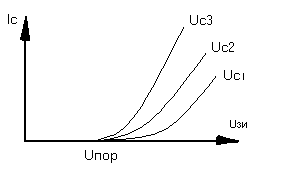

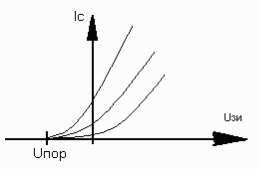

Рис. 15. Выходная характеристика

В линейной (крутой, триодной) области:

![]()

Формула верна для UЗ >UПОР, UC<UЗ–UПОР, при UC=0 IC=0

Если

UC

мало и выполняется неравенство

![]() ,

тогда:

,

тогда:

![]() т.е.

Ic

- линейная функция Uc,

здесь: W - ширина канала, L - длина канала,

µns-подвижность

электронов вблизи поверхности(0,5 µn

– в глубине). OX

- диэлектрическая проницаемость окисла,

lOX

- толщина

окисла,

т.е.

Ic

- линейная функция Uc,

здесь: W - ширина канала, L - длина канала,

µns-подвижность

электронов вблизи поверхности(0,5 µn

– в глубине). OX

- диэлектрическая проницаемость окисла,

lOX

- толщина

окисла,

![]() -

удельная емкость структуры затвор –

канал, Ф/м2,

-

удельная емкость структуры затвор –

канал, Ф/м2,

![]() .

.

При

UC=UЗ-UПОР

канал вблизи стока исчезает и транзистор

работает в области насыщения (пологой,

пентодной) с перекрытым каналом

![]()

Подставим это значение в формулу для IC:

![]()

т.е. в области насыщения ток стока IC от напряжения на стоке UC не зависит.

С увеличением UC канал вблизи стока перекрывается больше и больше: так как расширяется обедненный слой стокового p-n перехода, следовательно, длина канала L уменьшается, следовательно, ток IC растет, характеристики в области насыщения имеют небольшой наклон.

Крутизна:

![]()

![]()

![]()

Удельная

крутизна:

![]() - является параметром транзистора.

- является параметром транзистора.

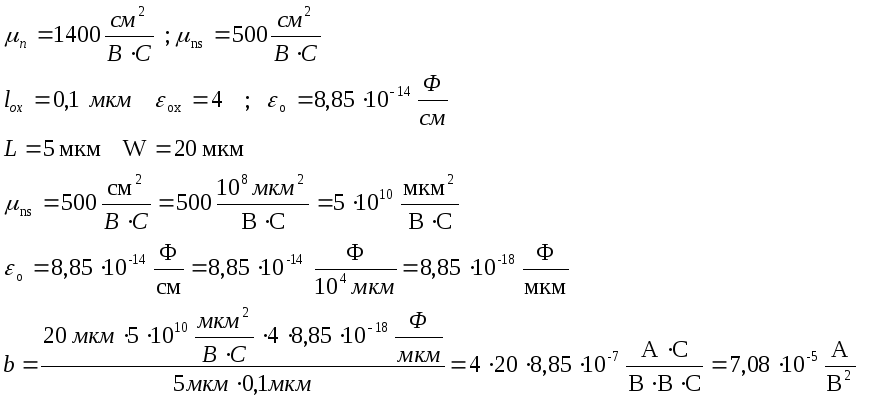

Оценим:

![]()

В PSpice используется параметр, называемый коэффициент крутизны:

![]() .

.

kp

является параметром микросхемы в целом,

а не отдельного транзистора, так как

![]() и

и![]() одинаковы для всей микросхемы, а длина

и ширина канала являются параметрами

транзистора.

одинаковы для всей микросхемы, а длина

и ширина канала являются параметрами

транзистора.

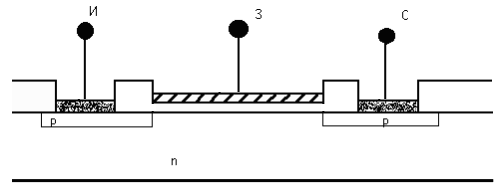

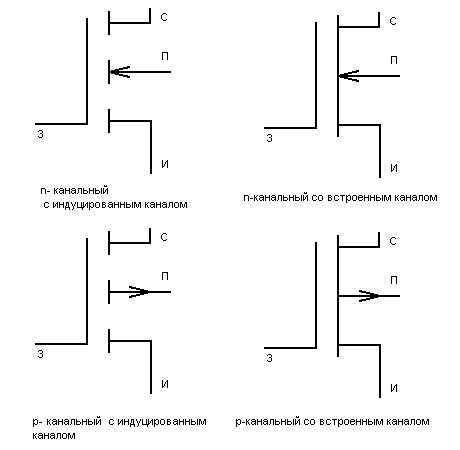

Разновидности мдп – транзисторов

По типу проводимости канала

n-канальный (рассмотрен)

p-канальный

Рис. 16. p-канальный МДП транзистор с индуцированным каналом

По характеру канала: транзисторы с индуцированным каналом

когда

![]() канала нет, канал появляется при

канала нет, канал появляется при![]() :

:

![]() n-

канал

n-

канал

![]() p- канал.

p- канал.

Именно такие транзисторы рассмотрены выше.

Рис. 17. Входная характеристика n- канального транзистора с индуцированным каналом.

Рассмотрим транзистор со встроенным каналом:

Рис. 18. Структура n-канального МДП транзистора (аналогично для p-канального)

Рис. 19. Входная характеристика n- канального транзистора со встроенным каналом.

Рис. 20. Обозначения различных МДП транзисторов

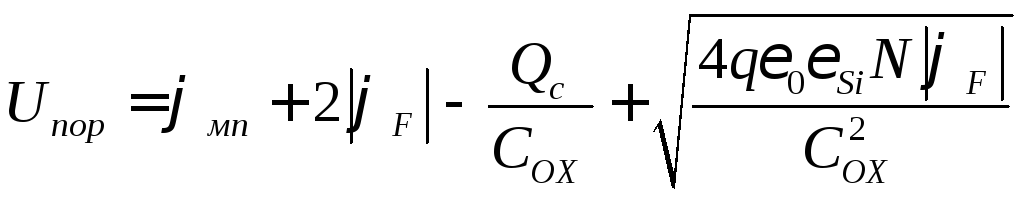

Зависимость порогового напряжения от электрофизических характеристик

Подложка p-типа (n-канальная структура):

;

;

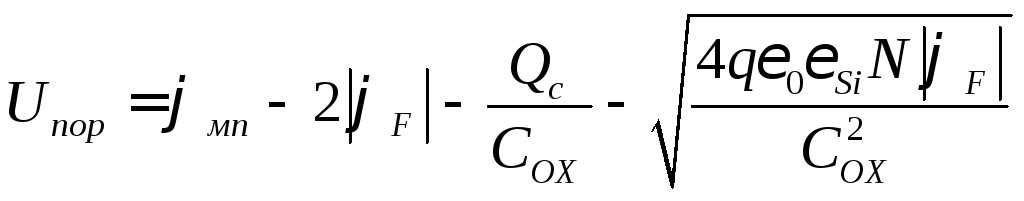

Подложка n-типа (p-канальная структура):

;

;

МП - разность работ выхода электронов из металла и полупроводника:

для подложки p-типа:

МП=МПС‑|F|

для подложки n-типа:

МП=МПС+|F|

МПС=‑0.6 В - разность работ выхода электронов из алюминия и кремния с собственным типом проводимости.

|F| - абсолютное значение потенциала Ферми, измеряемого в В, или уровня Ферми в эВ:

![]() .

.

Например:

![]()

тогда

разность работ выхода:

![]() .

.

![]() -

плотность заряда поверхностных состояний

-

плотность заряда поверхностных состояний

![]()

N – концентрация примеси в подложке.

Для поликремниевого затвора:

Разность работ выхода из затвора и подложки:

n-канальный транзистор – подложка p-типа, затвор легирован n-примесью

![]()

p-канальный транзистор – подложка n-типа, затвор легирован p-примесью

![]()

В SPICE пороговое напряжение называется vto. Расчет параметров МОП-транзисторов подробно описан в [1 - §8.6, 11.3; 2 - §9.3].