- •Московский государственный институт электроники и математики

- •Расчет топологии n-p-n транзистора

- •1.2. Диоды

- •1.3. Резисторы Тонкопленочные резисторы

- •Диффузионные резисторы

- •1.4. Мдп транзисторы

- •Разновидности мдп – транзисторов

- •Зависимость порогового напряжения от электрофизических характеристик

- •Динамические параметры

- •1.5. Приборы и ис на арсениде галлия

- •2. Логические схемы

- •2.1. Общие сведения

- •Классификация логических схем

- •Основные параметры и характеристики логических элементов

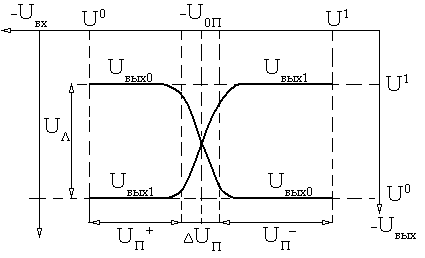

- •I – зона логического нуля по выходу,

- •II – зона логической единицы по выходу,

- •III – зона неопределенности.

- •I – зона логического нуля по выходу,

- •II – зона логической единицы по выходу,

- •III – зона неопределенности.

- •2.2. Транзисторно – транзисторные логические схемы (ттл).

- •2.3. Элементы эмиттерно – связанной логики (эсл).

- •2.4. Кмоп

- •Инвертор

- •2.4. Логические схемы на арсениде галлия.

- •3. Расчет схем в программе pSpice

- •3.1. Краткие сведения

- •Создание входного файла для программы pspice

- •Описание элементов схемы

- •Описания источников напряжения

- •Описание источников тока

- •Описание диода

- •Описание биполярного транзистора

- •Описание мдп транзистора

- •Арсенид-галлиевый полевой транзистор с каналом n-типа

- •Директивы управления заданием

- •3.2. Примеры расчетов Простейшие схемы

- •Расчет ттл схемы со сложным инвертором

- •3.3. Графический процессор probe

- •Литература

2.3. Элементы эмиттерно – связанной логики (эсл).

Элементы эмиттерно – связанной логики (ЭСЛ).

ЭСЛ – элементы отличаются высоким быстродействием (t3≤1 нс) и поэтому они являются в настоящее время основной элементной базой высокопроизводительных ЭВМ.

Основой ЭСЛ – элементов является переключателем тока (токовые ключи).

Принцип действия переключателя тока.

U0,U1<0, U0<U1, т.о. |U0|>|U1|.

Пусть хотя бы на один вход подан высокий потенциал Uвх>-Uоп, тогда соотв. Т1 открыт, вычислим напряжение БЭ транзистора Т2: Uбэ2=-Uоп-Uэ=-Uоп-(Uвх-U*)=U*-(Uоп+Uвх)<U* Uэ=Uвх-U* – потенциал эмиттеров. Следовательно Т2 закрыт, ток источника тока I0 протекает через входное плечо переключателя тока, на входе F0 устанавливается низкий потенциал U0=-I0R1 , в правом “опорном” плече ток не течет и на выходе. F1 потенциал равен 0 U1=0.

Если на все переключатели тока подан низкий потенциал Uвх<-Uоп , то транзисторы Т1 закрыты, Т2 открыт и на выходе F0-U1 , на F1-U0 .

Л![]() огический

перепад:

огический

перепад:

_![]()

![]() _

_

![]()

![]()

Базовый элемент ЭСЛ.

П![]() усть

на всех входах

усть

на всех входах

![]() и оба Т1 закрыты

и оба Т1 закрыты

![]() ,

,![]()

![]() ,

,

![]() ток

нагрузки,

ток

нагрузки,

![]() ток

источника тока T5-R3,

на выходе 0 высокий потенциал

ток

источника тока T5-R3,

на выходе 0 высокий потенциал

![]()

В

этом случае Т2 открыт и через R1

в его коллекторе цепи течет ток

![]()

![]()

![]() коэффициент передачи тока транзистора.

коэффициент передачи тока транзистора.

![]() ,

где

,

где![]()

На

выходе 1 – низкий потенциал

![]() .

Токи, задаваемые транзисторными

источниками тока

.

Токи, задаваемые транзисторными

источниками тока![]() ,

,

![]() .

Когда

.

Когда

![]() (хотя

бы один) открывается Т1 и закрывается

Т2,

(хотя

бы один) открывается Т1 и закрывается

Т2,![]() течет

через Т1 и

течет

через Т1 и![]()

Ограничение

на максимум логического перепада![]() определяется

из условия ненасыщенного режима

транзисторов Т1:

определяется

из условия ненасыщенного режима

транзисторов Т1:![]() .

Чтобы Т1 не был насыщен

.

Чтобы Т1 не был насыщен![]() (схемы

нагружены друг на друга). В этом режиме

(схемы

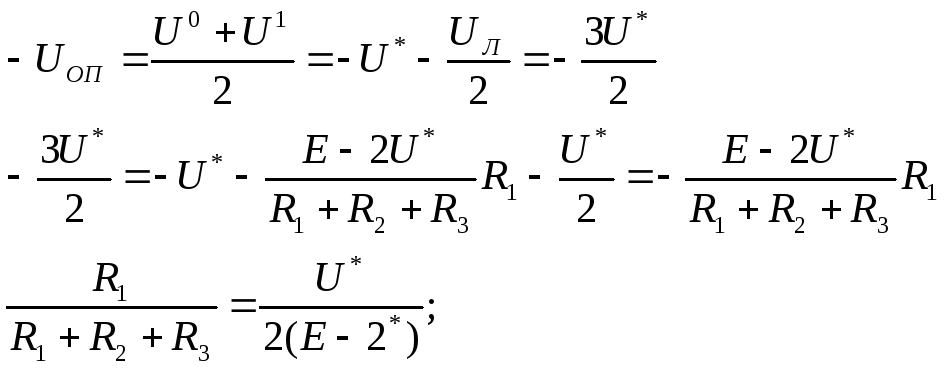

нагружены друг на друга). В этом режиме![]() Опорное напряжение:

Опорное напряжение:

Входные

токи: при

![]() , гдеl

– число открытых входов (

, гдеl

– число открытых входов (![]() ).

При

).

При

![]()

Макс

ток нагрузки

![]() определяется исходя из допустимого

снижения уровня

определяется исходя из допустимого

снижения уровня

![]() при

подключении нагрузки:

при

подключении нагрузки:![]() ,l=1

,l=1

![]()

Мощность

![]()

ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ И НАПРЯЖЕНИЯ СМЕЩЕНИЯ.

Чтобы:

![]() из

условия:

из

условия:

![]() -

для стабильности

-

для стабильности![]() ;

один источник на 5-10 ЭСЛ - элементов.

;

один источник на 5-10 ЭСЛ - элементов.

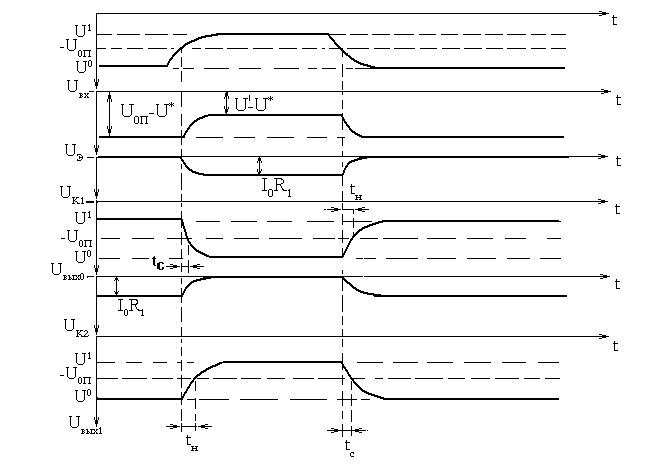

Пусть

![]() меняется

от

меняется

от![]() ,

транзистор Т1 открывается, потенциал

коллектора Т1:

,

транзистор Т1 открывается, потенциал

коллектора Т1:

![]()

![]() -

емкости коллекторов Т1 и Т3,

-

емкости коллекторов Т1 и Т3,

![]() -

паразитная емкость межсоединений.

-

паразитная емкость межсоединений.![]() -

емкость нагрузки,

-

емкость нагрузки,![]() -

паразитная емкость.

-

паразитная емкость.

Т.К.

![]() достаточно

мала, а емкость нагрузки

достаточно

мала, а емкость нагрузки![]() велика, потенциал

велика, потенциал![]() не

успевает следовать за уменьшением

не

успевает следовать за уменьшением![]() и

Т3 запирается, поэтому емкость

и

Т3 запирается, поэтому емкость![]() разряжается током

разряжается током![]() (ток

эмиттерного повторителя).

(ток

эмиттерного повторителя).![]()

Снижение

от

![]() происходит за время спада

происходит за время спада![]() ,когда

,когда![]() напряжение на эмиттерном переходе Т3

напряжение на эмиттерном переходе Т3

![]() и

Т3 открывается.

и

Т3 открывается.

Пусть

![]() меняется

от

меняется

от![]() ,

Т1 запираются и

,

Т1 запираются и![]() возрастает

вследствие заряда емк. С1 черезR1:

возрастает

вследствие заряда емк. С1 черезR1:

![]() .

Через открытый Т3 изменения

.

Через открытый Т3 изменения![]() передаются на выходе схемы.

передаются на выходе схемы.![]() увеличивается до уровня

увеличивается до уровня![]() за время нарастания

за время нарастания![]()

![]() .

.

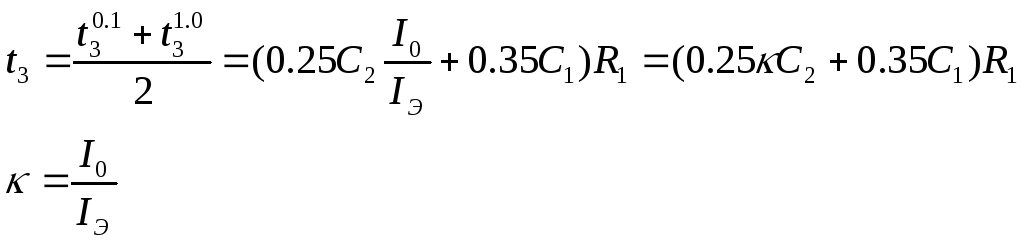

Средняя задержка переключения:

Энергия

переключения:

![]()

2.4. Кмоп

В схемах данного типа используются как n-канальные, так и p-канальные МДП транзисторы. Это позволяет создать логические схемы, практически не потребляющие мощность в статическом режиме. У таких схем потребляемая мощность на низких и средних частотах на 2-3 порядка меньше, чем у ТТЛ схем, а задержка примерно такая же. Эти схемы применяются при наличии ограничений на потребляемую мощность из-за ограниченных энергоресурсов или жестких требований к тепловому режиму. Однако они технологически сложнее и занимают большую площадь на кристалле.