- •Глава 1

- •§ 1. Основные понятия, определения и классификация систем автоматики

- •§ 2. Классификация элементов систем автоматического управления

- •§ 3. Принципы схемного отображения технологических объектов, процессов и систем управления

- •Глава 2 воспринимающие элементы систем автоматики

- •§ 4. Воспринимающие элементы перемещений

- •§ 5. Датчики усилий

- •§ 6. Датчики частоты вращения

- •§ 7. Датчики углов поворота

- •§ 8. Воспринимающие элементы температур

- •§ 9. Воспринимающие элементы давления

- •§ 10. Воспринимающие элементы расхода и уровня

- •Глава 3

- •§ 12. Усилительные элементы

- •§ 13. Вычислительные и логические элементы

- •§ 14. Исполнительные устройства с электродвигателями

- •§ 15. Исполнительные механизмы с электромагнитными

- •§ 16. Пневматические и гидравлические исполнительные механизмы

- •§ 17. Регулирующие органы и их характеристики

- •Глава 4 системы автоматического контроля

- •§ 18. Основные понятия об измерениях и средствах измерений

- •§ 19. Структура и назначение систем контроля

- •§ 20. Измерительные схемы и вторичные приборы

- •§ 21. Преобразование сигналов и системы передачи показаний на расстояние

- •§ 22. Автоматический учет сырья

- •§ 23. Автоматический контроль линейных размеров

- •§ 24. Автоматический контроль качества поверхности

- •§ 25. Автоматический контроль температуры

- •3. Приборы для измерения температуры табл

- •§ 26. Автоматический контроль уровня

- •§ 27. Автоматический контроль влажности

- •§ 28. Автоматический контроль расхода и давления

- •§ 29. Автоматический контроль работы оборудования

- •§ 30. Информационно-измерительные системы

- •Глава 5

- •§ 32. Структурные схемы и их преобразование

- •§ 33. Классификация звеньев по динамическим свойствам

- •§ 34. Характеристики автоматических систем управления

- •§ 35. Инженерные методы расчета и выбора регуляторов

- •§ 36. Элементы построения оптимальных систем управления

- •Глава 6

- •§ 37. Основные понятия и определения

- •§ 38. Основные формализованные языки описания логических систем управления

- •§ 39. Синтез однотактных систем логического управления

- •6. Таблица состояний

- •Глава 7

- •§ 41.ГПреимущества автоматизированных производств

- •§ 42. Оптимизационная математическая модель производства

- •§ 43. Производительность автоматизированного оборудования деревообрабатывающих производств

- •§ 44. Влияние надежности на эффективность автоматизации деревообрабатывающих производств

- •Глава 8

- •§ 45. Характеристика производственных процессов и производств

- •§ 48. Регулирование потока и запаса материала

- •§ 49. Технологические основы управления дискретными производственными процессами

- •Глава 9

- •§ 50. Взаимосвязь параметров при механической обработке древесины

- •§ 51. Системы автоматического управления режимами обработки деталей

- •§ 52. Системы автоматической стабилизации частоты вращения исполнительных двигателей

- •§ 53. Особенности динамики систем стабилизации частоты вращения (режимов обработки)

- •§ 54. Оптимизация динамических свойств автоматических систем управления

- •Глава 10

- •§ 55. Типовые блокировочные связи в системах управления

- •7. Основные виды межузловых связей

- •§ 56. Системы управления станками пиления древесины

- •§ 57. Системы управления станками строгальной и фрезерной групп

- •§ 58. Системы управления шипорезными, сверлильными, долбежными и лущильными станками

- •§ 59. Системы управления автоматами на базе механических программоносителей

- •§ 60. Системы программного управления

- •§ 61. Самонастраивающиеся системы управления

- •§ 62. Микропроцессоры и микроэвм в системах управления

- •9. Символьное обозначение команд

- •§ 63. Основные сведения о манипуляторах, роботах и системах управления ими

- •Глава 11

- •§ 64. Классификация станочных линий

- •§ 65. Структура автоматических линий

- •§ 66. Эффективность функционирования автоматических

- •§ 67. Линии раскроя плит

- •§ 68. Линии облицовывания плит

- •§ 69. Линии брусковых деталей

- •§ 70. Линии повторной обработки щитовых деталей

- •§ 71. Линии отделки

- •§ 72. Линии сортировки

- •Глава 12

- •§ 73. Управление загрузчиками автоматических

- •§ 74. Схемы управления разгрузчиками автоматических линий

- •§ 75. Транспортно-ориентирующие устройства автоматических линий и системы управления ими

- •§ 76. Устройства автоматического позиционирования

- •Глава 13

- •§ 77. Характеристика складов деталей и комплектующих изделий

- •§ 78. Системы управления складами

- •§ 79. Автоматизация транспортных работ

- •Глава 14

- •§ 80. Управление процессами сушки в лесосушильных камерах

- •§ 81. Управление процессом сушки в конвейерных сушилках

- •§ 82. Управление процессом сушки в барабанных сушилках

- •§ 83. Управление режимом горячего прессования

- •§ 84. Управление процессами пропарки древесины

§ 13. Вычислительные и логические элементы

Разнообразие задач управления предопределяет необходимость использования в системах различных классов вычислительных и логических элементов автоматики.

Все вычислительные счетно-решающие устройства разделяются на аналоговые (непрерывного действия) и цифровые (дискретного действия).

Аналоговые вычислительные устройства. В этих устройствах все математические величины, участвующие в решении задачи, представлены в некотором масштабе непрерывно изменяющимися физическими величинами: перемещениями, углами поворота, напряжениями, токами и др. Устройства этого типа являются физическими системами (механические, электрические и др.), в которых протекают процессы, описываемые уравнениями, подобными уравнениям задачи, подлежащей решению. Таким образом, аналоговые вычислительные устройства являются математическими мо-

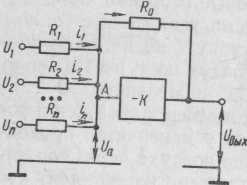

При

большом К

последний

член в уравнении (2) стремится к нулю.

Тогда Uвых

будет связано с UBX

следующей

зависимостью

Широкое распространение получили электронные моделирующие устройства. Это объясняется, с одной стороны, пригодностью одних и тех же математических уравнений для описания объектов и явлений различной физической природы, с другой — тем, что этот вид аналоговых устройств удобен в управлении, компактен и обладает гибкой структурой.

Электронные устройства обеспечивают решение обыкновенных дифференциальных уравнений любого порядка. В состав этих устройств входят следующие блоки: интегрирующие, суммирующие, множительные; осуществляющие масштабное преобразование; функциональные для образования нелинейных функций и ряд вспомогательных блоков, обеспечивающих возможность наблюдения и регистрации решения и управления устройством.

Рис. 25. Структурная схема

операционного суммирующего

усилителя

получим

![]() =i0

=i0

Если в схеме суммирующего усилителя вместо Ro включить конденсатор, то получится интегрирующий усилитель, причем при наличии у него нескольких входов происходит интегрирование суммы. Если в схеме суммирующего усилителя вместо сопротивлений Rj включить конденсаторы, то получим дифференцирующий усилитель.

Соединяя определенным образом различные блоки аналоговых вычислительных устройств, можно получать различные электронные модели, довольно точно описывающие явления, протекающие в технологических объектах.

Вычислительные устройства дискретного действия. В них все математические величины представляют в виде дискретных значений. Вычисление заключается в последовательном выполнении арифметических операций. В устройствах этого типа широко применяют логические элементы, триггеры, регистры, счетчики, дешифраторы и т. д.

Для решения сложных задач управления технологическими процессами в системах автоматики используют различные логические элементы. К логическим элементам относятся схемы, реализующие основные логические функции — И, ИЛИ и НЕ. Поскольку любая сложная логическая функция может быть выражена через элементарные функции И, ИЛИ и НЕ, система логических элементов И, ИЛИ и НЕ называется функционально полной. Иногда в качестве типовых используют и более сложные элементы, реализующие логические функции И—НЕ, ИЛИ—НЕ и др., позволяющие строить более сложные комбинационные схемы для управления технологическими объектами.

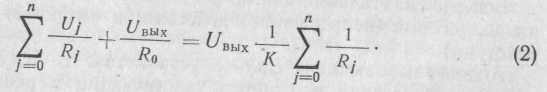

К логическим элементам, выполняющим основные логические функции, относятся схемы НЕ, И (схема совпадения) и ИЛИ (схема собирательная).

С помощью схемы НЕ реализуется логическая функция НЕ (отрицание). Эта схема выполняется на активных элементах — реле, транзисторах и т. д. На рис. 26, а показана схема НЕ, выполненная на транзисторе: положительный сигнал на ее выходе (коллекторе транзистора) будет только при отрицательном сигнале на ее входе.

С помощью собирательной схемы реализуется функция ИЛИ (дизъюнкция). Эта схема показана на рис. 26, д. Сигнал на выходе схемы появится только тогда, когда есть сигнал- хотя бы на одном из входов.

Триггер представляет собой устройство, с помощью которого можно записывать, хранить и считать двоичную информацию. Триггер имеет два устойчивых состояния равновесия. Одному из этих состояний приписывается значение 1, а другому — 0. Состояние триггера распознается по его выходному сигналу. Под влиянием входного сигнала триггер скачкообразно переходит из одного устойчивого состояния в другое, при этом скачкообразно изменяется уровень напряжения его выходного сигнала.

Рис. 26. Логические элементы автоматики: схема НЕ (а), ее условное обозначение (б); схема И (в), ее условное обозначение (г); схема ИЛИ (д), ее условное обозначение (e)

Для

удобства использования в схемах

вычислительных устройств

триггеры обычно имеют два выхода: прямой

Q

(называемый также

«выход 1») и инверсный

![]() («выход

0»). В единичном состоянии

триггера на выходе Q

высокий

уровень сигнала, а в нулевом — низкий.

На выходе

—

наоборот.

(«выход

0»). В единичном состоянии

триггера на выходе Q

высокий

уровень сигнала, а в нулевом — низкий.

На выходе

—

наоборот.

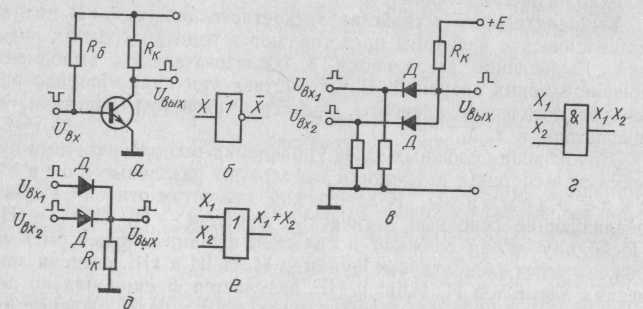

Простейшим триггером является асинхронный RS-триггер, выполненный на двух логических элементах ИЛИ—НЕ. Логическая структура и его условное обозначение приведены на рис. 27, а, б.

Такой триггер образован из двух комбинационных схем ИЛИ— НЕ, соединенных таким образом, что возникают положительные обратные связи, благодаря которым в устойчивом состоянии выходной транзистор одной схемы ИЛИ—НЕ закрыт, а другой открыт.

Полученный таким образом триггер имеет два входа: S — установки триггера в 1 и R — установки триггера в 0.

Рассмотрим прежде всего воздействие на такой триггер комбинации сигналов S = 1, R = 1 и S = 0, R = 0.

Сочетание S = l, R = 1 является запрещенным, так как при нем на обоих выходах триггера устанавливаются логические 0 и после снятия входных сигналов состояние его непредсказуемо.

Для элемента ИЛИ—НЕ логический 0 является пассивным сигналом, с поступлением его на вход состояние выхода элемента не изменяется. Поэтому комбинация S = 0, R = 0 не изменяет состояние триггера.

Логическая 1 для элемента ИЛИ—НЕ является активным сигналом: наличие ее на входе однозначно определяет на выходе логический 0 вне зависимости от сигнала на другом входе. Отсюда

Рис. 27. Функциональные схемы триггеров: асинхронного .RS-триггера (а),

его условное обозначение (б); синхронного RS-триггера (б); его условное

обозначение (г); .JK-триггера (д), его условное обозначение (е)

следует, что переключающим сигналом для рассматриваемого триггера является логическая 1, а также то, что вход S (установка триггера в состояние Q = 1) должен быть связан с элементом, выход которого принят за (см. рис. 27, а).

Для переключения триггера в состояние Q = 1 на его входы следует подать комбинацию S=1, R = 0, а для переключения в состояние Q = 0 — S = 0, R = 1.

Пусть триггер находится в состоянии 0 (Q = 0, = 1), а на его входах действуют сигналы S = 0, R = 0. Для переключения его в состояние Q = 1 подадим на входы комбинацию S = 1, R = 0. Тогда на выходе элемента Э2 установится логический 0, на входах элемента Э1 будут одновременно действовать логические 0 и на выходе Q установится логическая 1 — триггер переключается в новое состояние (Q = 1, = 0). Для его переключения из этого состояния на входы должна поступить комбинация S = 0, R = 1. После этого на выходе Q будет логический 0, на входах элемента Э2 одновременно окажутся логические 0 и его выход примет потенциал, соответствующий = 1 — триггер переключается в состояние Q = 0, = 1.

Часто необходимо, чтобы в вычислительных устройствах триггер реагировал на входные сигналы только в определенные моменты времени. Эти моменты обычно задаются с помощью дополнительного — входного — сигнала синхронизации С. На рис. 27, в, г приведены схема и условное обозначение такого синхронного RS-триггера. Она содержит асинхронный RS-триггер Т с прямыми входами и две схемы совпадения. Последние передают переключающую логическую 1 с информационного S- или S-входа на соответствующие входы Т только при наличии на синхронизирующем входе С логической 1. При С = 0 информация с S- и R-входов на триггер не передается.

Распространенным типом триггера в системах интегральных логических элементов является универсальный JK-триггер, схема и условное обозначение которого показаны на рис. 27, д, е. У рассматриваемого триггера имеются входы R и S несинхронизируемой установки, с помощью которых при С = 0 триггер может быть установлен в состояние 1 путем подачи R = 1 и S = 0 или в состояние 0 путем подачи R = 0 и S = 1. При подаче сигналов R = S = 1, не меняющих состояние схемы, работа триггера осуществляется под воздействием синхронизирующих сигналов С =1. Входы J и К соответствуют входам S и R RS-триггера, это означает, что сигнал 1 на входе / устанавливает триггер в состояние 1, а сигнал 1 на входе K устанавливает его в состояние 0 независимо от предыдущего состояния. Однако в отличие от RS-триг-гера в JK-триггере сигналы одновременно могут прийти на входы J и К. При этом состояние триггера изменится на противоположное, т. е. при J = К схема ведет себя как триггер со счетным входом. Регистром называется функциональное устройство, предназначенное для приема и запоминания двоичных чисел, а также для некоторых их логических преобразований.

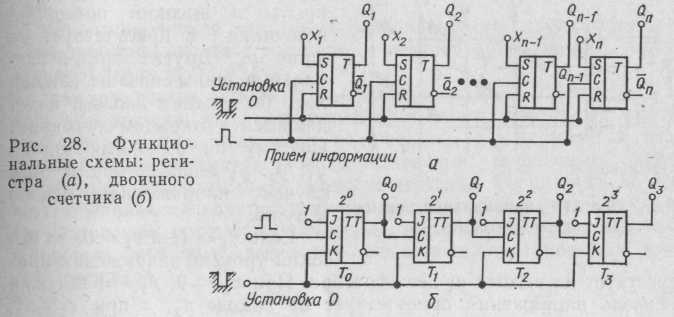

Параллельный регистр выполняет функции записи и хранения параллельного двоичного кода. Для построения такого регистра могут быть использованы ^5-триггеры. На рис. 28, а приведена функциональная схема параллельного регистра.

Параллельный двоичный код подается на входы х1—хп триггеров. Запись производится положительными импульсами, подаваемыми на входы С триггеров. Код снимается с выходов Q2—Qn. Для установки регистра в 0 используют входы R-триггеров.

В этой схеме запись информации в регистр синхронизируется по входу С и происходит только в момент подачи на вход С положительного импульса. Работой регистра управляют две шины: установки нуля и приема информации. Прежде чем записать информацию в регистр, необходимо подать управляющий сигнал на шину установки 0, т. е. все триггеры регистра установить в состояние 0. Для приема информации в регистр необходимо подать управляющий синхронизирующий сигнал на шину приема и одновременно по информационным цепям, соединенным с единичными установочными входами триггеров, подать код записываемого числа в регистр.

Счетчик предназначен для счета поступающих на его вход импульсов, в интервале между которыми он должен хранить информацию об их числе. Поэтому счетчик состоит из запоминающих ячеек — триггеров. Ячейки счетчика соединяют таким образом, чтобы каждому числу импульсу соответствовали единичные состояния определенных ячеек. При этом совокупность единиц и нулей на выходах п ячеек счетчика представляет собой n-разрядное двоичное число, которое однозначно определяет число прошедших на входе импульсов. Поэтому ячейки счетчика называют его разрядами.

На рис. 28, б представлена схема четырехразрядного двоичного счетчика прямого счета с цепями последовательного переноса и импульсным входом. Входные импульсы положительной полярности подаются на счетный вход С триггера младшего разряда счетчика То. Перед началом счета сигнал установки нуля устанавливает в состояние 0 все триггеры счетчика. По первому входному импульсу триггер То переключается в состояние 1 и код в счетчике принимает значение х = 0001. Это значение кода сохраяется до прихода следующего импульса. Под воздействием второго сигнала триггер То переходит в состояние 0. При переходе триггера То из единичного состояния в нулевое с прямого выхода триггера То образуется положительный сигнал переноса (импульс), поступающий на счетный вход триггера Т1, который установит этот триггер в состояние 1. Код счетчика принимает значение х = 0010 и т. д.

Максимальное число, которое может быть зафиксировано в двоичном счетчике, определяется по формуле N =2n—1, где п— число разрядов счетчика.

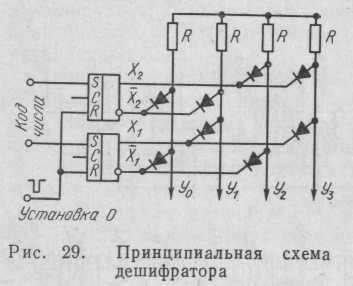

Дешифратором называется логическая схема, преобразующая двоичный код числа, поступающего на его входы, в управляющий сигнал только на одном из его выходов. Другими словами, дешифратор представляет собой совокупность схем совпадений, формирующих управляющий сигнал на одном из выходов, в то время как на остальных выходах сигналы отсутствуют.

Принципиальная схема дешифратора с логическими элементами совпадения на диодах на два входа показана на рис. 29. Горизонтальные и вертикальные шины соединяются в определенных местах диодами, которые образуют сетку (матрицу) дешифратора. Резистор и два диода, подключенные к вертикальному проводу, образуют логический элемент И. Таких схем в сетке — четыре.

Если x1=1, а х2 = 0, то высокий уровень напряжения присутствует на выходе y1 дешифратора. При x1= 0, х2 = 1 высокий уровень напряжения присутствует на выходе y2, а при x1 = 1, х2 = 1 на выходе у3.