- •1. Освоить практически возможности алгоритмов перевода чисел с использованием различных систем счисления. 5

- •2. Научиться применять способы выполнения арифметических операций с применением машинных кодов чисел. 5

- •3. Приобрести навыки практической работы с информацией во внутримашинном представлении. 5

- •1. Закрепление теоретических знаний по теме занятия. 106

- •Пз№1. Выполнение арифметических операций над числами в эвм Цель занятия:

- •Освоить практически возможности алгоритмов перевода чисел с использованием различных систем счисления.

- •Научиться применять способы выполнения арифметических операций с применением машинных кодов чисел.

- •Приобрести навыки практической работы с информацией во внутримашинном представлении. Теоретические сведения

- •Числа в системах счисления

- •Частные правила перевода

- •Арифметические действия над числами

- •Машинные коды чисел

- •Операции над машинными кодами чисел

- •Задания для работы на занятии:

- •Контрольные вопросы

- •Задание на самоподготовку:

- •Список литературы:

- •1.Освоить практически различные способы минимизации логических функций.

- •2.Научиться применять различные способы решения задач по минимизации логических функций.

- •3.Приобрести навыки практической работы по использованию различных способов минимизации логических функций.

- •Расчетный метод

- •Табличный метод

- •Задание для работы на занятии

- •Законы алгебры логики, следствия из них

- •Свойства элементарных функций.

- •Логические элементы

- •Синтез и анализ логических схем без памяти Синтез логических схем без памяти

- •Выводы:

- •1. Закрепление теоретических знаний по теме занятия;

- •2. Приобрести навыки анализа различных способов представления информации в эвм;

- •3. Совершенствование практических навыков оценки характеристик эвм.

- •Отображение чисел в разрядной сетке эвм.

- •Представление других видов информации

- •Методические рекомендации по подготовке к занятию

- •Задания для работы на занятии:

- •Разрядная функциональная группа

- •Озу типа 2d

- •Алгоритм функционирования озу типа 2d Выполнение операции "Запись";

- •Выполнение операции "Считывание";

- •Озу типа 3d

- •Постоянные зу

- •Определение основных параметров зу

- •Задание для работы на занятии:

- •Задание на самоподготовку

- •Контрольные вопросы

- •Литература

- •Пз №6. Составление алгоритмов и микропрограмм работы алу Цель занятия:

- •Краткие теоретические сведения

- •Запросы прерывания

- •Структура арифметико – логического устройства

- •Алгоритм работы алу при сложении n двоичных чисел с фиксированной запятой в дополнительном коде

- •Алгоритм работы алу при умножении чисел с фиксированной запятой

- •Задание для работы на занятии:

- •Вопросы для самоконтроля:

- •Задание на самоподготовку:

- •Литература:

- •Пз №7. Составление алгоритмов и микропрограмм работы устройства управления Цель занятия:

- •Краткие теоретические сведения об уу цвм

- •Алгоритм работы микропрограммного уу при выполнении операций сложения и умножения.

- •Методические рекомендации:

- •Задание для работы на занятии:

- •Задание для работы на самоподготовке:

- •Вопросы для самоконтроля:

- •Литература:

- •Пз №8. Разработка модулей памяти на бис

- •Закрепление теоретических знаний по теме занятия.

- •Краткие теоретические сведения о структуре памяти эвм

- •Разработка модулей памяти на бис зу

- •Задание для работы на занятии:

- •Задание на самоподготовку:

- •Контрольные вопросы:

- •Приобретение навыков решения задач, связанных с составлением отдельных микрокоманд (микроинструкций) для мпк к589.

- •. Приобретение навыков решения задач, связанных с разработкой алгоритмов и микропрограмм для мпк к589.

- •Проверка степени усвоения материала практического занятия (выполнение курсантами заданий по вариантам).

- •Методические рекомендации по проведению занятия:

- •Вопросы для контроля и самоконтроля: Проверка степени усвоения лекционного материала (устно) и уровня подготовленности курсантов к занятию (летучка).

- •Вопросы для проведения письменного контроля:

- •Задание на самоподготовку:

- •Литература:

- •Система микроопераций микропроцессора к589

- •Пз №10 решение задач разработки аппаратных средств специализированных вычислительных комплексов. Цель занятия:

- •Задание для работы на занятии.

- •Задача №1

- •Краткий теоретический материал по задаче №1

- •Предварительный выбор типов смпк.

- •Расчет цикла работы об

- •Временные характеристики смпк

- •Расчет надежностных характеристик об и аппаратных затрат для его реализации.

- •Сравнительная оценка характеристик об и окончательный выбор типа смпк и структуры об смп

- •Разработка временной диаграммы функционирования об.

- •Пример решения подзадач 1…5

- •Заданные характеристики об

- •Задача №2

- •Краткий теоретический материал по задаче №2

- •1.Обоснование и выбор структурной схемы.

- •2. Построение функциональной схемы.

- •3.Построение принципиальной схемы

- •Разработка структурной, функциональной и принципиальной схем об смп

- •Методические рекомендации:

- •Контрольные вопросы:

- •Задание на самоподготовку:

- •Список литературы:

- •Режимы работы вс

- •Алгоритмы планирования работы вс в различных режимах

- •Алгоритм планирования вычислительного процесса вс, работающей в режиме однопрограммной пакетной обработки

- •Алгоритм планирования вычислительного процесса вс, работающей в режиме классического мультипрограммирования

- •Задание для работы на занятии:

- •Методические рекомендации:

- •Вопросы для самоконтроля:

- •Расчет основных параметров алу.

- •Определение требуемого быстродействия алу.

- •Определение разрядности алу с фиксированной запятой.

- •Определение разрядности алу с плавающей запятой.

- •Определение характеристик озу

- •Пример определения основных параметров вк

- •Определим структуру и формат команд уу.

- •Регистр команд

- •Регистр базы

- •Определим характеристики озу.

- •Задание для работы на занятии.

- •7. Доложить о результатах расчетов преподавателю, ответить на контрольные вопросы. Методические указания:

- •Контрольные вопросы

- •Список литературы:

Алгоритм работы алу при сложении n двоичных чисел с фиксированной запятой в дополнительном коде

По командам процессора двоичные коды чисел выбираются из ОЗУ и поступают на шину данных (ЩД) в прямых кодах. Предварительно командой «Сброс» производится очистка регистров АЛУ.

АЛУ готовится к приёму операндов. В СчТ заносится N – количество тактов сложения. Операнды, поступающие с ЩД в АЛУ, вступают в операцию сложения в прямом коде, если знаки операндов положительные, если отрицательные – в дополнительном коде.

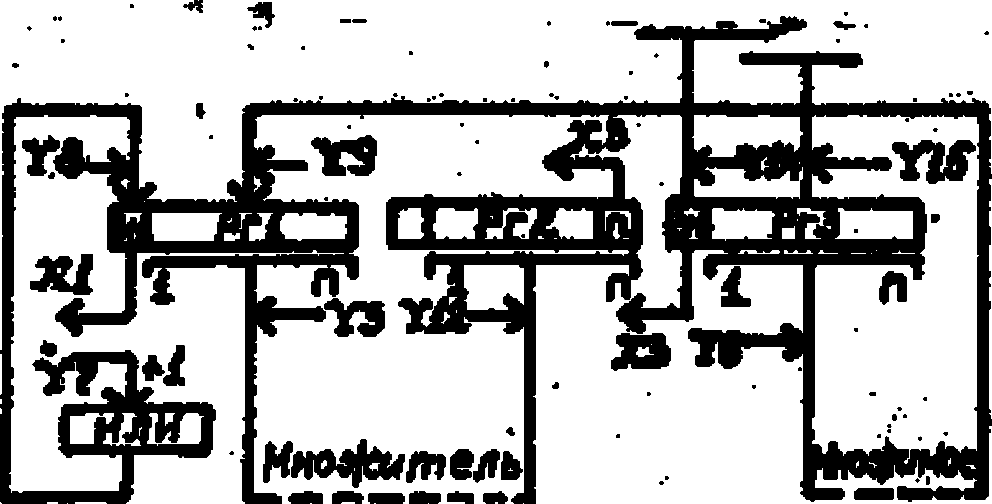

В АЛУ выполняются следующие микрооперации, представленные на рис.6.3.

По управляющему сигналу Y30 осуществляется засылка в СчТ числа тактов т.е. СчТ: = N.

С ШД осуществляется приём операнда в Рг1: Рг1: = ЩД. В УУ выдаётся сигнал Х1 для анализа знака операнда.

Пересылка операнда в Рг3.

Е сли Х1 = 1, то вырабатываются сигналы Y1; Y3; Y16; Y19; Y14;Y15; по которым осуществляется пересылка отрицательного операнда в Рг3 в дополнительном коде, т.е. СМ:=Рг1+1+0; Рг3:=СМ.

При сложении Рг3 закрыт и на левый вход СМ подаётся 0. Если Х1 = 0, то вырабатываются сигналы Y1; Y3; Y14; Y15; по которым осуществляется пересылка положительного операнда в прямом коде:

СМ:=Рг1+0; Рг3:=СМ.

Приём очередного операнда в Рг1 и формирование Х1.

Сложение операндов .

Если Х1=1, то по сигналам Y1; Y3; Y16; Y19; Y5;Y6;Y14; Y15; сложение двух операндов и засылка результата в Рг3:

СМ:=Рг1+1+Рг3; Рг3:=СМ

При выполнении сложения схемами формирования признаков результата и анализа на 0 выдаются сигналы r1:r4. УУ определяет наличие переполнения. При его отсутствии осуществляется переход к следующей микрооперации.

6. Анализ счетчика. СчТ=?

По Y31 выполняется микрооперация Сч:=Сч-1 и формируется сигнал Х4.Если содержимое Сч≠0, т. е. Х4=1, то УУ осуществляет переход к микрооперации приёма операнда (п.4.).

Если содержимое Сч=0, т.е. Х4=0, осуществляется выдача результата на ШД в прямом коде. На этом заканчивается операция сложения операндов.

а) б)

Рис. 6.3. Схемы алгоритмов выполнения операций сложения и умножения в АЛУ с сумматором накапливающего типа.

Алгоритм работы алу при умножении чисел с фиксированной запятой

В зависимости от способа формирования суммы частичных произведений различают несколько методов выполнения умножения и соответствующие им структуры АЛУ. В данном АЛУ используется умножение, начиная с младших разрядов (мл.р.) множителя, со сдвигом суммы частичных произведений вправо и при неподвижном множимом (рис.6.4).

Рг

множителя (Рг2)

![]()

→ Сумматор

частных произведений

Рг множимого (Рг1)

Рис. 6.4. Схема выполнения умножения

Регистр множителя и сумматор частичных произведений имеют цепи сдвига вправо. Последовательность действий в каждом цикле выполнения умножения определяется младшим разрядом регистра множителя. Этот разряд анализируется УУ. Согласно значению разряда (0 или I) вырабатывается соответствующее управляющее воздействие. Если мл.р. равен I, осуществляется сложение СМ + Рг1, а затем сдвиг частичного произведения на I разряд вправо. Если мл.р. равен 0, то происходит просто сдвиг частичного произведения на I разряд вправо. При сдвиге множителя вправо старшие разряды Рг2 освобождаются и на их место поступают младшие разряды, вытесняемые при сдвиге из СМ. После выполнения умножения старшие разряды произведения находятся в РгЗ (выполняющего роль Pr сумматора, где накапливаются частичные произведения), младшие – в Рг2.

Для выполнения умножения чисел, представленных в прямом коде предварительно выполняются операции пересылки операндов. При этом операнды анализируются на 0. При равенстве нулю хотя бы одного сомножителя умножение не производится, а произведению присваивается нулевое значение.

В АЛУ при умножении выполняются следующие микрооперации:

I. В РгЗ засылается множимое, в Рг1 - множитель (рис. 6.5) Производится анализ их знаковых разрядов. Если X1=Х2, то по сигналу Y8; Рг [ Зн] : = 0; Если X1 не равно X2,то по Y7;Y8; Рг1 [Зн]: = 1; В Рг1 [ Зн] - хранится знак произведения.

Рис. 6.5. Схема пересылок в АЛУ при умножении

Засылка значащих разрядов множителя в Рг2: по Y3; Y12; Рг2 [ I -n]: = Рг1 [I - n].

Засылка значащих разрядов множимого в Рг1: по Y6; Y9;Pr1[1-n]: = РгЗ [ I - n] :

4. Установка начального значения суммы частичных произведений: по Y14; Y15; РгЗ: = 0.

5. Засылка в счетчик тактов числа циклов умножения: по Y30; СчТ:=n.

6. Умножение модулей операндов начинается с анализа мл.р. множителя Рг2.

Если Х3= I, то по Y3; Y5; Y6; Y14; Y15; выполняется суммирование: РгЗ: = РгЗ + Рг1 (1-n) ; после чего организуется сдвиг суммы частичных произведений и множителя на I разряд вправо;

по Y4; Y20A ; Y12; Рг2 [ I -n ] : = Рг2 [1 - n] ;

по Y5; Y6; T20; Y14; Y15; РгЗ: = Рг3.

Вытесненный старший разряд [n] суммы частичных произведений при сдвиге из сдвигателя СД [ n + I ] переходит на место младшего разряда в Рг2 по Y11;

Если X3=0, то выполняется только сдвиг суммы частичных произведений и множителя на I разряд вправо.

7. После выполнения цикла умножения производится анализ счетчика:

по Y31; СчТ: = СчТ - I; СчТ = 0 ?

Если СчТ=0, осуществляется очередной цикл умножения. Если СчТ=0, осуществляется переход к следующим микрооперациям.

Результату умножения присваивается знак: по Y1;Y14; РгЗ [Зн] : = Рг1[3н] .В РгЗ хранятся старшие разряды произведения, а в Рг2 -младшие.

9. После выполнения операции умножения содержимое регистров РгЗ и Рг2 выдается на шину данных.