- •Методичні вказівки

- •Для студентів спеціальності 7.092501

- •Методичні вказівки до виконання лабораторних робіт з курсу “Мікропроцесорна техніка“ для студентів спеціальності 7.092501.

- •1.1. Мета роботи

- •1.2. Обладнання та програмне забезпечення

- •1.2.1. Учбово-відлагоджувальний стенд “ev8031/avr”.

- •1.2.2. Персональний комп’ютер.

- •1.3. Теоретичні відомості

- •1.3.3. Технічні характеристики стенда “ev8031”.

- •Послідовний прийомопередавач.

- •Статичний світлодіодний індикатор.

- •Цифроаналоговий перетворювач.

- •Аналого-цифровий перетворювач.

- •Генератори.

- •Виведення цифрової інформації.

- •1.4. Програма роботи

- •1.5. Порядок виконання роботи

- •1.6. Контрольні запитання

- •2.1. Мета роботи

- •2.2. Обладнання та програмне забезпечення

- •2.4. Програма роботи

- •2.5. Порядок виконання роботи

- •2.6. Контрольні запитання

- •3.1. Мета роботи

- •3.2. Теоретичні відомості

- •3.3. Програма роботи

- •3.4. Порядок виконання роботи

- •3.5. Контрольні запитання

- •4.1. Мета роботи

- •4.2. Теоретичні відомості

- •4.3. Програма роботи

- •4.4. Порядок виконання роботи

- •4.5. Контрольні запитання

- •5.1. Мета роботи

- •5.2. Теоретичні відомості

- •5.3. Програма роботи

- •5.4. Порядок виконання лабораторної роботи

- •5.5. Контрольні запитання

- •6.1. Мета роботи

- •6.2. Теоретичні відомості

- •6.3. Програма роботи

- •6.4. Порядок виконання лабораторної роботи

- •6.5. Контрольні запитання

- •7.1. Мета роботи

- •7.2. Теоретичні відомості

- •7.3. Програма роботи

- •7.4. Порядок виконання лабораторної роботи.

- •7.5. Контрольні питання

- •Додаток 4. Інтерфейси.

- •Література

Міністерство освіти України

Національний університет водного господарства і природокористування

Кафедра електротехніки і автоматики

043-

Методичні вказівки

до виконання лабораторних робіт з курсу

“Мікропроцесорна техніка“

Для студентів спеціальності 7.092501

Рівне - 2005

Методичні вказівки до виконання лабораторних робіт з курсу “Мікропроцесорна техніка“ для студентів спеціальності 7.092501.

(С.Ю.Бочаров - Рівне: НУВГП, 2005. - ??с.)

Склав: доцент С.Ю.Бочаров, кафедра електротехніки і автоматики.

Відповідальний за випуск - зав. кафедри електротехніки і автоматики, професор, академік УЕАН Б.О. Баховець

Затверджені методичною комісією

факультету прикладної математики і комп’ютерно-інтегрованих систем.

Протокол №

від “ ” 200 р.

Лабораторна робота №1. Вивчення структури та основ функціонування учбово-відлагоджувального стенда “EV8031/AVR”

1.1. Мета роботи

Вивчити структуру та функціональні можливості учбово-відлагоджувального стенда, провести його тестування.

1.2. Обладнання та програмне забезпечення

1.2.1. Учбово-відлагоджувальний стенд “ev8031/avr”.

1.2.2. Персональний комп’ютер.

1.3. Теоретичні відомості

1.3.1. Загальні відомості та призначення.

Учбово-відлагоджувальний стенд (УВС) “EV8031/AVR” – це програмно-апаратний комплекс, орієнтований на застосування у навчальних цілях, а також як засіб розробки програмного забезпечення для контролерів на базі однокристальної ЕОМ серії MSC-51 а також на базі контролерів архітектури AVR. Стенд містить мікропроцесорний контролер, пам'ять програм, пам'ять даних і різноманітні периферійні пристрої. Він дозволяє відлагоджувати програми, написані мовами Сі та асемблер.

Структура, принципи програмування та зведена таблиця команд базового однокристального мікроконтролера MCS-51 наведені відповідно в додатках 1 та 2.

1.3.2. Схема підключення УВС “EV8031” до ПК. Живлення стенда.

Завантаження програми в учбовий стенд “EV8031” відбувається з персонального комп'ютера по послідовному порту RS-232C. Підключення напруги живлення стенда (+5В) і зв'язок з персональним комп'ютером здійснюється за допомогою одного універсального кабеля із двома роз’ємами (25 й 9 контактів) для з'єднання з одним із com-портів. Крім того, є роз’єм підключення до комп'ютерного блоку живлення й роз’єм для підключення живлення стенда. Роз’єм підключення живлення стенда зручно кріпиться на задній панелі системного блоку комп'ютера й тому не виникає необхідності постійно знімати кришку системного блоку.

Увага!!! Для нормальної роботи стенда, його необхідно підключати тільки до одного з com-портів ПК.

Рис.1.1. Схема підключення стенда EV8031 до ПК і подачі живлення

1.3.3. Технічні характеристики стенда “ev8031”.

Мікроконтролери, що використовуються: AT89C51, AT89C52, AT90S8515 (ATmega8515) (корпус DIP-40);

Пам'ять програм – 16 Кбайт;

Пам'ять даних – 16 Кбайт;

Послідовна EEPROM пам'ять, 256 байт (AT24C02) у стандартній поставці;

Два послідовних канали передачі даних RS232;

Системний інтерфейс (див. додаток №4);

Інтерфейс розширення (16 ліній вихід, 8 ліній вхід/вихід, порт P1 ОЕОМ), дивіться додаток №4;

Пристрій дискретного введення інформації: 2 кнопки;

Клавіатура 4х3;

Статична світлодіодна індикація: 8 світлодіодів;

Статична 4-розрядна семисегментна світлодіодна індикація;

Цифроаналоговий і аналого-цифровий перетворювач (плата розширення);

Генератор з фіксованою частотою генерації – близько 10 кГц, генератор зі змінною частотою генерації від 1 кГц до 50 кГц (плата розширення);

Динамічна 4-розрядна семисегментна світлодіодна індикація (плата розширення);

Знакосинтезуючий світлодіодний індикатор 5x7 1 шт. (плата розширення).

1.3.4. Опис учбово-відлагоджувального стенда.

Принципова електрична схема учбового стенда наведена в додатку 3. Перелік інтегральних мікросхем, що входять до складу стенда перераховані в таблиці 1.1. Деякі елементи розміщені на нижній стороні плати стенда.

Х1 – Системний інтерфейс з повним адресним простором;

Х10 – Інтерфейс розширення для підключення зовнішніх пристроїв з використанням паралельного інтерфейсу;

Х11 – Інтерфейс послідовного порта СОМ1 для зв'язку стенда з ПК;

Х12 – Інтерфейс послідовного порта СОМ2 для зв'язку стенда з іншими пристроями, що мають стандартний порт RS232C;

Х3 – Інтерфейс програмування AVR;

X14, X15 – Перемички підключення пристроїв шини I2C до процесора.

Рис.1.2. Розташування елементів стенда, призначення роз’ємів і перемичок.

Таблиця 1.1. Перелік комплектуючих мікросхем.

№ |

Позначення на схемі |

Позначення (імпортне) |

Короткий опис ІМС |

1 |

DD1 |

AT89C51 |

Однокристальна ЕОМ |

2 |

DD2, DD7, DD9, DD11, DD17 |

74HC573N |

8-розрядний регістр |

3 |

DD3 |

62256 |

Статичний ОЗП 32Кб |

4 |

DD4 |

EPM7128STC100 |

Програмована логічна мікросхема |

5 |

DD6, DD18 |

74HC04 |

6 КМОП інверторів |

6 |

DD8, DD10 |

1489 |

Перетворювач рівня RS-232C |

7 |

DD12 |

ADM485 |

Перетворювач рівня RS-485 |

8 |

DD14 |

AT29C02 |

ЕСПЗП 2 Кбіт |

9 |

DD15 |

DS1621 |

Цифровий темп. датчик |

10 |

DD16 |

DS1302 |

Годинник реального часу |

Окрім зовнішньої оперативної та постійної пам’яті, що розміщені на стенді, є також резидентна пам’ять програм (Flash) мікроконтролера, в яку „зашита” виробником стенда програма-завантажник (не модифікується на лабороторних роботах) і резидентна пам’ять даних (SRAM).

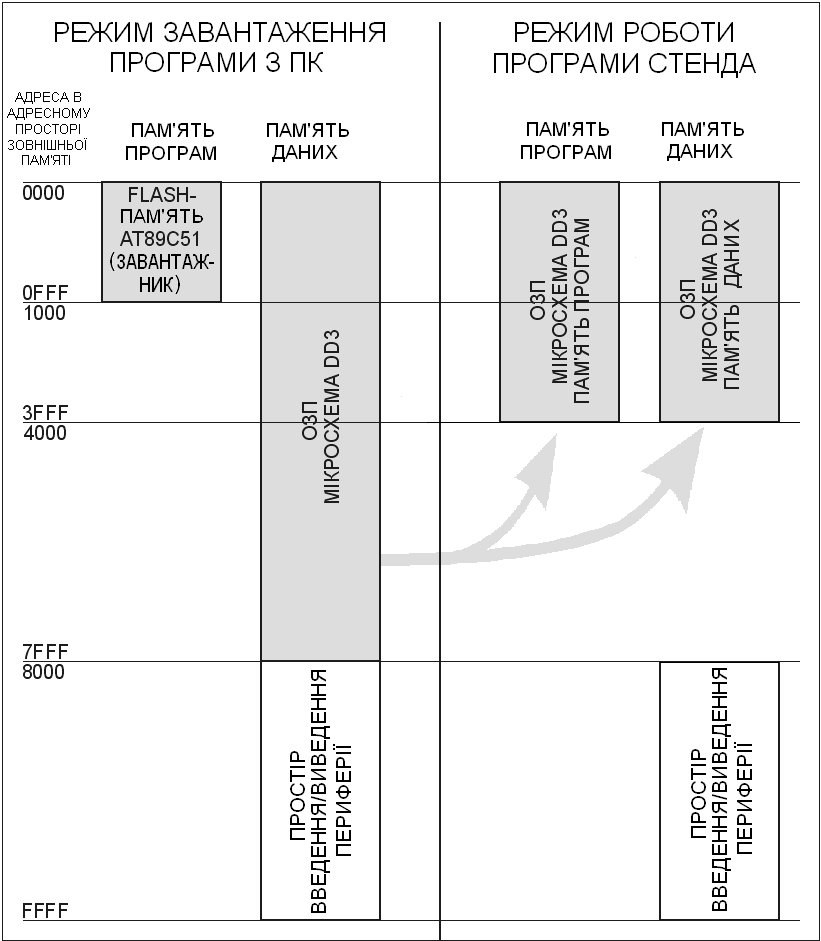

Стенд може працювати в двох режимах (Рис.1.4.):

1. Режим очікування (завантаження програми з ПК). В цьому режимі виконується програма-завантажник, що знаходиться у Flash-пам'яті мікроконтролера AT89C51. Вона проводить ініціалізацію послідовного прийомопередавача ОЕОМ (DD1), перевіряє наявність зовнішньої оперативної пам'яті та відображає її об’єм в кілобітах на статичному індикаторі. У режимі очікування вся зовнішня оперативна пам'ять (32кБ) відображається в адресний простір, як пам'ять даних. В цей режим стенд переходить при формуванні сигналу RESET, в т.ч. при включенні стенда.

2. Режим роботи (програми користувача). При надходженні коду програми користувача з послідовного порту персонального комп'ютера у послідовний порт (роз’єм Х11) стенда, ОЕОМ записує його в зовнішній ОЗП. Після прийняття останнього байта, стенд переходить в режим роботи отриманої програми: завантажник формує сигнал запуску цієї програми за допомогою запису керуючого коду в системний контролер. Зовнішній ОЗП обсягом 32кБ ділиться на дві частини по 16кБ: одна частина з програмою користувача (в даному режимі виступає зовнішньою пам'яттю програм), інша – для даних (зовнішня пам’ять даних). Адресний простір резидентної пам’яті програм перекривається зовнішньою пам'яттю програм, внаслідок чого програма-завантажник „випадає з поля зору” процесора; програмний лічильник скидається і починає виконуватись завантажена програма користувача. Сигнали керування PME, WR, RD, ALE, що формуються процесором і необхідні для звертання до зовнішньої пам'яті, надходять також через системний контролер.

Кнопка SW2 необхідна для формування сигналу скидання на вході RESET контролера, тобто для переводу стенда в режим очікування прийому даних з послідовного порту. Після натиснення на цю кнопку мікроконтролер готовий приймати дані в зовнішню пам’ять.

Кнопка SW1, необхідна для перезапуску завантаженої із ПК програми, що перебуває в зовнішній пам'яті програм. При її натисканні, загоряється світлодіод HL9. При цьому можливий новий запис програми в стенд із персонального комп'ютера. Під час передачі даних з персонального комп'ютера в стенд, комп'ютер на лінії RI послідовного порту формує сигнал, що через системний контролер скидає ОЕОМ, так само як і кнопка SW2.

Рис.1.3. Структурна схема стенда.

Вся логіка стенда реалізована на програмованій логічній мікросхемі EPM7128STC100 (DD4). Цей системний контролер управляє режимами роботи стенда, виробляє керуючі сигнали на ОЗП, регістри-фіксатори, обслуговує статичний світлодіодний індикатор та клавіатуру.

Рис.1.4. Розподіл пам'яті стенда.

Адресація (звернення) мікроконтролера до периферійних пристроїв стенда реалізована як адресація до комірок зовнішньої пам'яті в адресному просторі від 8000h до FFFFh (див. Рис.1.4. і Табл.1.2.). Сигнали вибірки периферійних пристроїв формуються дешифратором адреси всередині мікросхеми системного контролера DD4.

Таблиця 1.2. Карта портів введення/виведення стенда.

Адреса |

Тип циклу |

біт7 |

біт6 |

біт5 |

біт4 |

біт3 |

біт2 |

біт1 |

біт0 |

Ім'я |

Плата розширення |

||||||||||

8000h |

Запис |

|

|

|

PA4 |

PA3 |

PA2 |

PA1 |

PA0 |

PA_REG |

8001h |

Запис |

Регістр даних динамічної індикації |

PB_REG |

|||||||

8002h |

Запис |

PC7 |

PC6 |

PC5 |

PC4 |

PC3 |

PC2 |

PC1 |

PC0 |

PC_REG |

8003h |

Запис |

|

|

|

|

|

TRISC |

|

|

TRIS |

F000h |

Запис |

Регістр даних ЦАП |

|

|||||||

РКІ |

||||||||||

8004h |

Запис |

Регістр команд РК індикатора |

LCD_CMD |

|||||||

8005h |

Запис |

Регістр даних РК індикатора |

LCD_DATA |

|||||||

Послідовний порт і клавіатура |

||||||||||

9000h |

Читання |

CTS |

DSR |

DCD |

RI |

|

|

|

|

US_REG |

9003h |

Читання |

|

|

|

|

KLDN |

KL3 |

KL6 |

KL9 |

|

9005h |

Читання |

|

|

|

|

KL0 |

KL2 |

KL5 |

KL8 |

|

9006h |

Читання |

|

|

|

|

KLUP |

KL1 |

KL4 |

KL7 |

|

C000h |

Запис |

|

|

|

|

DTR |

RTS |

CFG1 |

CFG0 |

UC_REG |

Індикатор і світлодіоди |

||||||||||

A000h |

Запис |

3й і 2й (старші) розряди статичного індикатора |

DISPLAY[0] |

|||||||

A001h |

Запис |

1й і 0й (молодші) розряди статичного індикатора |

DISPLAY[1] |

|||||||

A002h |

Запис |

<зарезервовано> |

DISPLAY[2] |

|||||||

A003h |

Запис |

<зарезервовано> |

DISPLAY[3] |

|||||||

A004h |

Запис |

DP0 |

DP1 |

DP2 |

DP3 |

BL0 |

BL1 |

BL2 |

BL3 |

DC_REG |

A005h |

Запис |

<зарезервовано> |

EDC_REG |

|||||||

A006h |

Запис |

LED0 |

LED1 |

LED2 |

LED3 |

LED4 |

LED5 |

LED6 |

LED7 |

LED_REG |

Керування роботою |

||||||||||

A007h |

Запис |

|

|

|

|

|

|

|

RUN |

SYS_CTL |

|

|

|

|

|

|

|

|

|

|

|