- •5. Дешифраторы.

- •10. Цифровые компараторы

- •8. Сумматоры

- •9. Вычитатели.

- •11. Перемножители

- •17. Разновидности регистров. Параллельные регистры.

- •15. Счётчики.

- •16. Реверсивные счётчики.

- •18. Сдвиговые регистры.

- •19. Реверсивные регистры.

- •20. Запоминающие устройства. Разновидности, характеристики.

- •21. Структуры зу.

- •23. Пзу и ппзу.

- •25. Озу типа fram

- •26. Плис. Общие понятия. Разновидности.

- •27. Программируемые логические матрицы (pla).

- •28. Программируемая матричная логика (pal), базовые матричные кристаллы (ga).

- •29. Программируемые вентильные матрицы (fpga). Программируемые коммутируемые матричные блоки (cpld)

- •Программируемые вентильные матрицы

- •31. Плис типа «система на кристалле (SoC).

- •32. Цап. Общие положения. Погрешности цап.

- •33. Цап с суммирование токов.

- •34. Цап типа r-2r.

- •35. Сегментированные цап.

- •36. Цифровые потенциометры. Цап прямого цифрового синтеза.

- •37. Ацп. Общие положения. Параметры ацп. Погрешности ацп.

- •38. Разновидности ацп. Параллельные ацп.

- •39. Ацп поразрядного уравновешивания.

- •40. Конвейерные ацп.

17. Разновидности регистров. Параллельные регистры.

Регистры – устр-ва, выполняющие ф-ии приема, хранения, передачи и преобразования инф-ии. (самые распростр-ые узлы цифровых устройств) Инф-ия в регистре хр-ся в виде двоичного кода. Регистр предст-ет собой упоряд. послед-ть тр-ров, число кот. соотв-ет числу разрядов в слове. Каждому разряду числа, записанного в регистр, соотв-ет свой разряд регистра, выполн-го на основе D-триггера. Классиф-ся по способу записи инф-ии или кода в регистр:паралл., послед. и паралл.-послед.В паралл. регистры запись числа осущ-ся паралл. кодом, т.е. во все разряды одновременно. Послед. регистры хар-ся послед. записью кода числа, начиная с младшего или старшего разряда, путем сдвига кода тактирующими импульсами. Регистры параллельно-последовательного типа имеют входы как для паралл., так и для послед. записи числа.

По назначению регистры подразделяются на накопительные (регистры памяти, хранения) и сдвигающие.В свою очередь сдвигающие регистры делятся: по способу ввода-вывода инф-ии на параллельные, последовательные и комбинированные;по направлению передачи инф-ии на однонаправленные и реверсивные регистры.

В параллельном регистре цифры кода подаются на D-вход соотве-их тр-ров. Запись осущ-ся при подаче логич. 1 на вход С. Код снимается с выходов Q. Паралл. регистры служат только для хранения инф-ии в виде паралл. двоичного кода и для преобразования прямого кода в обратный и, наоборот.

Послед. регистры, помимо хранения инф-ии, способны преобр-ть послед.код в паралл. и наоборот.

параллельный регистр

-------------------------------------------------------------------------------------------

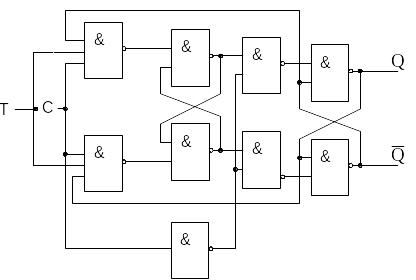

14. D-триггеры. T-триггеры.

Тр-ры—устр-ва,кот. явл-ся эл-ми памяти,сохр. своё сост. при отключ. вх. сигнала,логич. схема с полож. обратной связью, имеющую два устойчивых состояния – единичное и нулевое,обозн-ся соответ-о 1 и 0. В основе любого триггера находится кольцо из двух инверторов.

Т-счетный(общий)вх.Т-тр-р изм-ет свое логич. сост-ие на противополож. по каждому активному сигналу на инф-ом вх. Т. Т-тр-р может строиться как на JK, так и на D-тр-рах. Если на J и K под-ся «1», то JK-тр-р переход. в инверс.сост-ие,это позволяет создать на базе JK-тр-ра Т-тр-р, объединяя входы J и К. Наличие в D-тр-ре динам. С входа позволяет получить на его основе T-тр-р. вход D соед-ся с инверсным выходом, а на вход С подаются счетные импульсы.В рез-те тр-р при каждом счетном импульсе запоминает значение «неQ», то есть будет переключаться в противополож. сост-ие. Хранение инф-ии осущ-ся при подаче на вход С «0» или «1». На выход передается и запом-ся на период повторения синхроимпульсов инф-ия, имеющаяся на входе D перед фронтом импульса на входе С. Изм-ие инф-ии на выходе может происх-ть только во время действия фронта импульса на входе С.

Так как у T-триггера в столбце QS+1 таблицы переходов имеется значение не QS, то структура только двухступенчатая (когда структура одноступенчатая, то это явл генератором).

Tn |

Qn+1 |

1 |

Qn |

0 |

!Qn |

D-триггер запом-ет входную инф-ию при поступлении синхроимпульса. Хранение информации в D-триггерах обеспечивается за счет синхронизации. D-триггеры имеют два входа: информационный D и синхронизации С. В этом триггере сигнал на входе по сигналу синхр-ии записывается и передается на выход. Так инф-ия на выходе остается неизменной до прихода очередного импульса синхр-ии. D-вх. для уст-ки в сост. «0» или в «1».Прием инф-ии по одному вх.D. Тр-р м. снабжен допол. вх. асинхр-ой уст-ки. К561ТМ2 предст-ет собой 2 тр-ра с динам. управ-ем по входам синхр-ии, имеющие входы асинхронной уст-ки R и S . При подаче на вход S «0» и на вход R «1» тр-р уст-ся в единичное состояние (Q = 1). При подаче на вход S «1» и на вход R – «0» тр-р уст-ся в нулевое состояние. При S = R = 1 тр-р работает как D-триггер, повторяя на выходе Q сигнал на входе D при воздействии полож. фронта на входе синхр-ии

Как асинхронный D-триггер не находит применения из-за отсутствия режима хранения информации (Qt+1=Qt).

Cn |

Dn |

Qn+1 |

0 |

0 |

Qn |

0 |

1 |

Qn |

1 |

0 |

0 |

1 |

1 |

1 |

-------------------------------------------------------------------------------------------